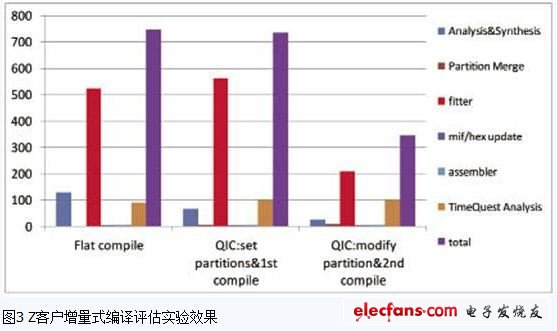

增量编译:使用增量编译满足最后时刻 HDL 变动需求,仅针对已变动逻辑进行布局布线,从而可节省时间。

2020-12-13 10:14:00 4563

4563 一些刚开始接触C语言编译的网友想下载一款C语言编译器来使用,不过,网络上有不少C语言编译器相关的软件,让人很难抉择。

2022-09-05 09:19:42 9241

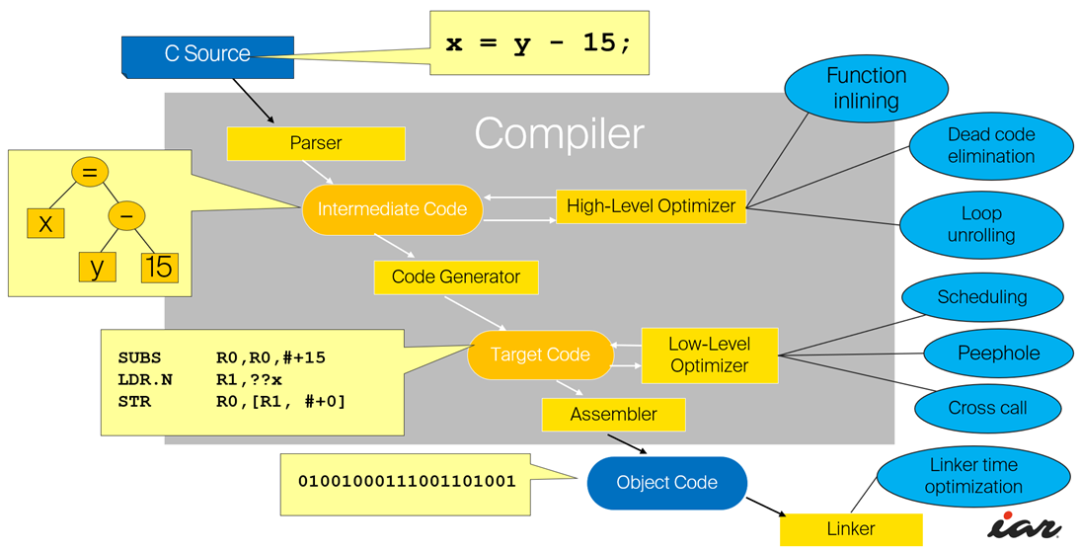

9241 什么是编译器?为什么要有编译器?编译器的作用是什么?编译系统的组成部分有哪些,它们之间的关系是什么?有一句名言说的非常好:了解一件事情最好从它的历史开始。要想对整个编译系统有个全面透彻地理解,我们就必须要先去认真研究它的发展历史。下面我们就来看一下编译系统的发展历史。

2022-09-20 09:09:19 1046

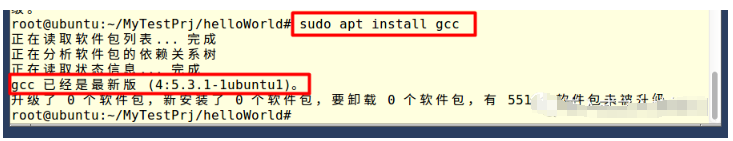

1046 对于习惯了使用windows进行开发的朋友们,如果想要编译C语言,只要要在windows中安装一个可以编译的IDE即可。或者直接自己加载编译的工具链,使用Cmd命令行也可以完成C语言的编译。

2023-01-11 15:50:07 2620

2620

OpenHarmony 有两种编译方式,一种是通过 hb 工具编译,一种是通过 build.sh 脚本编译。本文笔者将提升 build.sh 方式编译速度的方法整理分享给大家。

2023-02-14 09:31:22 1443

1443 本地编译:在当前目标平台下,编译出来的程序,放到当前平台下,就可以运行的。

2023-04-15 11:54:28 2972

2972

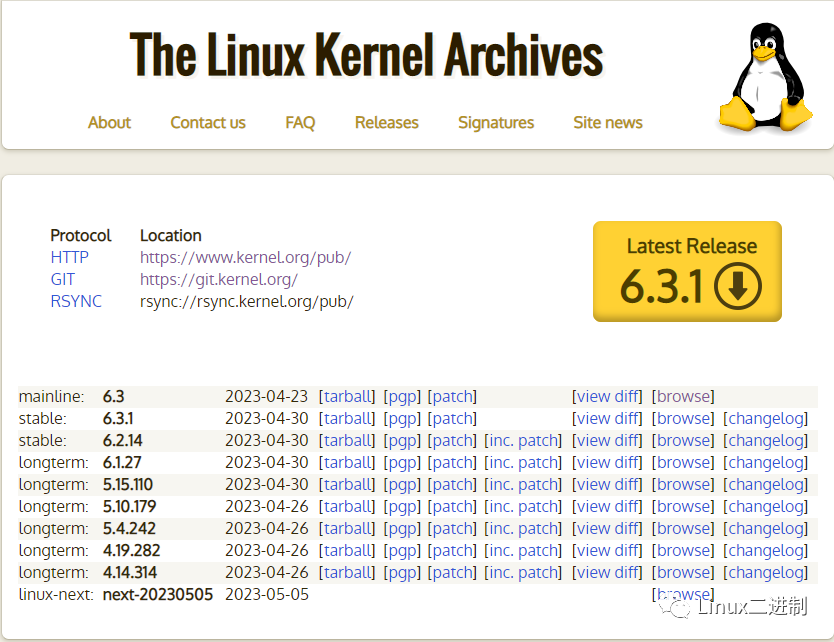

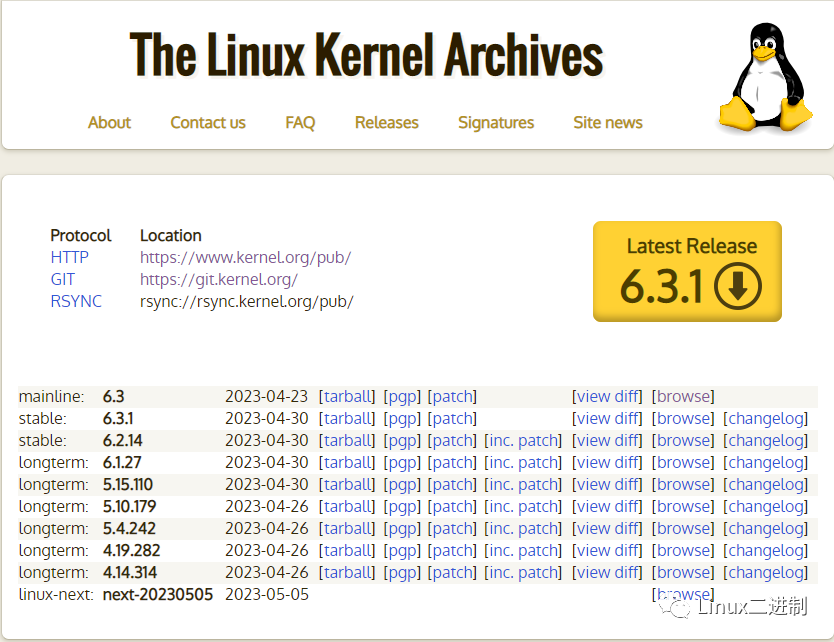

整个Linux内核编译的过程非常简单,但是内核编译需要花费很长的时间。因为Linux内核的代码非常多。当然,如果你的计算机性能强劲,时间会短很多。当你准备好性能强劲的计算机后,让小编带你一步一步的编译Linux内核。

2023-06-07 16:26:27 4728

4728

Linux内核的编译主要过程: 配置、编译、安装 。

2023-08-08 16:02:44 435

435

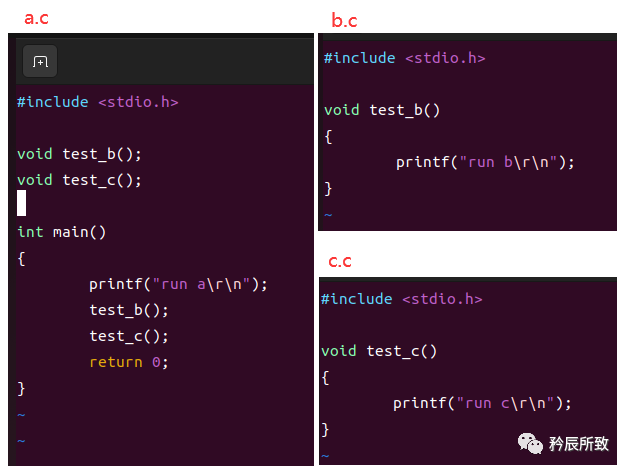

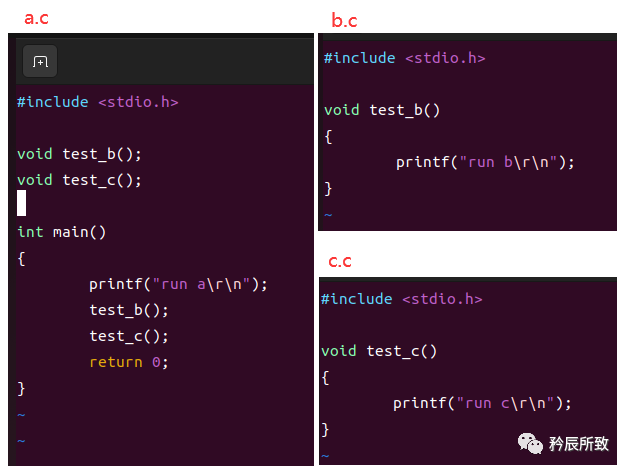

一、Linux 下多文件编译 在上一篇 Linux 下的 C 编程我们知道了 Linux 下的编译器为 GCC ,以及如何使用 GCC 进行编译,在文章我们讲解 GCC 的编译,使用的只使用了

2023-09-11 15:18:37 1000

1000

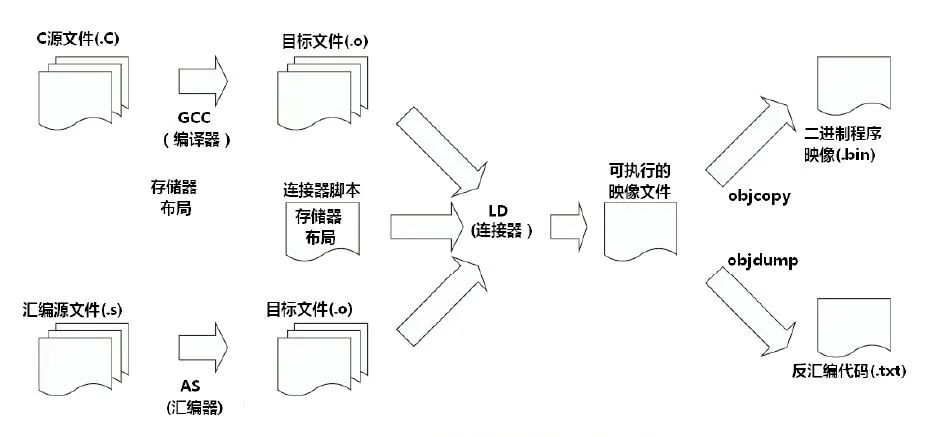

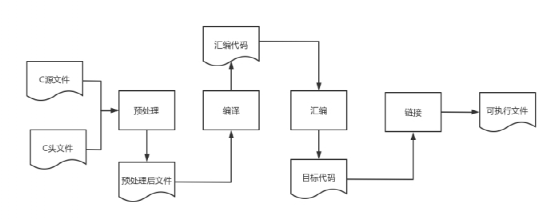

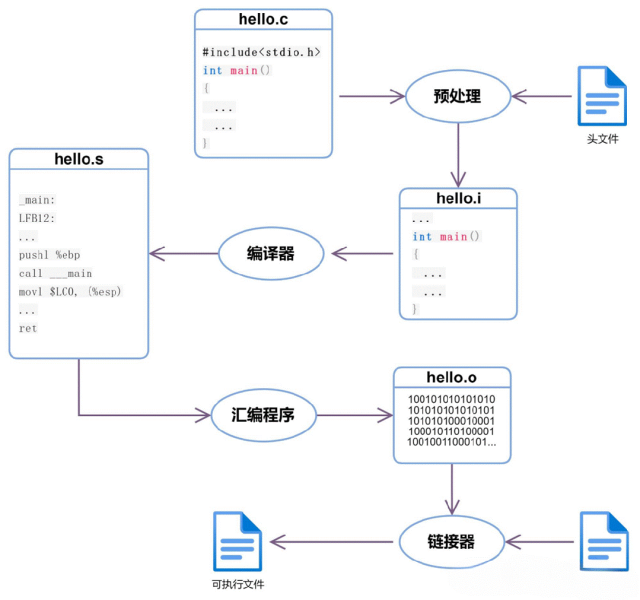

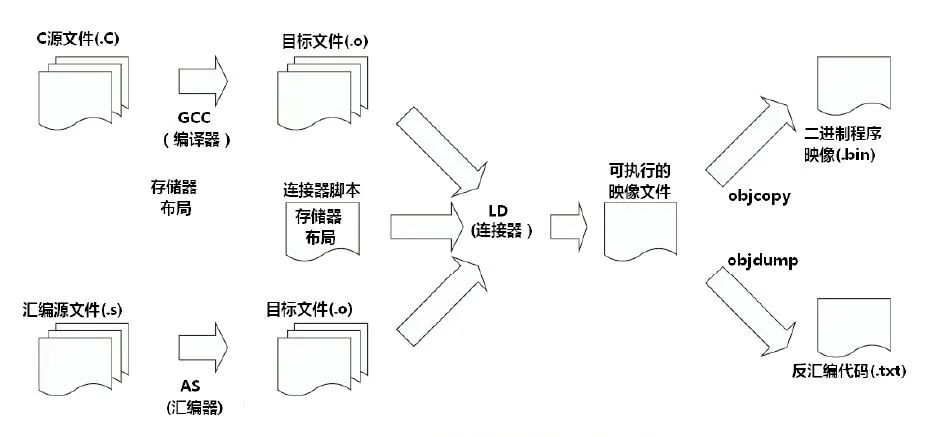

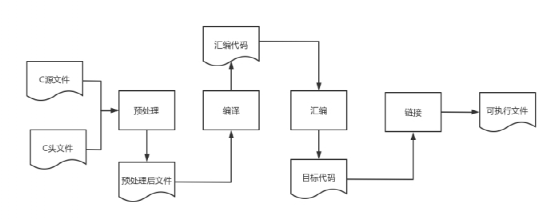

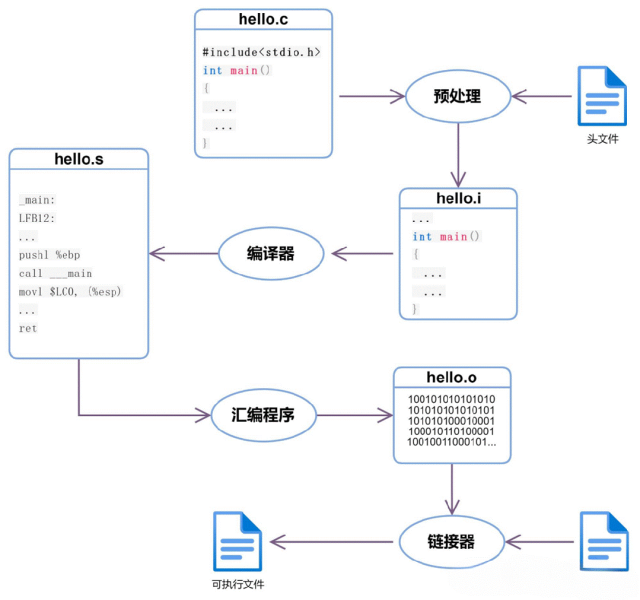

本文讨论了C程序的完整编译过程,分别讲述了预处理、编译、汇编、链接各阶段完成的编译任务。然后通过一个编译实例,探讨了各阶段输出的文件。

2023-11-15 17:14:23 456

456

使用CRIO 9064和C系列模块,写了一个很简单的FPGA VI,编译成功了,但运行VI确报如下错误,网线换成USB线,出现同样的错误,不知何解?

2020-04-17 15:06:15

我刚刚接触NI采集设备,想要编译一个FPGA程序,但是连接本地编译器一直出错,无法编译。我用的是labview2016 32位中文版,驱动都装了,xilinx编译器也是对应的。大神们能否告诉我是为什么?如下图:

2017-09-13 15:33:56

刚刚学习fpga方面的知识,fpga如何测量一个增量式编码器,消除抖动的话是否也是在上升沿和下降沿都进行计数处理,这样的话怎样设定可以保障计数器可以同时在两个always 下进行计数,可以给一下大概的例程最好

2016-01-11 18:27:47

朋友们,xinlinx有没有增量编译的技术,最近做个工程占用了快80%,用了比较多的ip核,每次改一个参数就要重新综合半天,这样调试效率实在太低,我用的是ise13.2,和工具有关系么?

2014-06-14 22:43:59

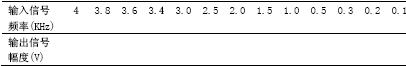

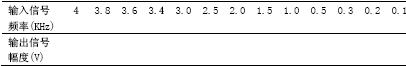

增量调制(ΔM)编译码实验一、实验目的 1、了解语音信号的ΔM编码过程; 2

2009-10-11 08:58:46

labview fpga编译一直出错。在别人建的项目里新建vi代码可编译,自己建的里面打同样代码就不行。里面用了Dma-fifio,fxp的数据类型,labview2015+2015SP1Xilinx14_7进行编译。截图如下:

2016-08-05 19:25:34

` 本帖最后由 YSHL2016 于 2016-9-28 08:44 编辑

在simulink中的matlab function写的增量式编码器仿真模型。模型输入为电机模型输出的机械角度thet

2016-09-28 08:34:22

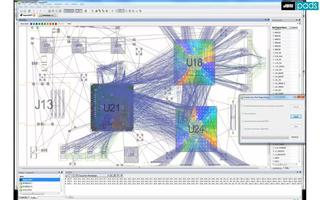

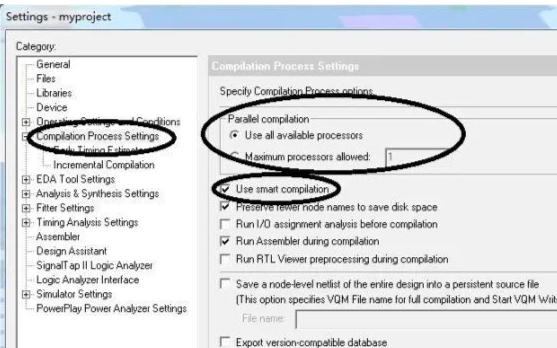

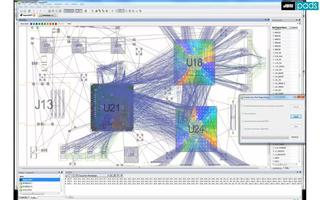

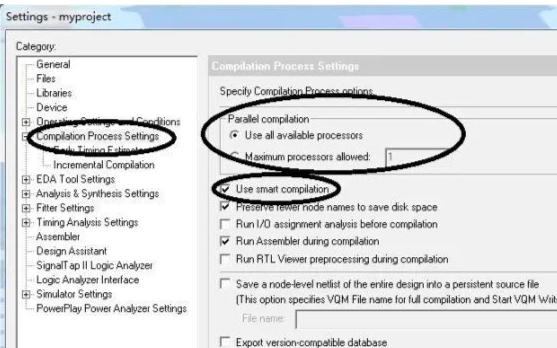

压一压就好了! Altera不能真的压缩时间,但我们能改变“速度”!从数年前的版本开始,Quartus2软件中就整合了一种新技术,或者说一种新的设计流程:增量式编译(Incremental Compilation)。它是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!您,了解它吗?

2019-09-19 08:22:03

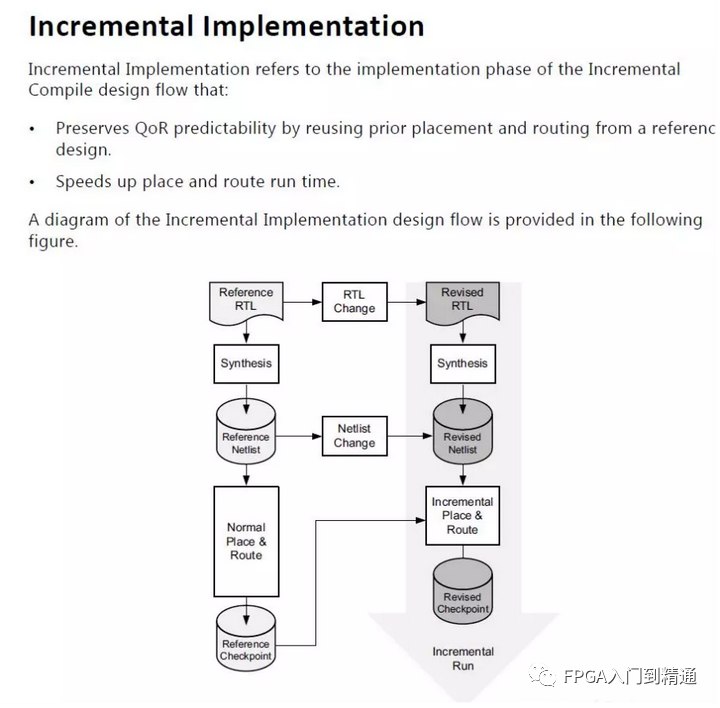

增量实现由哪几个流程构成?增量实现流程有哪几种模式?怎么证明增量编译后,原始设计成功锁定了呢?

2022-02-16 07:54:31

相关EDA软件的性能滞后所带来的开发效率相对降低而苦恼不已,尤其是对大容量FPGA芯片动辄10到20个小时的编译时间可谓怨气冲天。笔者在许多次面对一线的FPGA工程师时,都听到了这样类似的话:要是编译时间能压一压就好了!

2019-11-11 07:03:58

缩短编译时间

2023-10-11 07:54:53

Compilation is too Long Maxplus2使用技巧—减少complier(编译)时间

What you can do for Netlist/Database

2008-09-12 09:52:36 0

0 上EasyGo FPGA Solver中的FPGA Coder解算软件,可以将用户灵活搭建的模型直接下载至FPGA中运行,而不需要进行FPGA的编译,最

2022-05-19 09:16:05

。EasyGo FPGA Solver 的优点在于,能够将Simulink的图形化模型利用解算器软件转化成FPGA执行的代码,而不需要进行FPGA的编译

2022-05-19 09:21:43

编译原理实验指导《编译原理》实验教学大纲一、课程名称:编译原理(Principle of Compiler)二、课程编码:4111204三、课程总学时: 72 学时[理论: 54 学时;实

2009-03-23 18:02:54 56

56 本文利用可编程逻辑的灵活性和Nios 的强大处理能力,将多种编译码模块和微处理器模块集成到一片FPGA 内部,方便地实现了通用编译码器的设计。由于采用了VHDL 语言,使系统具有可移

2009-11-30 14:27:56 22

22 本文针对当前大型软件生成时间过长的问题,在MSBuild 生成引擎的基础上,提出并实现了一种利用集群进行分布式编译的系统,以降低在MSBuild 平台上的产品每次编译所需要的时间

2010-01-15 14:16:20 18

18 GAL编译工具

Atmel提供的GAL编译工具 4.8a版本

2010-04-14 15:42:06 83

83 PCM编译码实验

一、实验目的1. 掌握PCM编译码

2008-10-21 13:35:45 8339

8339

1.GCC编译 2.Make简介 3.常用编译器

2011-04-05 21:26:15 60

60 首先说说编译PC上的QT/E,我起初的时候不知道编译PC上的QT/E编译qpe和交叉编译后的qpe有什么不同,

2011-05-10 10:53:24 2695

2695 本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 CoSy是ACE公司开发的编译器构造框架[1]。它提供共享工具和引擎来构造编译器,编译器开发者只专注于目标机相关代码的开发。CoSy框架生成的编译器具有可扩展性和可移植性。可以根据目

2013-08-19 17:49:10 0

0 了30%,最大达到70%,进一步扩展了在软件效能方面的业界领先优势。软件还包括最新的快速重新编译特性,适用于客户对Altera Stratix® V FPGA设计进行少量源代码改动的情形。采用快速重新编译特性,客户可以重新使用以前的编译结果,从而保持性能,不需要前端设计划分,进一步将编译时间缩短了50%。

2013-11-06 15:15:43 2685

2685 介绍编译原理的基本原理的课件

有需要的朋友下来看看

2015-12-23 14:30:53 0

0 吴鉴鹰总结的Keil 编译常见问题,吴鉴鹰总结的Keil 编译常见问题。

2016-07-22 15:31:13 10

10 Android反编译工具

2016-12-17 15:59:02 21

21 基于FPGA的3B4B编译码电路

2017-02-07 14:58:18 11

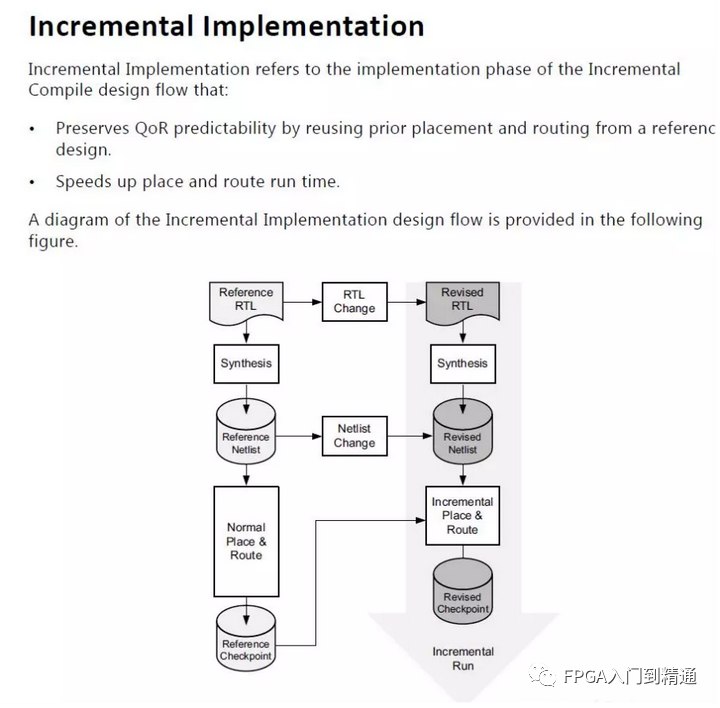

11 Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

2018-07-05 06:06:00 10328

10328 3.3 gcc编译器 GNU CC(简称为gcc)是GNU项目中符合ANSI C标准的编译系统,能够编译用C、C++和Object C等语言编写的程序。gcc不仅功能强大,而且可以编译如C、C++

2017-10-18 13:48:46 0

0 Mocor Smart 编译指导

2017-10-24 10:38:02 5

5 通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 2377

2377

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

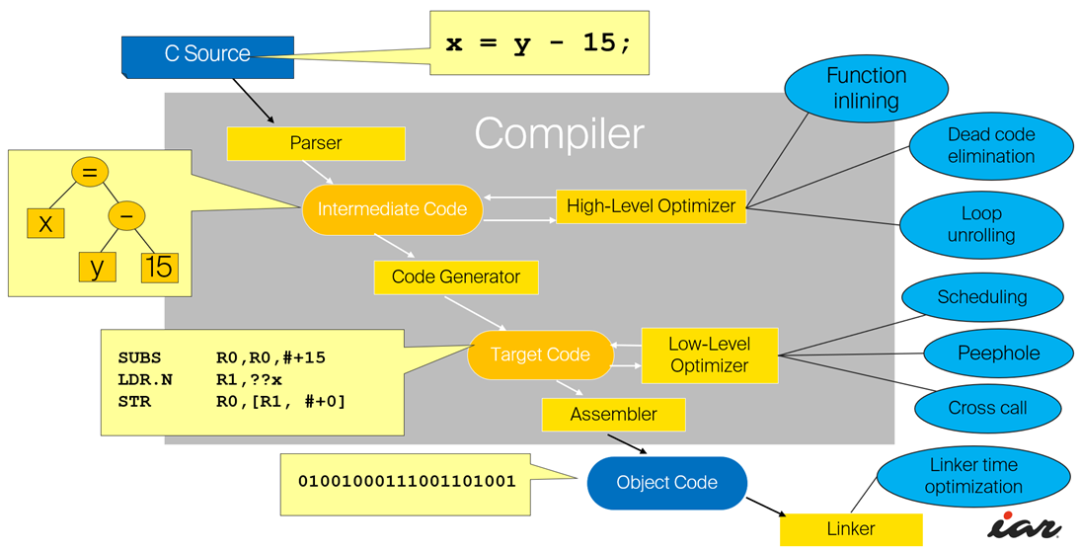

随着计算机的发展,编译器已经发挥着十分重要的作用。本文主要介绍了编译器的种类、编译器的工作原理以及编译器工作的具体操作过程及步骤详解。

2017-12-19 12:54:31 15011

15011 具套装平均快出2倍,保持了FPGA和SoC设计的软件领先优势。 Quartus II软件14.0版支持用户更高效的迅速实现FPGA和SoC设计。最新版包括新的快速重新编译特性,对设计进行小改动后,编译时间缩短了4倍;以及同类最佳的PCI Express (PCIe) IP解决方案,性能达到企业级水平。

2018-02-11 13:37:00 4543

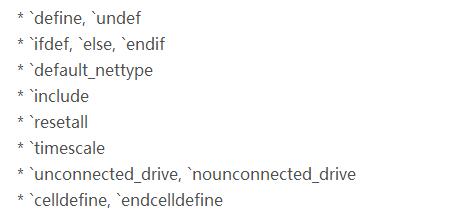

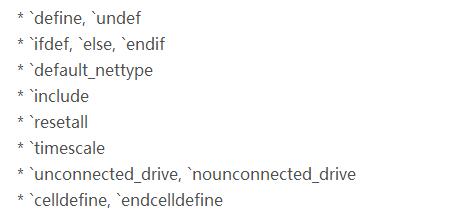

4543 以`(反引号)开始的某些标识符是编译器指令。在Verilog 语言编译时,特定的编译器指令在整个编译过程中有效(编译过程可跨越多个文件),直到遇到其它的不同编译程序指令。

2018-03-23 13:40:40 13585

13585

FPGA到最后自然是规模越来越大,编译时间越来越长。解决问题的方法通常来说应该从工具和设计入手。

2018-08-04 09:16:18 6131

6131 到Bluespec的编译器。这个P4FPGA的工作发表在会议第一天的NetPL workshop上,P4语言与FPGA的结合引起了工业界的重视。因此,本文将分享搭建P4C与P4FPGA联合编译环境的经验

2018-10-02 09:00:01 492

492 目前,FPGA在实时基因组测序计算大显身手,把测序时间从30小时缩短到26分钟,之后基因组测序计算时间将会缩短到10分钟,预计一个全序列基因编译可以在接近实时的时间内完成。

2018-10-09 16:51:35 1802

1802 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:56:00 2512

2512 了解使用Vivado 2016.1中引入的增量编译流程进行调试的好处,以及在使用增量编译实现时添加/删除/修改ILA内核所需的步骤。

2018-11-30 06:19:00 2759

2759

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3340

3340 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 当RTL代码修改较少时,使用增量编译功能可以提高工程的编译速度,Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

2019-01-22 17:27:48 9325

9325

编译预处理是VerilogHDL编译系统的一个组成部分,指编译系统会对一些特殊命令进行预处理,然后将预处理结果和源程序一起在进行通常的编译处理。以”`” (反引号)开始的某些标识符是编译预处理语句

2019-03-26 16:10:41 643

643 编译器对C程序的处理可以明确地分为两步。第一步由预编译器完成。以#开头的预编译指令可能会影响编译器设置或者进行文本替换。注意,预编译器变量(标识符)和正常的C变量是不一样的。预编译完成之后,编译器将不会看到任何预编译指令或标识符。下面介绍常见的预编译指令。

2019-06-05 17:52:00 2

2 在遵循管脚特定的规则和约束的同时,可以在 PCB 上的多个 FPGA 之间自动优化信号管脚分配。减少布线层数,最大限度地减少 PCB 上的交叉数量并缩短总体走线长度,以及减少信号完整性问题,从而提高完成率并缩短 FPGA 的布线时间。

2019-05-14 06:23:00 3276

3276

这是国外一个著名的捣鼓硬件的老外反编译国产掌机代代星的内核并运行在自制的FPGA上的视频,这老外还提供了一份技术文档。

2019-12-26 07:03:00 2046

2046 万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。

2019-07-26 15:56:23 3187

3187

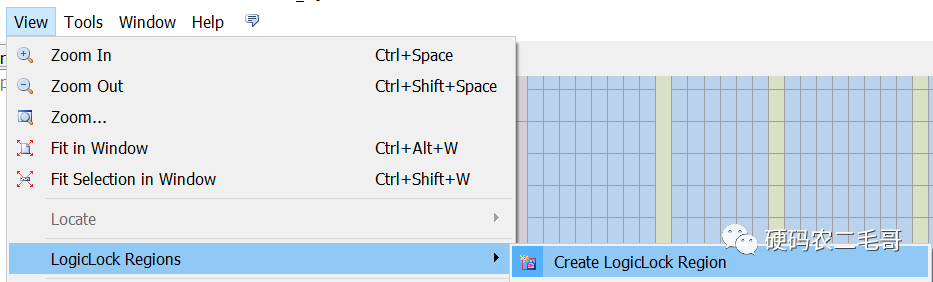

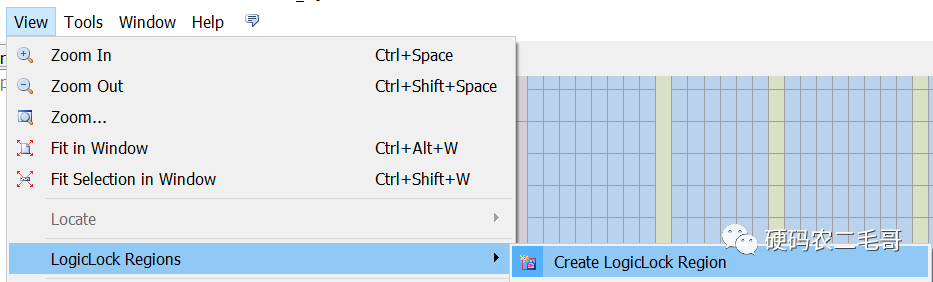

本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改

2019-07-06 10:32:42 6746

6746

既然C编译器是C语言写的,那第一个C编译器是怎样来的?

2020-02-25 15:47:44 2756

2756 如果你使用的是集成开发环境,那么你点击编译按钮就可生成可执行文件,然后点击运行即可运行。那么,你知道从源代码到可执行文件经历了哪些过程吗。仅仅是编译?

2020-06-24 11:49:01 2843

2843 用的CubeMX版本是4.20.0如下图,用的Keil5编译代码,编译结果0 Error(s),0 Warning(s)。

2020-10-10 10:32:36 3872

3872

由于早期的 Lisp 编译器生成的代码效率普遍低下,成为了 Lisp 失败的主要原因之一。而现在的高性能 Lisp 编译器(比

2021-03-30 10:45:29 1840

1840 对于减少Quartus II的编译时间的方法,可从三个角度进行考虑。

2021-05-18 10:27:25 4046

4046

LLVM是以C十十编写的架构编译器的框架系统,支持多后端和交叉编译,用于优化程序的编译时间、链接时间、运行时间和空闲时间。节点融合是一种简单有效的优化方法,其基本思想为将多个节点优化为一个高效的融合

2021-06-15 14:29:30 19

19 关于增量编译所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线...

2021-12-20 19:11:57 6

6 预编译就是处理以#开头的指令,比如赋值#include包含的文件、#define宏定义的替换、条件编译等。预编译就是为编译前做准备工作的阶段,主要处理以#开头的预编译指令。 预编译指令指示

2022-01-13 13:52:27 0

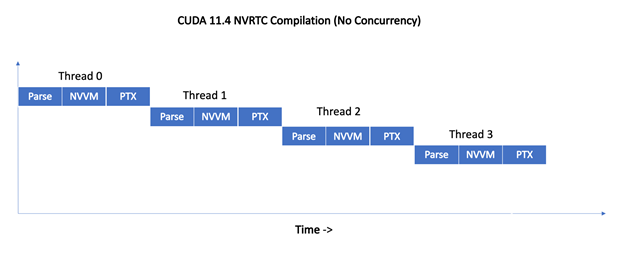

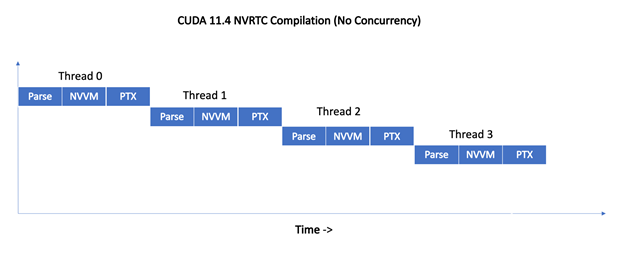

0 CUDA 11 . 5 C ++编译器解决了不断增长的客户请求。具体来说,如何减少 CUDA 应用程序构建时间。除了消除未使用的内核外, NVRTC 和 PTX 并发编译有助于解决这个关键问题 CUDA C ++应用程序开发的关注点。

2022-04-06 11:59:23 1894

1894

【GCC编译优化系列】实战分析C工程代码可能遇到的编译问题及其解决思路

2022-07-10 23:15:27 919

919

交叉编译器中“交叉”的意思就是在一个架构上编译另外一个架构的代码,相当于两种架构“交叉”起来了。Ubuntu 自带的 gcc 编译器是针对 X86 架构的,而我们现在要编译的是 ARM 架构的代码

2022-09-29 09:12:33 2468

2468 增量实现由两个流程构成:原始流程和增量流程,如图所示。其中,原始流程提供网表。

2022-10-10 14:16:04 1120

1120 对大多数童鞋来说理解编译器将.c文件编译为.o文件并不大困难,但是却难以明白最后链接的过程是什么作用和为什么要这样做?

2022-10-13 09:36:59 3446

3446 随着器件容量的增大,设计复杂度的增加,用户在使用 Quartus 软件工程全编译时,与以往相比要耗费更长的时间。目前在 Arria10,Stratix10 等器件上,资源消耗在 50% 以上

2022-12-20 14:36:13 2034

2034 在前文 《 如何为嵌入式软件开发选择编译器》 中讲到编译器对于嵌入式软件开发的重要性,以及如何选择一款优秀的编译器。 文中也比较了现有主流编译器的编译优化性能,IAR Embedded Workbench编译器不论在输出代码体积还是性能均处于业界领先地位。

2023-04-14 09:11:38 1371

1371

在《深入浅出编译优化选项(上)》中,我们介绍了如何在IAR Embedded Workbench编译器中进行编译优化等级配置、多文件编译配置、灵活配置编译优化选项作用域、链接阶段优化选项配置等。

2023-04-21 10:19:11 732

732 逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。 增量编译功能,可以使设计更快速时序收敛,加快编译速度。

2023-05-25 11:22:11 801

801

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项。

2023-05-25 18:25:34 2893

2893

VCS是一款常见的Verilog编译工具,它提供很多编译选项来控制编译过程及其输出。本文主要介绍以下两个编译选项。

2023-05-29 14:46:39 6967

6967 程序员做软件开发,比较讨厌一件事,那就是编译代码速度很慢的问题。 尤其是C/C++代码,编码一分钟,编译一小时钟,这谁能受的了?

2023-07-06 10:53:50 828

828

编译m4-1.4.17库时出现关于 freadahead.c中编译错误

2023-07-14 10:35:43 1888

1888 增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。

2023-09-01 09:36:49 362

362

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。它解决了实现阶段针对快速迭代的需求,显著节省了编译时间,还能确保所得结果和性能的可预测性。 以下图表显示了在一整套困难的设计上采用增量实现流程后,所节省的编译时间的变化趋势。

2023-09-04 10:07:01 372

372

增量综合的工作方式与增量实现流程相似,但仅适用于综合阶段,并且不会对紧随其后的实现阶段给予引导。

2023-09-08 11:01:37 276

276

这篇博文介绍了多种自动生成报告的有效途径,以便您在尝试对设计中特定阶段所耗用的编译时间进行调试时使用,例如,自动报告加载设计约束的时间、每条命令的持续时间,甚至是跨多个设计的运行时间差异。

2023-09-15 10:44:46 353

353

影响编译时间的因素有很多,包括工具流程、工具设置选项、RTL 设计、约束编辑、目标器件以及设计实现期间各工具所面临的任何关键问题。除此之外,所使用的机器及其负载也是关键因素。在这篇博客中,我们只探讨

2023-09-27 09:52:46 333

333

获得编译命令及选项 编译linux时,默认不会显示编译的命令,如果你要获得编译命令及其选项,可以在make命令后面加上宏定义: make V= 1 如果希望编译系统告诉你为何某个目标文件需要重新编译

2023-09-27 11:52:17 316

316 虽然想必您知道,在综合或实现阶段,增量运行可以从参考文件中读取和复制信息,但仅在某些阶段中能节省时间,如果网表发生大量更改,其中引用的内容就会减少,编译时间也会受到相应影响。

2023-10-09 16:48:33 822

822

主要介绍如何在本地搭建编译环境来编译rockchipBBuildrootllinuxSDK的源代码。d当前sdk只支持在linux环境下编译,并提供linux的交叉编译工具。

2021-12-13 11:23:13 18

18 为什么我们编写的C语言要进行编译?什么是编译?编译时发生了什么? 机器无法理解我们编写的C语言,而编译就是将面向人类的高级语言转换成为面向机器的机器语言的过程,图1是GCC编译器进行编译的过程,编译

2023-11-24 15:47:45 363

363

为了使用java8及后续java新版本的特性,Google增加了一步编译过程—脱糖(desugaring),但这一步会导致更长的编译时间,这也是为什么Google会推出D8和R8编译器来优化编译速度。

2023-12-21 09:21:59 337

337

电子发烧友App

电子发烧友App

评论