LTC1594L,4/8通道,3V微功耗采样,12位串行I / O A / D转换器的典型应用。它们通常在转换时仅消耗160uA的电源电流,并在转换之间自动关断至1nA的典型电源电流

2020-06-16 16:47:35

本帖最后由 eehome 于 2013-1-5 10:11 编辑

24C02串行E2PROM的读写

2012-08-10 14:07:14

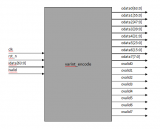

LTC1598L的典型应用 -4通道和8通道,3V微功耗采样12位串行I / O A / D转换器

2019-06-10 09:31:59

什么是串行通信?80C51串行口的工作方式有哪几种?串口如何使用?

2021-10-21 09:03:06

80C51串行口的结构有两个物理上独立的接收,发送缓冲器SBUF,他们占用同一地址,99H,接收器是双缓冲结构发送缓冲器,因为发送是CPU是主动的,不会产生重叠错误。串口的控制寄存器

2021-12-08 06:34:02

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

各位大神是否能用400个以上I/O口的FPGA芯片,实现串并转换,一个串行RS232输入,将输入的50个字节的数据转换控制 50个8位并行输出。具体大概应该怎么做

2015-07-08 17:19:33

1、FPGA内部AD多通道采样实验设计与实现编写程序,使用Anlogic 自带的ADC进行四通道数据轮询采集,同时介绍TD软件IP核的用法。本实验设计使用FPGA自带的12位串行AD芯片工作,将直流

2022-07-15 18:18:37

,数据的缓冲区可以开得很大,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,应该用同步时序设计完成串并之间的转换。比如数据从串行到 并行,数据排列顺序是高位在前,可以用下面的编码实现:prl_temp

2012-02-10 11:40:52

各位学者好,我一直不懂串行和并行通信的应用,以及传输时间和频率的问题例如我要用15MHz采样频率的外部AD采集正弦模拟信号,选的AD芯片采用8位串行通信,那么我听说串行通信时要占用DSP的频率为15M×8=120MHz这个是为什么?希望解释一下,如果能形象地讲解串并联通信就更好了,谢谢各位学者!

2016-07-15 11:40:58

作者:Michael Peffers 欢迎阅读《获得连接》系列博客!在上篇《获得连接》博客《解密串行解串器》一文中,我们探讨了如何通过串行解串器器件实现并行数据的串行解串。本文我们将探讨串行解串器

2018-09-13 10:01:00

AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-13 09:57:27

AT24C02串行E2PROM的工作原理与读写

2012-07-31 21:47:47

AT25128A是ATMELCorporation公司生产的一款144位串行电可擦除可编程只读存储器。它提供131,072/262,144位串行电可擦出可编程的只读存储器(EEPROM),换算成

2021-04-23 08:03:09

AT89C51串行口工作方式是什么?AT89C51单片机在无线数据传输中的应用是什么?

2021-06-07 06:21:32

GM8827C 实现27位RGB信号和3位控制信号 HS、VS、DE 的并串转化功能24 位 LVDS 发送器1 、产品概述本产品为一款多通道 LVDS 串行发送器,实现将 27 位 CMOS

2022-01-25 06:02:31

LTC1598的典型应用 -8通道,微功耗采样12位串行I / O A / D转换器

2020-06-16 14:19:18

M95256串行(SPI)EEPROM数据存取驱动仿真1、M95256介绍M95256 器件是组织为 32768 x 8 位的电可擦除可编程存储器 (EEPROM),可通过 SPI 总线访问

2022-02-15 06:45:40

10bits 并串/串并转换芯片,用于 LVDS 差分底板上传输和接收 10MHz 至 80MHz 的并行字速率的串行数据。加载起始停止位后,转换为一个串行数据速率在120Mbps 至 960Mbps 负载编码

2021-12-07 09:52:07

1、MSP430串行通信概述串口是系统与外界联系的重要手段,在嵌入式系统开发和应用中,经常需要使用上位机实现系统调试及现场数据的采集和控制。一般是通过上位机本身配置的串行口,通过串行通信技术

2022-02-15 06:52:31

•8位串行发送器的可选择时钟可达48 MHz,产生最大的6 Mbit数据速率 •数据成帧包括起始位、可选奇偶校验位和停止位•RS-232串行数据格式兼容偶校验、奇校验或无奇偶校验 •在发送缓冲区为空时可选择触发中断

2012-11-20 15:44:18

的逻辑1或逻辑0有多个位没有变化时,信号的转换就会因为电压位阶的关系而造成信号错误。直流平衡的最大好处便是可以克服以上问题。8B/10B编码是目前许多高速串行总线采用的一种编码机制,如1394b

2018-12-11 11:04:22

STM32407外接AD76026串行模式,有无大佬有参考代码参考一下啊

2021-01-08 16:33:15

处理器与外部设备通信的两种方式:并行通信传输原理:数据各个位同时传输。优点:速度快缺点:占用引脚资源多串行通信传输原理:数据按位顺序传输。优点:占用引脚资源少缺点:速度相对较慢串行通信:按照

2022-01-14 06:36:55

在我们使用STM32串行通讯时,可能用到多个USART串口,而此时printf只能向一个串口打印,见上篇,此时我们需要按照如下编辑个新的函数,实现向其它串口打印数据。1.添加文件2.函数定义及编辑 按照上述操作编辑相应函数之后,再进行正常的USART串口配置,即可进行正常的串行通讯串口发送。...

2022-02-23 06:56:59

TLC2543串行A/D转换程序即pretous仿真电压表测量

2012-11-27 20:16:59

TLC2543串行模数转换器参数资料下载内容主要介绍了:TLC2543外观图TLC2543特点TLC2543引脚功能TLC2543内部方框图

2021-05-21 07:44:43

这是TLC549串行模数转换程序:CSBITP1.7DATBITP1.6CLKBITP3.0AD_DATADATA30HORG0000HAJMPMAINORG0100HMAIN:MOVSP

2015-01-04 14:26:15

W25Q64串行FLASH基础知识大小:8M(Byte)(128块(Block),每块64K字节,每块16个扇区(Sector),每个扇区4K字 节,每个扇区16页,每页256个字节)特点

2021-07-22 09:32:51

模式。XCF08P版本包括32兆位,16 - Mbit的,和8兆位串行PROM,支持主,从串行SelectMAP和SelectMAP FPGA配置模式。

2010-04-07 13:37:44

`《微机原理与汇编语言》89C51串行口及串行通信技术[hide][/hide]`

2017-04-05 12:51:12

本帖最后由 eehome 于 2013-1-5 09:44 编辑

串行接口(RS-232) 连接到PC与FPGA的串信接口是一种简单的连接方式。本节课程将向大家展示了如何在一个FPGA上创建

2012-03-20 14:05:46

长等优点,本文将着熏介绍串口通信的连接方式以及利用C语言编程实现串口通讯,最后以实际的工程项目应用,验证了该通讯方式的可靠性。 1 RS232串行接口 1.1 RS232接口简介 RS232串行

2019-06-17 05:00:08

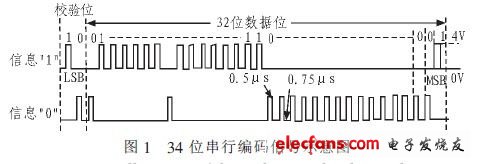

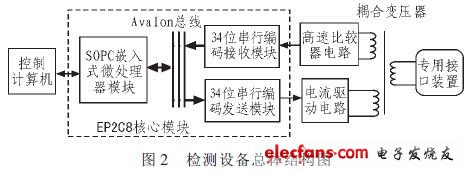

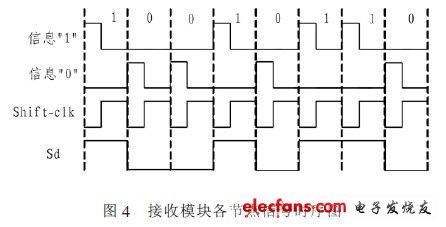

、RS485以及ARINC429等都是电子设备中常用的串行数据传输标准。某专用接口装置采用一种点对点的34位串行编码数据传输标准,34位串行编码经耦合变压器调制后进行信息传输,能够在恶劣的电磁环境下

2019-09-20 07:52:56

模数转换原理是什么?它的过程是怎样的?八位串行A/D转换器ADC0832具有什么特点?工作原理是什么?

2021-09-29 06:50:05

关于MAX9247/MAX9218串行器/解串器芯片组的性能测试详细解析

2021-04-12 06:11:46

给TLC2355写一个驱动,由EPM570控制它采样,TLC2355为14位串行AD,采样率达3.5M(串行时钟可达63M,63M/18=3.5M),其实只要弄懂这个串行AD的操作时序,写起代码

2011-09-02 14:00:52

现有一串行信号,需延时2ms,用芯片如何实现,不用单片机。

2015-04-27 20:35:39

四通道12位串行输入数据转换器AD5735资料下载内容包括:AD5735引脚功能AD5735内部方框图

2021-03-30 07:37:08

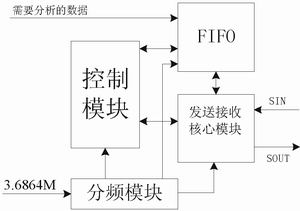

数据,并发送给从机;(2) 接收来自从机的串行数据,将其转换为并行数据,通过并行端口输出;(3) 输出从机所需要的输入信号、时钟信号SCK 和片选信号CS。在数据串并转换的过程中, 必须用到寄存器来存放临时

2015-01-28 14:09:51

基于Keil C的AT24C02串行E2PROM的编程AT24C02是美国Atmel公司的低功耗CMOS型E2PROM,内含256×8位存储空间,具有工作电压宽(2.5~5.5

2009-08-18 17:13:25

存储器中读取16字节数据,经并串转换输出16路的串行数据。从波形图分析,功能正确,且各输出端口信号均符合时序要求。 5结语 FPGA是在线可编程芯片,可以根据不同的用户要求进行不同的编程,缩短

2011-08-19 08:48:06

本帖最后由 tcvsdonnnie 于 2013-7-8 20:04 编辑

cc1101无线收发程序,已调试成功了,其中,发送端采用的是g2553的launchpad,接收端是采用的是f149控制的,且用了12864串行显示,

2013-07-03 21:37:00

如何去实现FPGA中的各个模块?如何去实现FPGA与PC的串行通信?

2021-05-26 07:25:13

请问一下有没有采用EEPROM对大容量FPGA芯片数据实现串行加载的实际方案?

2021-04-08 06:01:39

LTC1096的典型应用 - 微功耗采样8位串行I / O A / D转换器

2019-06-03 08:49:16

本文介绍的基于可编程门阵列( FPGA) 实现的冲击信号处理芯片,能在飞行器飞行过程中,实时完成对三路冲击信号的分析和处理,将冲击信号的处理结果代替冲击波的原始测量数据传到地面,利用冲击信号

2021-05-26 06:28:43

,因为一切都不能随机出现,必须在给定的时间内发生。系统时钟可分配给包括串行解串器在内的所有组件,以帮助实现同步工作。网络处理单元 (NPU) 或 FPGA 等终端器件不仅可在所需的系统频率下实现并行

2018-09-13 09:54:18

无限采样保持使用与LTC1658串行14位DAC接口的LTC1417串行14位ADC

2020-04-02 10:00:45

您好Xilinx社区,我喜欢在时钟ADC和FPGA Spartan 6的通用时钟之间以90°的方式提供相位信号。之前,我的信号使用not功能进行180°定相。我的时钟信号只编码一位。请问你能帮帮我

2019-03-06 12:13:51

最新51串行编程器的全部制作资料及软件

2012-08-06 22:25:19

如何用EEPROM对大容量FPGA芯片数据实现串行加载?如何设计并-串转换时序?

2021-04-29 07:13:12

有谁写过AD9851串行传送的程序吗?

2013-08-02 22:35:46

求大佬分享一种RS-232串行通信消除干扰噪声的设计方法

2021-06-02 07:13:35

GM7122是由成都国腾电子技术提供的一款视频编码芯片,视频编码电路主要实现接收 8 位 CCIR656 格式的 YUV 数据,(例如 MPEG 解码数据),并编码成 CVBS 信号,经过 D/A

2021-07-05 15:24:14

GM7122是由成都国腾电子技术提供的一款视频编码芯片,视频编码电路主要实现接收 8 位 CCIR656 格式的 YUV 数据,(例如 MPEG 解码数据),并编码成 CVBS 信号,经过 D/A

2022-04-26 10:45:25

GM7122是由成都国腾电子技术提供的一款视频编码芯片,视频编码电路主要实现接收 8 位 CCIR656 格式的 YUV 数据,(例如 MPEG 解码数据),并编码成 CVBS 信号,经过 D/A

2022-10-13 18:52:41

请问AD2S1210串行通讯的最大波特率是多少?

2018-09-10 10:34:13

请问AD2S1210串行通讯的最大波特率是多少?

2023-12-18 08:10:54

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

怎样去设计一种RS485串行通信接口电路?RS485串行通信接口电路的应用有哪些?

2021-06-02 06:35:15

谁介绍一款FPGA出串行高速2711串行接口芯片

2015-05-25 10:41:52

,不宜实现小型化。增量式光电编码器不具有计数和接口电路,一般输出A、B、Z脉冲信号,价格较低,在实际工程中比较常用。文中设计了一个基于FPGA的简单且精度高的接口电路,其结构简单、性能可靠。具有滤波

2019-06-10 05:00:08

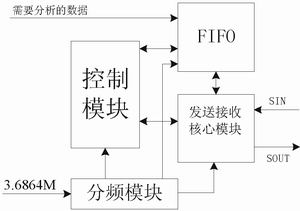

为了使计算机能够通过串口控制FPGA 的输出信号,笔者根据异步串行通信的原理,设计了简便易行的FPGA 串行通信接口系统,并应用VHDL 语言在FPGA 内部集成了串行接收模块,具有较强

2009-09-24 15:52:56 18

18 基于单片机的CPLD/FPGA被动串行下载配置的实现:介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行模式的下载配置,阐述了其原理及软硬件设计。 &nb

2009-10-29 21:57:22 19

19 AD7849是一款14/16位串行输入乘法DAC。该DAC架构可确保拥有出色的微分线性性能;在额定温度范围内,A级产品可保证14位单调性,所有其它等级产品可保证16位单调性。在上电与关断期间(当电源

2023-03-06 14:05:11

基于FPGA的各种雷达信号产生方法,介绍了在FPGA中实现直接数字频率合成器(DDS)以及提高输出信号质量的方法,编程实现了频率捷变、线性调频以及相位编码等雷达信号的产生。仿真

2010-11-29 18:02:49 31

31 摘 要:本文主要介绍了基于FPGA技术实现与PC串行通信的过程,给出了各个模块的具体实现方法,分析了实现结果,验证了串行通信的正确性。引言串行通信即

2006-03-24 13:31:51 4661

4661

摘要: 在简单介绍算术编码和自适应算术编码的基础上,介绍了利用FPGA器件并通过VHDL语言描述实现自适应算术编码的过程。整个编码系统在LTERA公司的MAX+plus Ⅱ软

2009-06-20 13:40:24 1026

1026

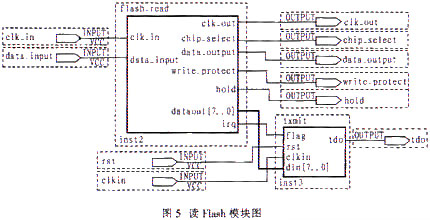

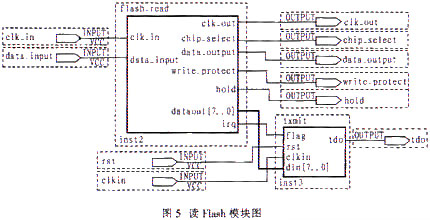

基于FPGA的串行Flash扩展实现

FPGA凭借其方便灵活、可重复编程等优点而日益被广泛应用;闪速存储器(Flash Memory)以其集成度高、成本低、使用方便等优点,在众多领域中

2010-01-12 10:39:55 1363

1363

研究了能够同时对多路 光电编码器 脉冲信号进行细分、计数以及传输的数据采集处理系统。提出了以高度集成的FPGA芯片为核心的设计方式,实现6路光电编码器信号的同步实时处理。坐

2011-08-18 16:33:15 90

90 本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

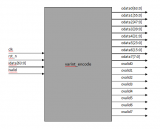

61 为实现某专用接口装置的接口功能检测,文中详细地介绍了一种34位串行码的编码方式,并基于FPGA芯片设计了该类型编码的接收、发送电路。重点分析了电路各模块的设计思路。电路采

2012-06-18 12:37:09 41

41 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 本文介绍了基于DSP和FPGA的编码器信号测量及处理的通用模块,对海德汉编码器进行了概述等。

2017-10-13 18:17:29 19

19 介绍了单片机与FPGA 异步串行通信的实现方法,给出了系统结构原理框图及其部分VHDL 程序,并定义了发送器和接收器的端口信号。

2020-09-29 16:20:00 8

8 介绍了单片机与FPGA 异步串行通信的实现方法,给出了系统结构原理框图及其部分VHDL 程序,并定义了发送器和接收器的端口信号。

2021-03-02 13:52:00 15

15 串行信号接收芯片AU5561可以解码Ts5647、Ts5648、Ts5667、Ts5668、Ts5669等型号的编码器,可以提供40到iiO位串并信号的转换,并且可以和1s/32位CPU或DsP总线

2021-03-29 10:15:55 7

7 今天是画师第二次和各位大侠见面,执笔绘画FPGA江湖,本人最近项目经验,写了篇基于FPGA的Varint编码(压缩算法)实现,这里分享给大家,仅供参考。如有转载,请在文章底部留言,请勿随意转载,否则

2021-04-02 16:29:16 1580

1580

传输系统的组成结构如图1所示,主要由两块ATCA板和一块ATCA机箱背板组成。两块ATCA板上各放置一片FPGA作为串行链路的两个端点,两片 FPGA之间用两对差分线进行连接,形成

2021-05-05 16:49:00 4740

4740

现场可编程逻辑阵列(FPGA)资源丰富,结构灵活,近年来发展迅猛。针对其特点,本文设计了基于FPGA的增量式光电编码器的接口电路,实现了对增量式编码器脉冲信号的倍频、鉴相及计数等功能。

2021-04-27 13:57:50 3886

3886

电子发烧友App

电子发烧友App

评论