跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这在SOC设计后期,也就是要对时序签字时可能会导致问题。后端设计工程师要知道跳变点的概念及其含义,这个非常重要。这也正是本文目的之所在。

1.跳变点定义:

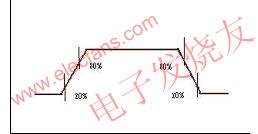

跳变点可定义为逻辑高电平的百分比,作为测量压摆率和时延值的参照。图1(a)演示的是压摆率跳变点。

图1(a)

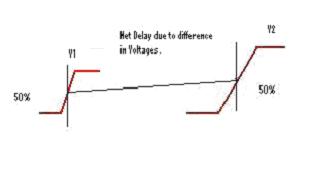

图1(b)演示的是时延跳变点。

图1(b)

跳变点用来描述标准单元或硬模块(IP)等的引脚过渡值特征,同时检查SoC时序。通常跳变点的值在时序模型(自由格式)中提及,时序分析工具在计算时延和压摆率时会使用这些值。

2.如何固定跳变点:

在描述标准单元或硬模块(IP)特征时,跳变点对于特定的技术节点是固定的。将跳变点固定的目的是确保测量的时延/压摆率接近实际(Spice)的波形。如图2(a)所示,当跳变点位于切换波形的线性区(20%-80%)时,压摆率值比位于非线性区(10%-90%)时要令人乐观。

图2(a)

通常情况下,在过渡跳变点位于线性区时,时序工具计算的单元时延更接近Spice结果。

同时,晶体管的电压阈值(Vt)特性对于决定跳变点发挥了重要作用,因为输出波形在输入电压超过晶体管的Vt值后会发生线性化[1]。

时延阈值在输入和输出波形的线性区是固定的。只要时延跳变点位于波形的线性部分,那么时延跳变点是20-80还是50-50都没有关系。

3.自由格式提及的跳变点句法[2]

下面给出的是典型时序模型(.liberty文件)的快照,以指示正在使用的跳变点

input_threshold_pct_rise:50;

input_threshold_pct_fall:50;

output_threshold_pct_rise:50;

output_threshold_pct_fall:50;

slew_lower_threshold_pct_rise:20;

slew_lower_threshold_pct_fall:20;

slew_upper_threshold_pct_rise:80;

slew_upper_threshold_pct_fall:80;

4.时序工具如何处理跳变点来计算时延

a)当跳变点对于界面都相同时:

图3(a)描述了驱动程序和负载具有相同时延阈值时的情况。

在给出的示例中,两者都为50%。

图3(a)

此时,,考虑压摆率降级(由网络引起)后,时序工具计算的驱动程序达到其50%的逻辑高值和负载达到其50%的逻辑高值时两者之间的时间差。

类似的解释对于特定单元的输入和输出产生的下降信号和时延同样适用。压摆率值根据.lib中提及的变量进行计算。

b)当跳变点对于一个界面而不同时

(i)20%比50%:

图4(a)描述了驱动程序时延跳变点为20%而对负载单元跳变点为50%的情况。

在这种情况下,与负载信号相比,驱动程序的信号会快速达到其时延跳变点值。因此此类界面的网络时延会大于驱动程序也达到50%情形下的时延[图3(a)]。

图4(a)

时序工具可通过线性或非线性扩展计算网络上出现的额外时延。

(ii)50%比20%

图4(b)描述了驱动程序跳变点为50%而负载单元的跳变点为20%的情形。

在这种情况下,与驱动信号相比,负载的信号会更早达到其时延跳变点值。这种情况通过时序工具借助扩展(线性或非线性)来进行处理。

图4(b)

这里需要注意的是:在这种情况下,扩展会引起“负时延”。

应注意:尽管现实世界不能在时域中后向穿越,但是时序工具需要将这种时延考虑在内,这样,从开始点(在本例中为驱动单元的输入引脚)到终端点(在本例中为负载单元的输出引脚)的整体路径时延接近现实世界时延(Spice)。

5.与跳变点相关的其他问题:

(i)SDF中的负时延:在通过时序工具完成扩展后产生的负时延将以标准时延格式(SDF)进行复制,用于门级模拟。不希望发生这种情况,因为门级模拟器无法处理负时延。

它们要么标志错误消息要么表示此类情况的零时延。作为一种变通方法,可编写一个脚本(附录A),根据所计算的负时延,增加(或减少)负载单元(或驱动单元)时延。

(ii)端口和IO单元之间的附加时延:

通常时序工具报告端口到I/O单元的时延。在硅片上,该网络作为接合线出现在芯片外部。因此,对于该网络物理信息不能进行量化。

时序工具提供此类网络的时延报告。原因包括:

a)由于没有时序模型可用于端口,因此时序工具采用用户定义的或默认跳变点和电压电平计算时延。

b)由于假定跳变点和端口w.r.tI/O单元跳变点的电压电平值之间有差额。图5(a)和图5(b)描述了此类情况。

图5(a)

图5(b)

要克服这种情况,可执行以下操作:

1)为与I/O单元的端口相同的端口定义运行条件。

2)编写脚本为此类网注释零时延。

(iii)带有丢失跳变点的库

如果我们拥有不包含跳变点阈值或电压电平值的时序模型,那么来自/到此类模型的界面的时延可能不正确。因为时序工具使用跳变点和电压电平的默认值,分析这些路径。作为一种变通方法,用户应在向负责库的人员进行咨询后,再定义跳变点。

6.如果不通过时序工具进行扩展会怎样:激烈。这可能会导致芯片故障,因为使用时序工具计算的时延不接近Spice值。如果可以为跳变点不同的界面进行Spice分析,应当是一种很好的操作方法。

如果对SOC中所使用的所有模型(硬模块)使用同样的跳变点,应当是一种很好的操作方法。

这完全可以消除因阈值不同所产生的问题。

7.Spice合作关系:

对多阈值路径进行Spice分析,是增强信心并解决时序问题的好方法。

尽管在Spice世界,阈值实际并不存在。在时序模型中使用它们是为了简化时序分析工具。

时序工具提供一个选项,复制出特定时序路径的spice网列表。除了spice网列表外,还复制出包含输入矢量的激励文件。复制出的spice网列表可能不包含针对时序路径中标准单元和/或硬模块的spice网列表。

Spice模拟工具可读取复制的spice网列表和标准单元/硬模块的spice网列表,然后提供激励文件来模拟重要路径。

需要通过分析生成的波形,查看路径是否满足时序要求。测量SPICE中此类路径的时延和过渡值时需要谨记:要采用与时序模型中所提及的跳变点相同的跳变点。

8.扩展类型:

大多数行业标准工具使用线性或非线性扩展作为其运作方式

a)线性扩展:在该方法中,工具假定不同阈值的线性斜坡。

该方法使用相似三角形的概念扩展驱动程序到负载单元的时延。

b)非线性扩展:此时,工具使用电流源模型来定义坡道。这需要通过复杂的数学方程来计算时延。

总之,本文以跳变点定义开始,然后阐释如何固定用于特定技术库的跳变点。然后本文论述了时序工具如何解释跳变点,以及当驱动程序与负载单元跳变点不同时可能会引发的问题。

附录 A:在SDF中考虑负互连时延的脚本

#!/usr/local/bin/perl

print "\n***************RUNNING PERL SCRIPT negaTIvedelinsdf_assarray.pl****\n\n";

if (!exists $ARGV[0] || !exists $ARGV[1]) { print "USAGE:: negativedelinsdf_assarray.pl

}

open(FILEA,$ARGV[0]) || die ("ERROR:: SDF file $ARGV[0] cannot be opened for reADIng\n");

open(file1, ">$ARGV[1]") || die ("ERROR:: file $ARGV[1] cannot be opened for writing\n");

while(

{ $line = $_;

$line1 = $line;

$line =~ s/^\s+//g ;

if ( $line =~ "INTERCONNECT.*-[0-9]") ######## FINDING NEGATIVE INTERCONNECT ######

{

@array1 = split(/\s+/,$line);

$count = @array1;

if ($count == 4){ ## To accont for the fact that only one INTERCONNECT triplet is present

$array1[$count]= $array1[$count-1];

$count = $count + 1;

}

for($i=0;$i<= $count -3;$i++)

{print file1 "$array1[$i] ";}

$value2 = $array1[$count -1];

$value1 = $array1[$count -2];

$instance_name = $array1[2];

@instance = split(/\//,$instance_name);

$count2 = @instance;

$pin_name = $instance[$count2 -1]; ####### GETTING LOAD INSTANCE PIN NAME ###############

$instance_name =~ s/\/[^(.*\/)][A-Z0-9a-z_\[0-9\]+]*$//g; ####### GETTING LOAD INSTANCE NAME ###############

if( $value1 =~ "::")

{ $value1 =~ s/[()]//g;

@correct_value1 = split(/::/,$value1);

$load_correct_value1_0{$instance_name} = $correct_value1[0];

$load_correct_value1_1{$instance_name} = $correct_value1[1];

if($correct_value1[0] <= -0.0) #####NEGATIVE CHANGED TO ZERO DELAY######

{$correct_value1[0] = "0.000";}

if($correct_value1[1] <= -0.0)

{$correct_value1[1] = "0.000";}

print file1 "($correct_value1[0]::$correct_value1[1])";

}

elsif( $value1 =~ ":[^:]")

{ $value1 =~ s/[()]//g;

@correct_value1 = split(/:/,$value1);

$load_correct_value1_0{$instance_name} = $correct_value1[0];

$load_correct_value1_1{$instance_name} = $correct_value1[1];

$load_correct_value1_2{$instance_name} = $correct_value1[2];

if($correct_value1[0] <= -0.0) #####NEGATIVE CHANGED TO ZERO DELAY######

{$correct_value1[0] = "0.000";}

if($correct_value1[1] <= -0.0)

{$correct_value1[1] = "0.000";}

if($correct_value1[2] <= -0.0)

{$correct_value1[2] = "0.000";}

print file1 "($correct_value1[0]:$correct_value1[1]:$correct_value1[2])";

}

else{print file1 "$value1 ";}

if( $value2 =~ "::")

{ $value2 =~ s/[()]//g;

@correct_value2 = split(/::/,$value2);

$load_correct_value2_0{$instance_name} = $correct_value2[0]; ########NEGATIVE CHANGED TO ZERO DELAY#####

$load_correct_value2_1{$instance_name} = $correct_value2[1];

if($correct_value2[0] <= -0.0)

{$correct_value2[0] = "0.000";}

if($correct_value2[1] <= -0.0)

{$correct_value2[1] = "0.000";}

if ($correct_value1[0] == $correct_value2[0] && $correct_value1[1] == $correct_value2[1] ) { # Print these values only if they are differnet from the already printed values for the INTERCONNECT

print file1 ")\n";

} else {

print file1 " ($correct_value2[0]::$correct_value2[1]))\n";

}

}

elsif( $value2 =~ ":[^:]")

{ $value2 =~ s/[()]//g;

@correct_value2 = split(/:/,$value2);

$load_correct_value2_0{$instance_name} = $correct_value2[0]; ########NEGATIVE CHANGED TO ZERO DELAY#####

$load_correct_value2_1{$instance_name} = $correct_value2[1];

$load_correct_value2_2{$instance_name} = $correct_value2[2];

if($correct_value2[0] <= -0.0)

{$correct_value2[0] = "0.000";}

if($correct_value2[1] <= -0.0)

{$correct_value2[1] = "0.000";}

if($correct_value2[2] <= -0.0)

{$correct_value2[2] = "0.000";}

if ($correct_value1[0] == $correct_value2[0] && $correct_value1[1] == $correct_value2[1] && $correct_value1[2] == $correct_value2[2]) { # Print these values only if they are differnet from the already printed values for the INTERCONNECT

print file1 ")\n";

} else {

print file1 " ($correct_value2[0]:$correct_value2[1]:$correct_value2[2]))\n";

}

}

$load_instance{$instance_name} = $instance_name; ##SAVE ALL LOAD INSTACES FOR NEG DELAY IN THE ASSOCIATIVE ARRAY##

$load_pin{$instance_name.$pin_name} = $pin_name; ##SAVE ALL LOAD PINS FOR NEG DELAY IN THE ASSOCIATIVE ARRAY##

}

elsif ($line =~ "CELL" ) {

print file1 "$line";

$find = 0;

}

elsif($line =~ "INSTANCE ") ##CHECKING CORRESPONDING INSTANCES AND FIND FLAG = 1 IF FOUND######

{

print file1 "$line1";

@array2 = split(/\s+/,$line);

$instance_name2 = $array2[1]; ##GETTING THE LOAD INSTANCE NAME FOUND HERE##########

$instance_name2 =~ s/[()]//g;

$instance_definition{$instance_name2} = "$instance_name2" ;

if(exists $load_instance{$instance_name2}) ####COMPARE INSTANCE NAME WITH THAT SAVED IN ASSO ARRAY#####

{

if($load_instance{$instance_name2} eq "$instance_name2")

{$find = 1;}

}

}

elsif($line =~ "IOPATH" && $find == 1) ##AFTER INSTANCES ARE FOUND CHECKING FOR CORRSPONDING PINS######

{

@array4 = split(/\s+/,$line);

if ($array4[0] =~ "COND" ) { ## Take care of COND statements

$pin_name2 = $array4[3];

} else {

$pin_name2 = $array4[1];

}

if($line =~ "IOPATH" && exists $load_pin{$instance_name2.$pin_name2} ) {

if ( $load_pin{$instance_name2.$pin_name2} eq "$pin_name2" )

{

@array3 = split(/\s+/,$line);

$count3 = @array3 ;

@value_IOPATH = ""; # This is to initialize the array to blank

if ($array3[0] =~ "COND" ) {

for ($j=5; $j<=$count3 ; $j++) {

$value_IOPATH[$j-5] = $array3[$j];

$value_IOPATH_width = @value_IOPATH;

if ($count3 == 6) { #### In case there is only one triplet for COND.*IOPATH

$value_IOPATH[1] = $value_IOPATH[0];

}

#$value1_IOPATH = $array3[5];

#$value2_IOPATH = $array3[6];

}

$constant_fields = 4;

} elsif ($array3[0] =~ "IOPATH") {

for ($k=3; $k<=$count3 ; $k++) {

$value_IOPATH[$k-3] = $array3[$k];

$value_IOPATH_width = @value_IOPATH;

if ($count3 == 4) { #### In case there is only one triplet for IOPATH

$value_IOPATH[1] = $value_IOPATH[0];

}

#$value1_IOPATH = $array3[3];

#$value2_IOPATH = $array3[4];

}

$constant_fields = 2;

}

for($i=0;$i<= $constant_fields;$i++)

{print file1 "$array3[$i] ";}

if( $value_IOPATH[0] =~ "::") ####CORRECT OR ACCOMODATING THE NEG DELAY VALUES HERE #########

{ $value_IOPATH[0] =~ s/[()]//g;

@correct_value1_IOPATH = split(/::/,$value_IOPATH[0]);

if(exists $load_correct_value1_0{$instance_name2}) {

if($load_correct_value1_0{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

if ( abs($load_correct_value1_0{$instance_name2}) < $correct_value1_IOPATH[0] ) { ###the absolute value to negative delay is larger than the timing of load arc. ######

$correct_value1_IOPATH[0] = $correct_value1_IOPATH[0] + $load_correct_value1_0{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}

}

}

if(exists $load_correct_value1_1{$instance_name2})

{ if( $load_correct_value1_1{$instance_name2} < 0.0) {

if ( abs($load_correct_value1_1{$instance_name2}) < $correct_value1_IOPATH[1] ) {

$correct_value1_IOPATH[1] = $correct_value1_IOPATH[1] + $load_correct_value1_1{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

print file1 "($correct_value1_IOPATH[0]::$correct_value1_IOPATH[1])";

}

elsif( $value_IOPATH[0] =~ ":[^:]") ####CORRECT OR ACCOMODATING THE NEG DELAY VALUES HERE #########

{ $value_IOPATH[0] =~ s/[()]//g;

@correct_value1_IOPATH = split(/:/,$value_IOPATH[0]);

if(exists $load_correct_value1_0{$instance_name2}) {

if($load_correct_value1_0{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

if ( abs($load_correct_value1_0{$instance_name2}) < $correct_value1_IOPATH[0] ) {

$correct_value1_IOPATH[0] = $correct_value1_IOPATH[0] + $load_correct_value1_0{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}

}

}

if(exists $load_correct_value1_1{$instance_name2}) {

if($load_correct_value1_1{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

if ( abs($load_correct_value1_1{$instance_name2}) < $correct_value1_IOPATH[1] ) {

$correct_value1_IOPATH[1] = $correct_value1_IOPATH[1] + $load_correct_value1_1{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}

}

}

if(exists $load_correct_value1_2{$instance_name2}) {

if($load_correct_value1_2{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

if ( abs($load_correct_value1_2{$instance_name2}) < $correct_value1_IOPATH[2] ) {

$correct_value1_IOPATH[2] = $correct_value1_IOPATH[2] + $load_correct_value1_2{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}

}

}

print file1 "($correct_value1_IOPATH[0]:$correct_value1_IOPATH[1]:$correct_value1_IOPATH[2])";

}

else{print file1 "$value_IOPATH[0] ";} # This is to print empty brackets in case rise and fall triplets are empty

if( $value_IOPATH[1] =~ "::")

{ $value_IOPATH[1] =~ s/[()]//g;

@correct_value2_IOPATH = split(/::/,$value_IOPATH[1]);

if(exists $load_correct_value2_0{$instance_name2}) {

if( $load_correct_value2_0{$instance_name2} < 0.0)

{ if ( abs($load_correct_value2_0{$instance_name2}) < $correct_value2_IOPATH[0] ) {

$correct_value2_IOPATH[0] = $correct_value2_IOPATH[0] + $load_correct_value2_0{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

if(exists $load_correct_value2_1{$instance_name2}) {

if( $load_correct_value2_1{$instance_name2} < 0.0)

{ if ( abs($load_correct_value2_1{$instance_name2}) < $correct_value2_IOPATH[1] ) {

$correct_value2_IOPATH[1] = $correct_value2_IOPATH[1] + $load_correct_value2_1{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

if ($correct_value1_IOPATH[0] == $correct_value2_IOPATH[0] && $correct_value1_IOPATH[1] == $correct_value2_IOPATH[1]) { # Print these values only if they are differnet from the already printed values for the IOPATH

} else {

print file1 " ($correct_value2_IOPATH[0]::$correct_value2_IOPATH[1])";

}

}

elsif( $value_IOPATH[1] =~ ":[^:]")

{ $value_IOPATH[1] =~ s/[()]//g;

@correct_value2_IOPATH = split(/:/,$value_IOPATH[1]);

if(exists $load_correct_value2_0{$instance_name2}) {

if( $load_correct_value2_0{$instance_name2} < 0.0) {

if ( abs($load_correct_value2_0{$instance_name2}) < $correct_value2_IOPATH[0] ) {

$correct_value2_IOPATH[0] = $correct_value2_IOPATH[0] + $load_correct_value2_0{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

if(exists $load_correct_value2_1{$instance_name2}) {

if( $load_correct_value2_1{$instance_name2} < 0.0) {

if ( abs($load_correct_value2_1{$instance_name2}) < $correct_value2_IOPATH[1] ) {

$correct_value2_IOPATH[1] = $correct_value2_IOPATH[1] + $load_correct_value2_1{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

if(exists $load_correct_value2_2{$instance_name2}) {

if( $load_correct_value2_2{$instance_name2} < 0.0) {

if ( abs($load_correct_value2_2{$instance_name2}) < $correct_value2_IOPATH[2] ) {

$correct_value2_IOPATH[2] = $correct_value2_IOPATH[2] + $load_correct_value2_2{$instance_name2};}

else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay \n";}}}

if ($correct_value1_IOPATH[0] == $correct_value2_IOPATH[0] && $correct_value1_IOPATH[1] == $correct_value2_IOPATH[1] && $correct_value1_IOPATH[2] == $correct_value2_IOPATH[2]) { # Print these values only if they are differnet from the already printed values for the IOPATH

} else {

print file1 " ($correct_value2_IOPATH[0]:$correct_value2_IOPATH[1]:$correct_value2_IOPATH[2])";

}

}

else{print file1 "$value_IOPATH[1] ";} # This is to print empty brackets in case rise and fall triplets are empty

for ($m=2;$m<=$value_IOPATH_width;$m++) {

if (exists $value_IOPATH[$m]) {

$value_IOPATH[$m] =~ s/\)+/\)/; # To account for the brackets

print file1 " $value_IOPATH[$m]";

}

}

if ($array4[0] =~ "COND" ) { ## Extra bracket for COND statements

print file1 "))\n";

} else {print file1 ")\n";}

}

}

else

{print file1 "$line1";} #######DUMPING OUT OF SDF IN FILE1######################

}

else

{print file1 "$line1";}

}

close(file1);

close(fileA);

open(FILEA,$ARGV[0]) || die ("ERROR:: SDF file $ARGV[0] cannot be opened for reading\n");

print "\n\n#############REPORTING INSTANCES WHOSE DEFINITION IS NOT THERE IN THE SDF#############\n";

while(

{

$line2 = $_;

$line2 =~ s/^\s+//g ;

if ( $line2 =~ "INTERCONNECT.*-[0-9]")

{ @array4 = split(/\s+/,$line2);

$instance_name3 = $array4[2];

$instance_name3 =~ s/\/[^(.*\/)][A-Z0-9a-z_\[0-9\]+]*$//g;

if(exists $instance_definition{$instance_name3})

{}

else

{print "$line2";}

}

}

close(fileA);

print "\n";

电子发烧友App

电子发烧友App

评论