摘 要: 设计了一种基于NiosII处理器的片上系统(SoC),集成了Nios II处理器IP、PCI接口IP、网络接口IP以及基于Wishbone总线的串行接口IP核、 CAN接口IP核等。系统具有可重配置、可扩展、灵活、兼容性高、功耗低等优点,适合于片上系统开发与应用。本设计使用Verilog HDL硬件描述语言在QuartusII环境下进行IP软核设计、综合、布局布线,在Model Sim下完成功能、时序仿真,在SoPC下完成系统的定制与集成,在NiosII IDE环境下完成片上系统软件程序的开发,最后在FPGA器件上实现了智能多接口功能的片上系统。

随着超大规模片上系统需求的日益增多,基于传统IC芯片的微电子应用系统设计技术正在转向基于知识产权IP(Intellectual Property)核的片上系统技术发展[1]。因此,基于资源IP核的复用设计方式已开始逐渐成为国内外微电子系统设计的一项支撑技术。从应用功能角度划分IP核有三大类:微处理器IP核(如8位8051核、32位NiosII、Microblaze核等)、各种接口IP核(如SDRAM控制器、 PCI总线接口、CAN总线接口、串行总线接口IP核等)和专用算法IP核(图形编解码H.264、加密核等)。使用IP核复用技术,将IP集成到 FPGA芯片上,可缩小PCB板体积,降低功耗;还可以根据需要进行功能的升级、扩充和裁减。本文以Altera公司的NiosII为主处理器并集成PCI接口、串行接口、CAN接口、网络接口设计为例,说明片上系统的设计方法。

1 设计原理

采用片上系统设计的智能多接口模块一般可以不需要外部主处理器操作系统的干预,其典型结构如图1所示。在工作时,片上系统收到的信号经过本板上Nios II处理器处理转换后,即可将数据信号送出或做其他处理。信号转换、处理工作全部由片上系统完成,不增加外主处理器操作系统的软件开销,因而对整个系统的负担更小。也可以要通过接入的PCI等系统总线,以中断提请等方式向外部主处理器提请访问,可完成与外主处理器的数据交换[4]。

在开源OpenCores组织的网站上,可以获取大量共享IP核, 但是大多数是未被验证的,或者由于是不同人撰写的,其代码风格也不尽相同。其接口信号定义为标准Wishbone总线形式,Wishbone着重定义IP 核的接口信号和总线周期标准来实现IP核的重用。通过对IP软核代码的分析,在原代码的基础上可通过修改IP核的部分逻辑功能(如增加内嵌数据收发 FIFO深度),优化部分接口逻辑;通过对异步信号同步采样一次,可以去干扰,消除亚稳态以及虚假的Glitch;可通过增加复位状态寄存器等实现优化设计。最终完成基于Wishbone总线的IP软核设计。下面以串行接口IP核设计为例说明,其他类型的IP核也可以通过类似方法获得。串行接口IP设计是以异步串行控制器16C550为原型的。

2.1.1 波特率发生器设计

波特率发生器通过两个8位的分频寄存器实现,它提供发送数据和接收数据的基准时钟。波特率发生器产生的时钟是串行数据波特率的16倍。上电复位后两个分频寄存器都为00H,不使能所有的I/O操作。

2.1.2 数据收发

数据发送主要由线控制寄存器、计数器、FIFO控制器、发送FIFO、发送移位寄存器等实现。在波特率设置好后,计数器统计帧数据的位数,确保发送的帧数据包括起始位、有效数据位、奇偶校验位、停止位。发送FIFO可以暂存总线接口发送过来的数据,数据从发送FIFO移入到输出移位寄存器,每16个时钟时间向外发送一位数据,先发送起始位,有效数据从移位寄存器的高位逐位移出,最后输出奇偶检验位和终止位。当发送FIFO内的数据低于FIFO设置触发深度时,会触发发送FIFO空中断。

数据接收由线控制寄存器、计数器、接收FIFO和输入移位寄存器等组成。接收数据的线控制寄存器、计数器功能同发送模块。接收器始终监视着串行输入端,将8位串行数据逐位接收进来。数据接收后会通过移位寄存器暂存在接收FIFO中, FIFO深度可支持1 B、32 B、64 B、128 B等。

2.1.3 中断设计

串行接口IP核中包含一个8位的中断使能寄存器(IER)和一个8位的中断识别寄存器(IIR)。中断使能寄存器可以使能5种中断源,分别是:接收线状态中断、发送线状态中断、时间溢出中断、发送寄存器空中断、Modem状态中断等,共4个优先级。上电复位时默认状态为全部中断屏蔽。上电复位时IIR为 C1H,通过读取IIR数值可获取相应的4路中断状态信息。

2.2 总线转换桥接逻辑设计

为了实现Wishbone和Avalon总线协议之间的协议转换, 根据两种片上总线的特性, 通过状态机的使用来实现总线协议的转换, 并使用软件仿真的方法建立模型来验证总线转换桥的可用性。 Wishbone到Avalon总线转换桥的总体组成原理如图3所示。

Wishbone到Avalon总线转换桥的基本功能是使得符合Wishbone总线体系结构的IP核可以在采用Avalon总线的NiosII 固核处理器片上系统中集成,从而实现对定制外设的访问。接口支持32位总线操作。总线转换桥由相对独立的Avalon主从端口单元和Wishbone主从端口单元组成,每个单元都有一套完整的功能来支持Avalon总线和Wishbone端口上所挂载的IP核之间的交易,读写数据实行分开存储,由配置和状态寄存器控制操作模式和数据的输入输出。Avalon总线接口逻辑与Wishbone接口逻辑两侧都包含本地状态机及其他控制逻辑,并且总线桥接口逻辑还包括地址译码、命令译码、接口控制状态机、数据输出MUX、奇偶校验输出、地址溢出检查等功能模块。

2.3 片上系统集成设计

基于NiosII固核处理器的片上系统集成是在SoPC Builder环境下完成的。片上系统集成主要完成对片上系统的定制、片上系统的资源分配、总线交换操作、中断处理等几个点关键技术点。

2.3.1 片上系统定制设计

片上系统的定制设计主要是完成片上系统集成所需要的处理器IP和外设IP的选型,是集成设计的第一步,设置系统主频,同时可选配指令、数据Cache大小、外部数据指令、硬件乘法器、流水线支持、浮点运算支持等特性,并设置NiosII的Cache和CPU直接相连的存储器。外设IP主要包括PCI总线接口IP、外部SRAM接口IP、外部Flash接口IP、外部GPIO接口IP、外部网络接口IP、自定制的基于OpenCore的串行接口IP核、 CAN总线接口IP软核等。

2.3.2 片上系统资源分配

SoPC为各IP自动分配了一个默认地址。考虑到资源有效利用,还需要对系统资源进行重配置,主要包括:对Boot Loader的存储器选择和设置Boot Loader在存储器中的偏移;存放异常向量的存储器选择及其偏移量;各外设在Avalon总线上的偏移地址、中断号的分配;PCI总线对片上 Avalon总线上设备的Memnry或I/O的空间以及地址映射;DMA传输配置;消息寄存器(Mailbox)双口RAM的使用等。具体分配如下:

(1)考虑到可以通过PCI到Avalon总线的地址映射,从PCI通过BAR端口直接访问两路UART、CAN、GPIO等设备,根据各接口IP地址特性,其他外设在Avalon端地址分配不冲突的前提下,有效分配Avalon地址资源,并可以在PCI端直接使用BAR2/BAR3以及Memory或 I/O访问此类外设。

(2)可以通过Auto Bass Address操作,解决外设的地址分配冲突问题。通过调整其他外设地址避免与Flash地址的冲突。

(3)可通过手动方式修改各个外设的中断号,也可以通过Auto Assign IRQs 操作,自动分配中断号(最低为0,最高31)。

2.3.3 总线数据交换操作

PCI总线与Avalon总线实现互相访问,须先确定PCI核的资源配置,然后根据资源配置选择总线数据操作方式。从PCI总线方向看PCI软核主要有以下几个部分:寄存器组、BAR0~BAR3、DMAC、PCI访问端口。带有PCI核的整体架构如图4所示。

对于含PCI总线接口IP的片上系统总线操作,可以分为DMA方式和非DMA方式。非DMA方式即PCI总线通过PCI核的BAR空间访问Avalon总线设备,而不经过DAMC的控制。非DMA方式的操作共分为4类,其中数据类操作两类:PCI总线读取Avalon总线设备的数据(支持连续数据)、 PCI总线将数据写入Avalon总线设备(支持连续数据);配置类操作两类:PCI总线读取Avalon总线设备的寄存器、PCI总线写入Avalon 总线设备的寄存器。数据类操作与配置类操作没有本质上的区别,只是数据类操作支持连续数据操作,数据通道是双口RAM,而配置类操作只支持单次操作,数据通道是MailBox组。PCI核的寄存器组包含两类MailBox寄存器组:P-A MBR和A-P MBR,每类MailBox组含8个32位寄存器。

3 软件设计

NiosII EDS(嵌入式开发包)基于开放式、可扩展Eclipse IDE的工程以及Eclipse C/C++开发工具提供了统一的开发平台,适用于所有NiosII处理器。 NiosII EDS为基于NiosII的系统自动生成板级支持包(BSP),包括硬件抽象层(HAL)、可选的RTOS以及设备驱动。BSP提供了C/C++运行环境,可以避免与硬件直接打交道。所有软件开发任务都可以在Nios II IDE下完成,包括编辑、编译和程序调试。

基于NiosII固核处理器的片上系统的BSP(板级支持包)设计主要以开发板源码为基础进行修改移植。系统通过bootloader进行引导,采用 Altera的集成开发环境NiosII 7.2 IDE进行操作系统?滋C/OSII的开发。在开发过程中采用软件模块化、通用化的编程思想进行设计,具体实现的驱动包括NiosII的驱动、PCI驱动、串行驱动、CAN接口驱动等。首先创建IDE的管理工程,然后选择目标硬件,IDE会建立系统库,根据向导就可以创建一个NiosII C/C++应用工程。最后是建立C的源文件和头文件,对C源文件和头文件编辑好后可对工程进行编译,编译中出的错误与警告IDE都会给出提示。

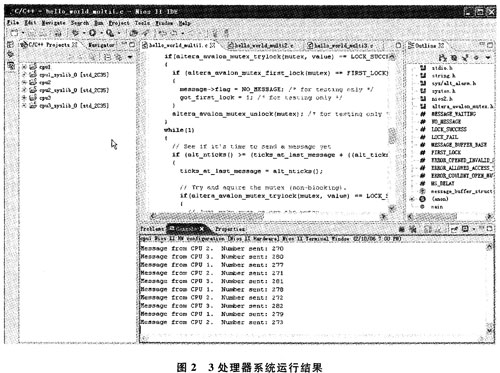

4 仿真与验证

为了验证串行接口IP核设计功能,需进行仿真测试与验证,其功能仿真如图5所示。

在Quartues II环境下完成该IP核编辑、编译、综合布局布线,并完成IP核相应的Testbench测试源代码的编辑、编译,在Model Sim环境下进行功能与时序仿真。对IP核的测试可以分别对Wishbone总线接口核和内部功能核两部分进行测试来完成。首先要对接口核部分测试,以确保能够正常进行读写操作,然后对功能核的每个功能模块和寄存器进行测试验证。结果证明其IP功能齐备,符合设计要求。

本文详细介绍了基于NiosII处理器的智能多接口片上系统设计与实现,采用Altera公司Cyclonell系列FPGA芯片EP2C35F672I8实现设计时,占用芯片资源小于50%。

随着超大规模片上系统的设计需求不断增加,其对IP核的性能、功能、可重用性以及灵活性等方面的要求将越来越高,而目前Xilinx、Altera等公司都已经推出了工作频率更高、布线时延更小、容量更大的新型FPGA芯片。可以将处理器核、总线接口核和专用算法核等集成在频率更高、性能更强大的 FPGA芯片上。

电子发烧友App

电子发烧友App

评论