基于机器视觉的车道偏离预警系统的实现

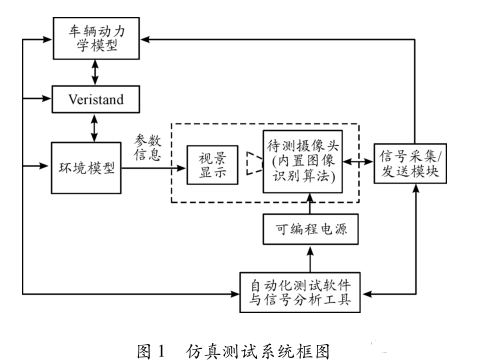

摘要:目前高速公路上由于车道偏离而导致的交通事故造成了巨大的损失,从而使得车道偏离预警系统的研究成为了社会的一大热点。本文基于DSP 计算和FPGA 计算,构造出一套基于视觉的车道偏离预警系统。本文给出了系统的框架结构以及硬件实现方式,并基于所提出的系统详细研究了视觉系统中大容量数据的传输、存储和处理等问题。最后,基于构造的系统,通过一系列典型的视觉处理算法和应用于车道跑偏决策的软件算法,验证了系统的可行性。

1、引言

汽车驾驶是涉及驾驶员、汽车、道路三方面因素的动作行为。驾驶员通过眼睛等一系列生理器官感受道路信息,通过对道路信息的理解和判断,及对汽车行驶状况的跟踪,做出一系列的驾驶决策。但是由于驾驶员长时间驾驶、粗心大意等一系列因素及驾驶员对道路信息的感知和车辆状况的了解存在一定的“盲区”,导致的交通事故越来越成为社会的一大主要安全隐患。本文从驾驶员、汽车、道路三方面入手,研究一套模拟人的驾驶行为来提高车辆行驶安全性的汽车主动安全系统,实现车道偏离预警等主动安全技术。

在基于机器视觉的系统中,实时性一直是一个主要的问题,尤其是像车道偏离预警这样的系统来说,要实现的算法更是覆盖了从图像预处理到高层视觉计算的整个视觉计算流程,既有底层的可高度并行实现的大数据量的卷积、灰度变换等规整算法,也包含有中层的特征提取等模式识别算法及高层的一些视觉处理方法,用以实现对道路的理解等。一直以来,嵌入式系统的通用性与效率一直是难以调和的一对矛盾[1],如何构造一套较通用的视觉处理系统,对于视觉各个层次的并行及串行算法,都具有较高的实现效率是本文要解决的一个问题,高速的DSP 处理芯片和大规模可重构芯片的出现为我们提供了一个很好的解决方案。

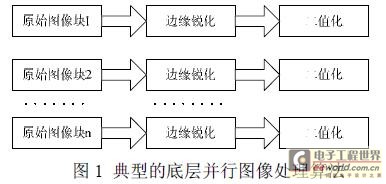

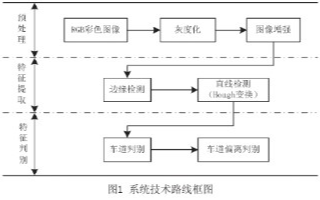

大规模的可重构芯片,诸如 FPGA 等,内部集成了大容量的基于查找表结构的门电路系统,非常适合构造细粒度的SIMD 处理阵列或者流水线结构,而这对于如图2 所示的典型的底层图像处理算法[1],具有着天然的适应性。TI 公司的C6000 系列的DSP 计算芯片,采用哈佛结构,内部具有8 个处理单元,还集成了专用的硬件乘法器,适合于完成一些串行的视觉处理算法,对于高层的数据量较少的但运算过程较复杂的道路理解等,具有较好的实现效果。

基于上面的分析,本文结合高速的 DSP 计算芯片和可重构的FPGA 芯片构造一套高速的嵌入式视觉处理系统,FPGA 作为辅助逻辑控制和前端处理模块,主要完成图像的前期采集和一些类似直方图统计、卷积等底层的高密度图像处理工作,可在硬件结构上灵活的配置,通过实现一系列的并行结构或流水线结构完成底层的算法,避免由DSP 完成这些细粒度的算法而造成资源的浪费和时间上的损耗;DSP 作为主要的计算中心,完成高层的串行为主的视觉处理任务,诸如道路理解和解释、车道跑偏决策等,DSP 的高速处理能力能较好的完成这些串行度高的算法。系统的基本框图如图2 所示。

2、系统设计与实现

实现图 2 的基于视觉的汽车主动安全系统,数据的存储和传输是一个主要的问题,尤其是对于汽车主动安全这样的实时性要求非常高的应用背景。如何在最短的时间内,由原始采集到的图像数据,经过一系列的存储器数据搬移及信号处理过程,获得最终的对道路的理解判断,并对车辆是否跑偏做出正确的决策,是本系统主要的实现目标。本文将依据数据在系统中的“流动”顺序对本系统进行详细的介绍。

2.1、数据采集模块

在本系统中,图像数据是主要的传感器信号,获得高质量的图像数据对后期的处理和功能的实现具有较大的意义。但是对于实际的应用环境,由于天气、光照等因素的影响,甚至是一系列特殊情况的出现,一般的图像传感器在各种条件下难以具有较好的鲁棒性。为了较好的适应各种道路和天气状况,保证驾驶的安全性,我们采用了适合道路使用的CMOS 数字摄像头芯片自主开发了视觉采集模块,该摄像头芯片通过159 位SPI 控制字可完全编程控制,较好的实现对曝光时间、增益和噪声等的调节。同时,该摄像头芯片采用了一种多斜率的曝光模式输出,在不同的曝光模式下,控制曝光的时间也是不一样的,保证在光照过强或者光照条件非常弱的情况下,都可获得较好的图像。

对于摄像头芯片的SPI 控制,本文为了自适应的调整在不同背景下的工作模式,由DSP根据最后对图像的理解和判断的结果,给予FPGA 一定的通信信号完成对摄像头芯片的顶层的系统级的控制,而底层的真正的SPI 控制字的修改和调整则由FPGA 来完成,这样可避免SPI 的工作频率和DSP 外部总线频率的不一致而导致的DSP 工作效率的浪费,而FPGA来完成这样的工作则比较容易。

2.2、数据传输、存储模块

在本系统中,从前端的图像采集模块,到最后的报警信号的输出,数据是不停的在FPGA、SDRAM 及DSP 之间进行传输和搬移,接下来主要讨论如何在这三者之间进行高速有效的搬移和处理,这也正是本文的主要模块。系统中的数据流程主要有以下几个方面:

Ⅰ、在 FPGA 中经过预处理的图像数据,首先必须存储到主存储芯片SDRAM 中,这是后端高层处理的基础。

Ⅱ、DSP从SDRAM中读取最新的图像数据进行处理,并将处理的中间结果存于SDRAM中,这样的读写过程很可能是循环进行的,SDRAM 的分块存储特性正适合这样的性能要求。

Ⅲ、为了系统调试的方便,很可能要求显示中间处理的结果,因此我们在 FPGA 上挂接了一块显示调试模块,调试时FPGA 可从SDRAM 中读取中间的处理结果进行显示。

Ⅳ、还有一种情况,某些情况下我们可能要求 DSP 和FPGA 之间直接进行图像数据的传输,这也是我们必须考虑的范畴。

综合上面的种种可能情况,考虑我们采用的 DSP 芯片同时支持FIFO 和SDRAM 芯片的无缝连接,我们设计了图3 的数据传输方案:

首先,前端的采集模块输出的图像数据是 8 位的,而对于我们采用的SDRAM 存储芯片和DSP 处理芯片,数据总线都是64 位的。为了不造成资源的浪费,在FPGA 对图像进行预处理的过程中,我们同时将8 位的图像数据拼接成64 的数据输出,这样可充分利用系统的资源。

其次,在 FPGA 中经过一系列并行预处理的图像数据,存储于FPGA 内部开辟的FIFO中。FPGA 给出握手信号,通知DSP 可以开始由FIFO 向SDRAM 传输数据,数据的传输过程则完全由DSP 通过EDMA 传输方式来控制完成。当核心处理器DSP 完成当前操作的情况下,再从SDRAM 中读入最新的数据进行处理,这可充分利用DSP 芯片丰富的外设资源。

同时,由图 3 的数据流图我们发现数据在由FPGA 向SDRAM 传输的过程中,相对于DSP 来说,FPGA 中开辟的用来存储数据的FIFO 模块和外部主存储器SDRAM 模块是挂接于DSP 上的相同的地址总线和数据总线上的,在这种源设备和目的设备挂接于相同外部总线上的传输形式下,我们采用的DSP 芯片支持一种优化的EDMA 传输模式-PDT 传输,它优化了数据的传输过程,使得DSP 的EDMA 传输模式可在数据不经过DSP 内的缓存区的情况下,直接由源设备FIFO 传输到目的设备SDRAM 中,从而可在一个周期内完成数据的传输。相比于传统的传输模式,先由FPGA 传输到DSP 内部的缓存区,再由DSP 写入到SDRAM 中,PDT 传输模式基本上可缩短一半的数据传输时间,对于像图像这样的大容量数据传输来说,是具有非常大的意义的。

完成了前端预处理模块到主存储器 SDRAM 的数据搬移过程,接下来主要是后端的高速数据传输过程。DSP 与SDRAM 之间的数据传输可达到100MHz 以上的高速速率,尤其是DSP 支持的EDMA 传输方式,更是允许不在CPU 干涉的情况下,就可完成外部数据与DSP 内部的Cache 之间的传输,这样可提高CPU 工作的效率。另外,DSP 芯片内部有两级的缓存,第二级缓存L2 更是可达到1MB,因此我们考虑采用现在流行的ping-pong 传输方式,当CPU 在处理缓存中的ping 或pong 内部的数据时,在可以预测剩余处理时间的前提下,我们可预先将接下来要处理的数据通过EDMA 方式传输到对应的pong 或ping 存储区中,这样便将数据传输的时间蕴含在了处理过程中,节省了相应的传输时间,提高了效率。

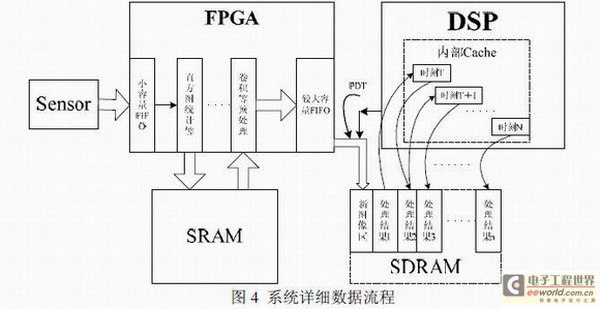

综合了上面对整个数据传输流程的分析,我们可以得出如图4 所示的数据搬移过程。由图中可以看出,从Sensor 出来的数据到FPGA 中的预处理,与DSP 内部的数据处理过程,在SDRAM 的缓存处理下,是可以以流水线的方式传输处理的,FPGA 作为前端预处理模块,完成大容量数据的处理过程,对于系统效率的提高具有非常大的作用。

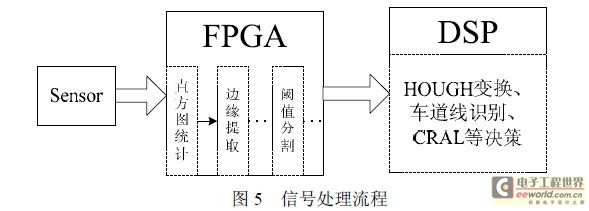

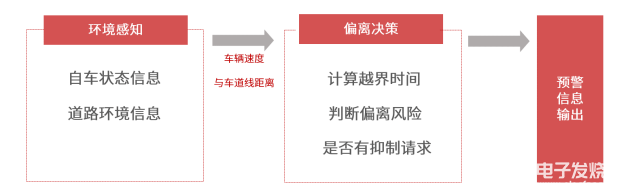

关于前端图像预处理方法及车道偏离决策算法的介绍性文章比较多[2][3][4],在本文中就不做过多的描述,主要的实现流程如图5所示。通过[2]中的一些典型算法,我们验证了本文所设计的汽车主动安全系统是完全满足汽车驾驶这种应用条件下的实时性要求的,而且该系统是具有较强的扩展性的。

4、结论

本文详细介绍了一套基于 DSP 计算和FPGA 逻辑计算的车道偏离预警系统的实现方案,主要解决了大容量图像数据在系统中的高速传输和存储、处理等。在设计的过程中,本文充分运用了FPGA 的逻辑资源对底层视觉算法的适应性及DSP 芯片的高速处理能力来满足高层的串行度高的视觉算法。通过一系列的实验,验证了该系统满足汽车安全这种应用背景下的高实时性要求。

3、系统软件算法

电子发烧友App

电子发烧友App

评论