01车载SoC芯片现状

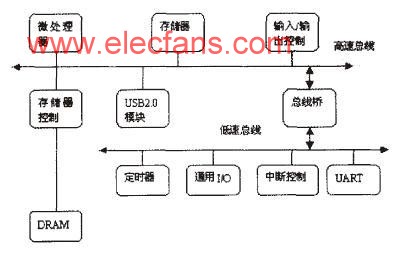

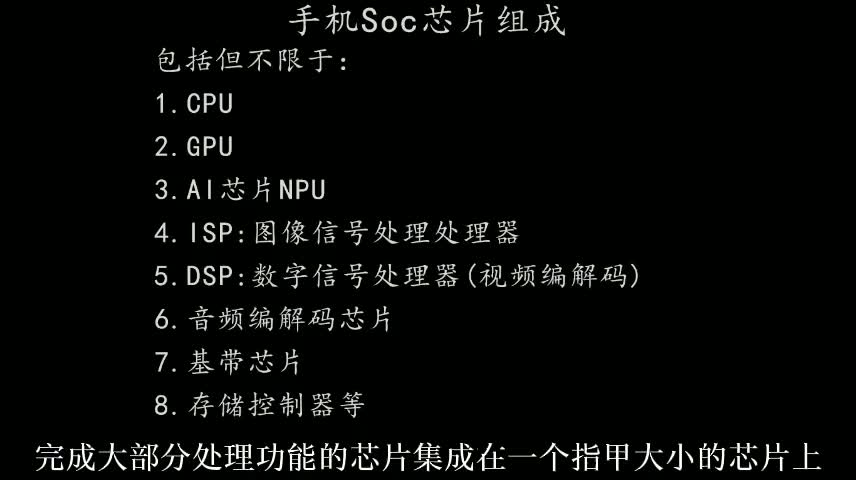

SoC的全称叫做:System-on-a-Chip,中文的的意思就是“把系统都做在一个芯片上”。这个概念最先是从智能手机发展起来的,通过将CPU、GPU、内存、Modem,ISP,DSP,Codec等系统部件打包集成在一颗芯片内,手机厂商就不需要分别单独采购这些功能芯片,从而带来节省主板空间、成本和功耗的收益,这对追求轻薄、长时间续航的手机来说非常具有吸引力。

SoC在汽车上的首次应用,首先是在智能座舱领域。随着智能座舱的发展,不仅需要强大的CPU算力来提高任务处理能力,强悍的GPU算力来处理视频、图片等非结构化数据,高效的AI 算力来满足智能座舱的智能化交互体验要求,高速的DSP算力实现大带宽实时通讯,还需要能操作系统兼容手机生态,从而快速提升娱乐体验。总之,智能座舱在4G通信、车载WFI、驾驶舱手势识别、高品质音视频处理、编解码、图像拼接等典型应用场景的需求跟智能手机的业务场景高度契合,所以凭借在消费电子、通信领域的技术实力和品牌优势高通在2014年基于骁龙600平台打造了骁龙620A车规级SoC芯片,取得了巨大的成功,截至目前高通的智能座舱SoC芯片已经演化到第四代SA8295。

在智能驾驶领域,海量帧图像处理极其考验芯片的并行计算能力,显然擅长逻辑和数字运算能力的CPU无法满足大量并行的简单运算任务,因此,在自动驾驶上通常使用了集成CPU 和XPU(GPU/NPU/TPU) 的SoC 芯片。随着智驾水平的发展,智驾SoC的算力也在不断提升,目前已经量产AI算力最高的智驾SoC是英伟达Orin。

由于智舱与智驾的场景并不相同,带来的算力侧重点也不相同,所以智舱SoC和智驾SoC很长一段时间内平行发展。在今年9月份,高通和英伟达几乎先后脚发布了自己的汽车超算芯片Thor(英伟达)和Snapdragon Ride Flex(高通),这两款芯片都可以同时支持智舱和智驾功能。业内不禁惊呼,是不是舱驾一体芯片的时代就要到来了。对此,笔者认为真正实现舱驾一体还需要有很长的路要走。

首先,是智舱和智驾的功能安全等级不同,如何打造一款同时兼顾不同功能安全等级的OS是一个挑战。

其次,真正舱驾一体要满足算力灵活分配,而Thor目前通过静态配置,一旦分配好了算力以后就无法根据场景进行切换。

第三,许多车企的组织机构里智舱与智驾分属不同部门,在一颗芯片里如何分工协作也是一场挑战,目前还没有成熟的经验可遵循。

因此,在未来一段时间内,智舱和智驾分属两个SoC还会是主流方案。

事实上无论是舱驾一体,还是智舱和智驾保持独立发展,要想搞清楚车载SoC未来发展方向是什么,就必须要先回答一个问题,车载SoC芯片的发展方向是由什么来决定的?

02汽车智能化的挑战

cao sir认为车载SoC芯片的发展方向是由整车电子电气架构发展来决定的!

电子电气架构是首先由德尔福公司提出的,集合汽车的电子电气系统原理设计、中央电器盒的设计、连接器的设计、电子电气分配系统等设计为一体的整车电子电气解决方案的概念,按照业内普遍采纳的博世定义,将电子电气架构分为分布式架构、域集中式架构、中央集中式架构三大阶段。近些年来,伴随着汽车“新四化”的快速发展,许多车企都从分布式电气架构迈进域集中式电气架构,有的甚至一步跨越到中央集中式电气架构,电子电气架构整体呈现快速演进的态势,这背后的原因就是汽车正面临着“减重降本”、“智能网联化”、“快速迭代”、“商业模式颠覆”四大挑战。

1、“减重降本”挑战,随着汽车上智能化功能越来越多,传统分布式架构会导致控制器数量繁多,成本和重量居高不下的问题。据统计,一辆基于传统分布式电子电气架构高端汽车的控制器高达70多个,整个电气系统重量80Kg。

2、“智能网联化”挑战,在新四化浪潮下,一辆智能网联汽车每天至少收集10TB的数据,对车辆内部、车辆与外界通讯提出更高要求,传统以CAN通讯为主干网的电子电气架构必然不能满足要求。

3、“快速迭代”挑战,传统的低内聚、高耦合的电气架构,可重用性、可拓展性差,开发周期长、成本高。未来市场是快鱼吃慢鱼的时代,传统的分布式电子电气架构低内聚,高耦合,新增加一个智能化功能需要许多控制器配合才能完成,不仅成本高,周期长。

4、“商业模式颠覆”挑战,原先的卖车+售后的盈利模式,向互联网“订阅”盈利模式转变,传统面向信号的电气架构显然无法支持这种“订阅”模式,所以衍生出了面向服务的SOA电气架构。

03车载SoC芯片的发展方向

为了满足上面的四大挑战,面向未来的新型电气架构必须具备“低能耗”、“可信可靠”、“高集成”、“可重用”、“可成长”、“高性能”、“低耦合”、“高开放”的八大核心特征。其中“高性能”、“低能耗”、“高集成”、“可信可靠”决定了车载SoC芯片的发展方向。

“高性能“

由于多屏互联、智能交互、智能驾驶等场景化功能对芯片性能有着极高要求。近几年来,智能座舱芯片的CPU算力提升相当明显, 仅用了不到7年的时间,从过去的数KDMIPS提升到如今的100多KDMIPS,。随着自动驾驶的发展,智驾芯片的AI算力也在大幅提升,通常业内认为实现L2级自动辅助驾驶需要的算力在10 TOPS以下,L3级需要30~60 TOPS,L4级需要超过300 TOPS,L5级需要超过1000 TOPS,甚至4000+ TOPS。

“低能耗“

据初步估计,一辆新能源车在CLTC工况下,每增加50w功耗会带来8~10Km的续航里程损失,因此,新型电子电气架构上对芯片能效比提出了更高的要求。降低能耗除了提升工艺纳米水平以外,从通用芯片转为某类算法“量身定做“ASIC芯片是一条前景广阔的途径。当前自动驾驶芯片使用GPU+FPGA的解决方案。未来算法稳定后,ASIC将成为主流。现阶段,主流产品的能效比已经由最初 0.8TOPS/W(EyeQ4)、1TOPS/W(Xavier),进化到了 4.44TOPS/W(英伟达 Orin)、4.8TOPS/W(地平线征程 5),未来主流产品功耗至少在 6TOPS/W 以上。

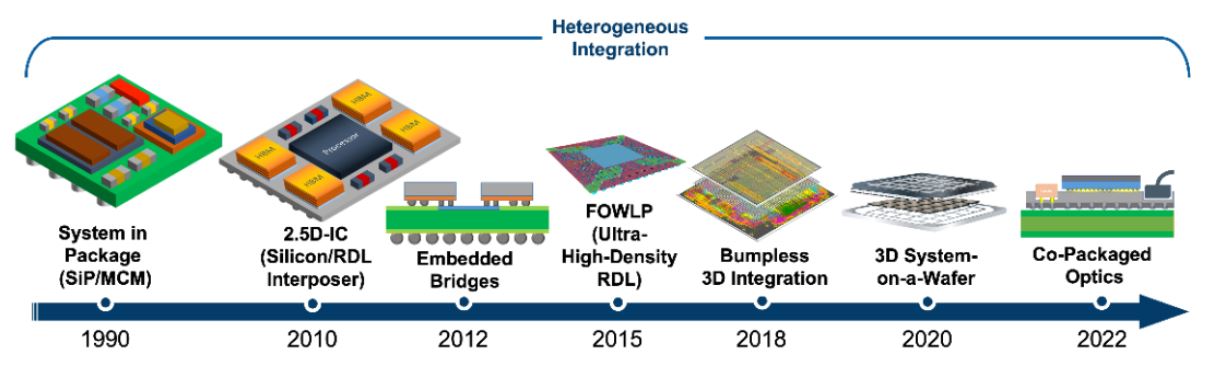

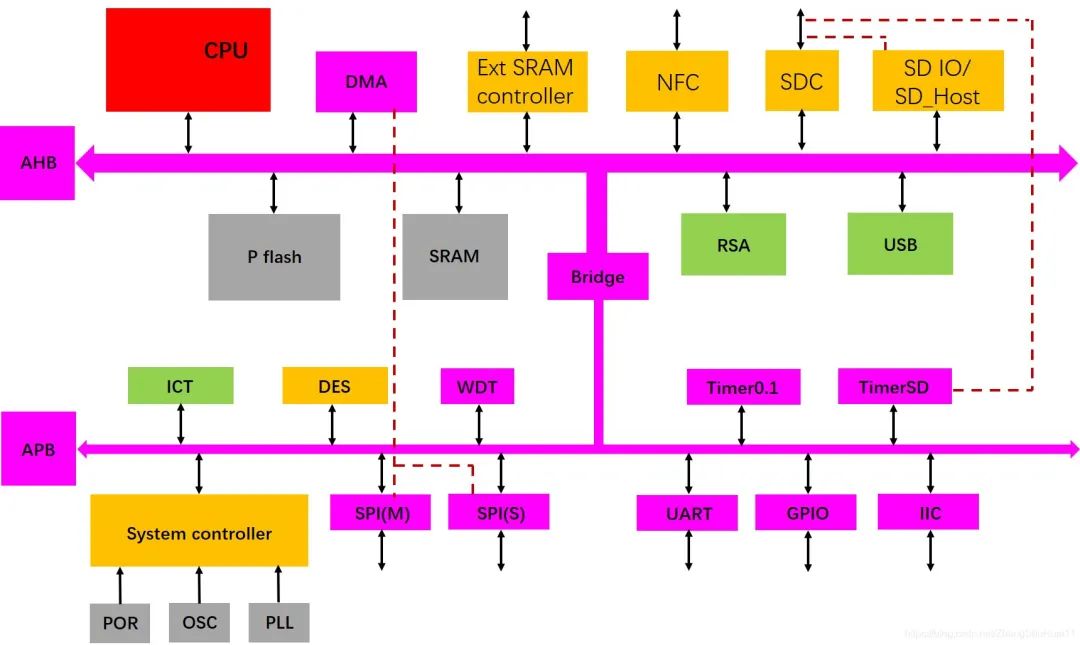

“高集成“

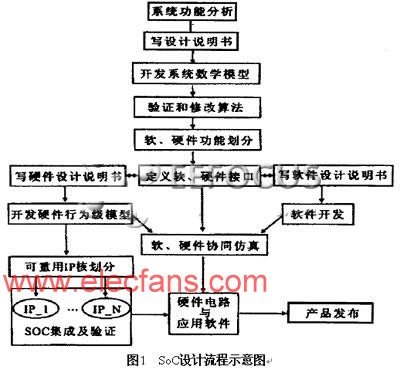

汽车电子电气架构(E/E架构)逐渐从传统的分布式向集中式演进。在集中式E/E架构下,新增的域控制器集成了更多的功能,主控芯片若要与其职能相匹配,则算力、性能等必须随之提升。在此趋势下,汽车芯片从通用型、分散化的单一功能芯片(MCU)开始逐步转向定制化、集成化的多功能SoC(System on Chip)芯片。SoC是系统级芯片,将系统关键部件集成在一块芯片上,提升性能的同时可有效地降低系统产品的开发成本,缩短开发周期,提高产品的竞争力。未来在中央集中式电气架构下,智舱SoC和智驾SoC芯片存在融合的趋势。

“可靠可信”

随着功能安全和网络安全的要求不断提高,SoC 芯片可靠可信是首要考虑的问题。可靠性技术的实现都是以容错为基础, 容错技术主要是依靠资源的冗余和系统重构资源的组织来完成。冗余主要包括硬件冗余、软件冗余、时间冗余、信息冗余等。硬件冗余是在常规的硬件功能设计之外再另加一些备用的附加的硬件, 当常规硬件发生错误时备用硬件起作用, 使系统仍然能够正常工作; 软件冗余是增加一些额外的用于检错纠错的程序, 当运行出错时程序能够自行进行检错纠错; 时间冗余是为某一指令或一段程序开辟额外的时间让其重复执行; 信息冗余是增加信息的多余度, 使其自己具有检错纠错的能力。

03国产SoC如何破局?

短期来看,凭借先发优势、朋友圈规模和迭代速度,高通和英伟达分别在智能座舱领域和智能驾驶领域尚未有人能与其棋逢对手,国产SoC如何在强敌环伺的竞争格局中破局,并与他们同台竞技?

首先要以紧紧围绕以用户需求为中心,打造创新管理流程。以自动驾驶AI芯片为例,当前市场上许多芯片公司都是基于自己算法开发的IP,用户买他们芯片就要同时使用他们的算法,有的芯片公司的产品甚至无法支持CNN+Transfomer算法,还有的芯片公司则会持续跟踪前言视觉学习算法,在设计过程中确保兼容,另外还通过软硬件协同设计,并提供工具链支持客户构筑自己的算法IP,从而为客户打造专属的运行效率更高的智驾SoC。

其次是打造高水平的技术团队。芯片行业本身就是一个系统性的工程,对专业学科的要求非常高且广泛包含但不限于数学、化学、物理、图像、光学等等。复杂性和广泛程度,更考验各位工程师们扎实的理论基础和出色的工程落地能力!因此与之对应的工作内容合理划分和优质的人才是芯片设计公司的重要灵魂,也是打造芯片正向开发的能力的基石。

第三,对智舱芯片来说,随着车内元宇宙、非触摸式交互,舱泊一体等一系列智能座舱场景落地,智能座舱SoC的算力发展整体向PC看齐趋势,当前市场上主流的座舱芯片未来将会被更高算力的SoC所取代,在新旧交替的过程中追求极致算力的智舱SoC芯片将会获得市场青睐。

第四,对智驾AI芯片来说,算力在不断提升同时带来了功耗、成本和面积的大幅提高,因此单纯依靠芯片算力堆叠是无法解决智能驾驶系统计算平台的支撑问题,笔者认为算力的无限膨胀不会是未来的趋势,与动辄上千TOPS的算力相比,精准高效的AI算力以及更好的软件是培训显得更为重要,为车企节约开发周期与成本。

狄更斯在《双城记》中说过:“这是一个最好的时代,也是一个最坏的时代。”,在新型电子电气架构变革的过程中,车载SoC市场格局将发生深刻变化,未来到底谁主沉浮,目前下结论还为时尚早,但是cao sir认为,那些围绕用户需求为中心,深耕技术的芯片企业,一定会有更多的机会!

编辑:黄飞

电子发烧友App

电子发烧友App

评论