3.1. ZEDBOARD的控制输入IP

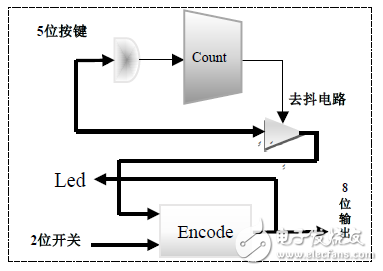

该IP设计主要完成对5个按键以及2个开关状态的检测及编码,使产生8位编码数据,用以传送给XPS构建的子系统的8位GPIO,以axi_lite相关协议映射编码数据,从而将编码输入传送到了PS (Processing System: ARM处理器)部分,用以软件编程检测和处理。

该设计的实现原理如图6所示,通过计数模块Count实现按键状态的去抖检测,两个按键用于缩放算法选择,并用三个Led的二进制实时显示,另两个按键用于选择缩放倍数,一个按键用于录入状态与完成录入状态间的切换;两个开关则分别控制放大/缩小、显示使能。

3.2. WLI算法IP

3.2.1. Axi4接口

Axi4 [8] 是由Xilinx和ARM合作提出的便于全可编程器件内部ARM和FPGA之间数据的高速通信的总线标准。Zedboard内部使用Axi4,可细分为Axi_lite、Axi4、Axi_stream三大类,包含地址、数据和反馈通道。能实现ARM和FPGA内部的高速并行数据通信,并支持DMA (direct memory access)通信。

3.2.2. 符合Axi4接口的WLI算法IP

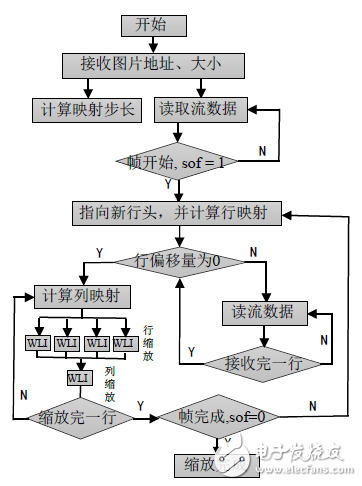

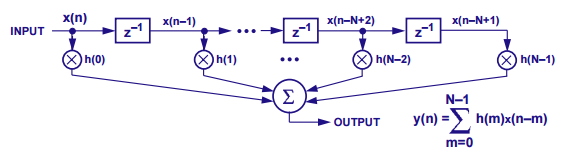

Vivado HLS是Xilinx针对其全可编程器件而推出的高级综合组件,该软件可以实现对C语言编写的程序的直接硬件化,并能很好的综合出符合Axi标准的IP [9] - [12] 。本文的设计采用这种设计方法,借助OpenCV的MAT的相关内容、要求,编写可综合算法程序,图7是WLI算法的实现流程。

映射策略确定新图中的一行在原图的行位置,通过每次缩放一行新图数据的基本策略,用四个数组(Bram存储)缓存与映射行相关的四行原图点值,从而实现算法的二维缩放。WLI子模块实现对一维4个相关点的算法缩放,通过先行后列的策略实现个相关点的图像缩放目的。

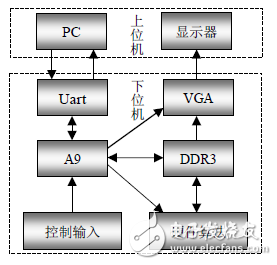

图5. 缩放算法硬件系统架构

图6. 控制输入IP结构框图

图7. WLI算法流程

3.3. 硬件系统搭建

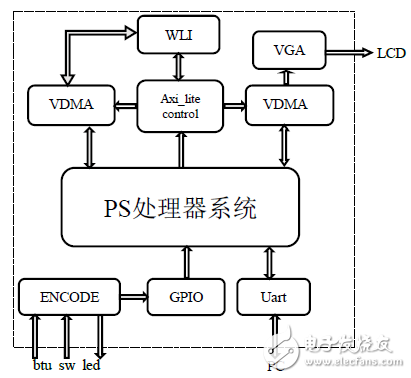

HLS综合出算法的硬件IP后,通过Planahead环境完成整个硬件系统的搭建。图8为系统结构示意图,该系统包括PS子系统、内存间以HP通道(DDR内存和FPGA间的高宽带、高速数据通道)直接进行数据通信的VDMA、GPIO等IP,以及自主设计的WLI算法IP和VGA显示IP [13] 。

4. 软硬协同验证实验

4.1. 软件原理

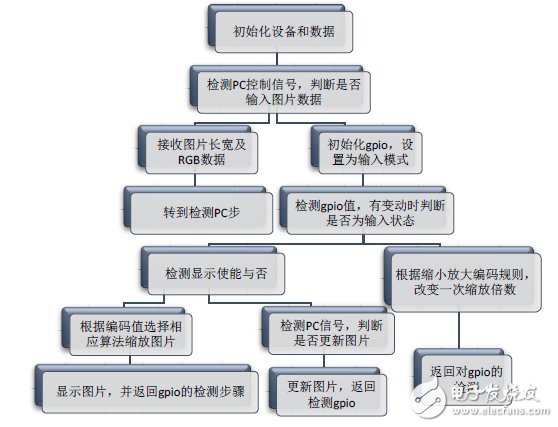

在硬件系统搭建完成以后,借助于Xilinx的SDK集成环境进行软件设计。图9是整个软件设计运行的流程图,主要分为初始化、原始图片选择接收存储、GPIO初始化、缩放倍数检测统计、按键状态检测判断和相应算法处理及对比显示等。

软件设计中,通过接收PC的选择信号,选择使用预定义的图片,或接收从PC传来的新图片。然后进入循环检测和缩放处理过程,便于演示。同时,通过显示使能控制端,可以再次更新PC的显示数据。而缩放显示模式不仅决定缩放的算法选择(软件或硬件),还决定显示模式(单一还是对比显示)。

当检测到GPIO为倍数录入状态时,应当进入倍数的检测和相应操作模式,由此可实现0.1精度的任意倍数图像缩放效果,并能够对基于不同缩放算法得到的图片进行对比显示。

4.2. 软硬件协同验证

通过SDK将编译好的bootloader程序、FPGA配置bit文件和裸机程序封装成boot.bin文件,以SD卡实现Zedboard的脱机演示系统。其验证实验的系统如图10所示,右图是双三次插值算法软件缩放结果,而左图则是WLI算法硬件缩放图。

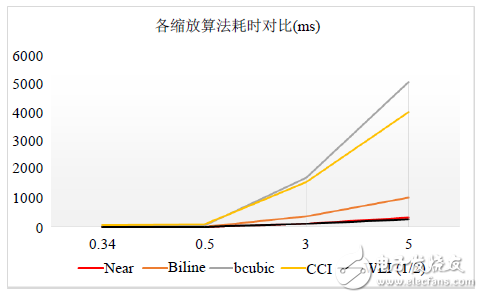

各缩放算法在ARM裸机上缩放图片所耗用时间 [14] 的对比结果如图11所示。其中最近邻(Near)、双线性(Biline)、双三次(Bcubic)和CCI等为软件缩放算法,WLI算法为硬件实现算法。

尽管软件缩放算法在约667 MHz的Cortex A9处理器上运行,而通过FPGA硬件化的WLI算法的运行时钟仅为100 MHz,但图11的结果表明,其缩放耗时仍同最近邻算法相当(Near几乎被WLI覆盖了),可见在相同时钟条件下,其计算效率将会大幅提高,体现硬件实现的并行特征。

图8. 硬件系统结构

图9. 软件处理流程图

图10. 图像缩放对比显示演示系统

图11. 各缩放算法不同倍数耗时对比

5. 结论

本文主要研究了时域图像缩放算法中比较常用的几种缩放算法,并基于一种称为WLI的图像缩放算法,在Xilinx的全可编程器件开发板Zedboard上实现了算法的硬件化,并构建了软硬协同验证系统,实现了脱机演示。

本文设计的IP实现了硬件图像缩放,并与基于软件实现的图像缩放具有相同效果,而计算效率提高了至少一个数量级,充分体现了硬件实现图像缩放的优异性和可行性。

参考文献 (References)

1. Choi, B.-D. and Yoo, H. (2009) Design of piecewise weighted linear interpolation based on even-odd decomposition and its application to image resizing. IEEE Transactions on Consumer Electronics, 55, 2280-2286.

2. 刘婧 (2009) 图像缩放算法的研究与FPGA设计. 硕士论文, 上海大学, 上海.

3. 李秀英, 袁红 (2012) 几种图像缩放算法的研究. 现代电子技术, 35, 48-51.

4. Wang, J. (2011) MATLAB三种程序耗时算法.

5. 心海 (2013) PSNR定义与计算.

6. Li, X. (2002) Blind image quality assessment. IEEE ICIP, 1, 449-452.

7. Xilinx (2014) Zynq-7000 all programmable SoC. Xilinx数据手册.

8. Xilinx (2011) Xilinx, AXI reference guide UG761 (v13.1) March 7. Xilinx数据手册.

9. 马建国, 孟宪元 (2011) FPGA现代数字系统设计. 清华大学出版社, 北京.

10. 仆居 (2013) AXI-Stream接口开发详细流程.

11. 何宾 (2011) 基于AX14的可编程SOC系统设计. 清华大学出版社, 北京.

12. 何宾 (2011) Xilinx all programmable Zynq-7000 SOC设计指南. 清华大学出版社, 北京.

13. 开源硬件社区 (2009) VGA驱动及实现.

14. Cuter (2013) 如何在SDK中计算某段程序的执行时间.

电子发烧友App

电子发烧友App

评论