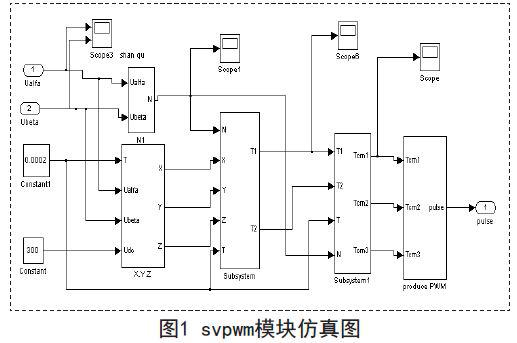

本文建立了基于svpwm变频调速的双电机偏差耦合控制算法的仿真模型,并用Matlab7.1仿真软件进行了仿真,对仿真结果做了分析和比较。

2018-10-24 08:05:00 10535

10535

你好: 我是一个购买的帐户,所以我的许可证应该允许访问所有内容。但是当我使用System Generator for DSP时,系统说我的SysGen签出许可证失败了。有人知道怎么解决吗?谢谢

2019-01-28 07:16:36

错误:System Generator for DSP(SysGen)的许可证签出失败。无法联系Xilinx许可证管理器。请检查以下内容:(1)XILINX环境变量指向有效的ISE安装(2

2018-12-29 10:35:12

FPGA中的数字控制器是什么?System Generator中的PID控制器是如何设计的?

2021-04-08 06:51:46

大家好,这是我第一次使用System Generator工具,如果有人能够解决一个不让我继续参与我的硬件协同仿真项目的问题,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根据我的理解,System Generator是MatLab到RTL的转换,因此不包括Vivado的优化过程。问题1--是真的。确实,Vivado中的优化将大大改变系统描述,而系统描述不会向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天评估包,Matalb 2014B。简单地说我想使用FIR编译器,当我尝试编辑它的参数时,我得到了两个错误: - 1.“来自MEX

2020-03-24 09:01:59

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何时才能胜任64位Windows 7?以上来自于谷歌翻译以下为原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,发现getway in这个模块参数设置变化导致MATLAB闪退问题,贴图如下其中getway in 这个模块数据类型换成定点有符号或者无符号数都不得行,换成布尔值又会出现错误,不知为何啊!求教。

2018-01-05 21:43:53

翻译成verilog,在FPGA里面实现,即system generator。altera有没有类似的接口,与matlab可以互连,直接在matlab里设计我所需要的算法,在翻译成verilog?

2015-01-14 14:20:50

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

国内外近些年的研究热点。本项目旨在采用时频分析算法提取放电脉冲特征量,通过仿真、编写软件验证算法的实用性,并硬件(dsp)实现算法并应用

2015-10-09 15:10:00

………………………………………… 1205.1.4 基于反正切函数的仿真建模与结果分析…………………………… 1225.1.5 基于锁相环的仿真建模与结果分析………………………………… 1225.2 自适应滑模观测器算法

2019-12-03 14:59:13

针对实现DSP的设计软件—System Generator。在使用FPGA为原型平台运行算法时,它不仅能够对硬件的真实情况进行仿真,还能够自动生成硬件实现所需要的硬件描述语言代码。与语 言设计相比

2019-06-21 06:25:23

各位好,最近在使用system generator 搭建一个ifft设计模块,使用ise调用,但是在下载到板子后,示波器输出波形去在没有输入的情况下仍然有波形,确定不是噪声,波形还是很规律,求解释呀!

2016-07-13 13:21:30

使用system generator导入xilinx模块时,只要连线两个模块,matlab就崩溃,有知道原因的大佬吗?

2018-01-19 17:54:57

.Vivado 2016.4与Spartan-6不兼容。据Xilinx称,Vivado不支持任何早于7系列的设备系列。)根据以下说明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在内部,有一个基于VHDL的框架,它将定制板上的不同部分与“DSP内核”连接,后者是在System Generator下开发的。在这

2019-01-15 10:39:11

在system generator中,我把(-128~127),变为(-1~1),但是下载到硬件中,使用chipscope抓取到的数据确实(-128~127),请问是怎么回事

2016-08-10 15:32:38

有做System Generator处理图像的吗?遇到一些问题,一起商量下

2020-09-28 19:04:58

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

你好,我有兴趣使用Artix-7 FPGA进行以太网协同仿真(在Simulink中通过System Generator)。在System Generator中,我看到AC701

2020-07-15 08:45:40

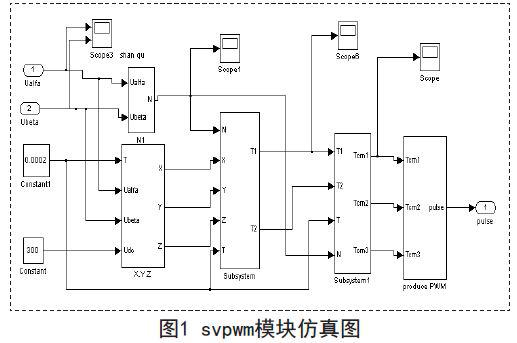

SVPWM算法的原理是什么?SVPWM算法如何去实现?如何对SVPWM算法进行Simulink仿真?

2021-08-04 06:29:27

各位大佬,我在安装System Generator时,跟着教程走,发现在vivado中没有出现System Generator for DSP这个选项,请问是我哪里安装得不对吗?

2023-09-26 21:54:58

当我完成SDx 2017.2的安装时,没有安装System Generator的选项。我正在运行从Xilinx下载的安装程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator创建一个双向(inout)端口。我正在尝试为Xilinx的外部存储器创建一个接口

2019-05-09 14:36:24

最近在使用system generator设计一个rs编码译码的模型,总的思想是在rs编码产生信号后,插入一个误码,然后作为信号源进行解码,看是否能够正常的进行解码,求解是怎么才能把rs编码后的信号存储起来作为信号源

2016-07-20 20:13:59

如何去设计一款合理的电子硬件解决方案,从而实现经济有效的大规模生产与部署?怎样去验证可部署目标硬件与软件算法模型之间的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

有用Xilinx的system generator做图像处理的嘛?求交流 。我正在用这个做图像处理,已经用了3个月了,在做一些算法,遇到一些困难,求一起交流学习。发现用这个开发的人真不多啊。

2014-05-09 14:57:21

非常苦恼,刚开始学习system generator,用带光盘的书上的例子,想要学习一下设计流程,结果屡屡碰壁。在搭建好系统,点击开始仿真之后,总是会出错。在别人的电脑上就能仿真成功,一开始认为是

2016-07-13 23:12:36

在红外线的增强处理中,怎么用quartusII进行算法的实现及其仿真验证,重点是直方图算法,这里面的代码是什么。

2015-05-06 23:01:22

xilinx公司的网络教程“利用 System Generator 进行 DSP 设计”谁有?上传一份给小弟吧

2013-03-14 12:17:03

仿真分析 8.1.仿真电路分析 信号输入:幅值为2,频率为50Hz的三相正弦波信号 SVPWM算法实现:载波为20KHz的三角波,三相逆变电路的直流侧电压为24V PWM信号生成:载波为

2023-03-06 17:00:53

以前,我们有Matlab 2006a和ISE 8.2i,并且正在使用System Generator。我们不得不重新安装Matlab 2006a以启用新的工具箱,但现在Simulink中没有

2018-11-19 14:42:56

小波盲源分离算法的仿真及FPGA实现:提出了一种基于小波变换的盲源分离方法,在理论分析和仿真结果的基础上,给出了FPGA 的实现方案。针对传统盲分离算法对源信号统计特征敏

2009-06-21 22:44:09 21

21 本文基于软件无线电的思想,对MQAM 调制进行算法和仿真的研究。采用System Generator 搭建MQAM 调制系统模型,将算法转换成了硬件可实现模块,对该系统进行了完整的仿真及仿真分

2009-12-14 14:28:48 24

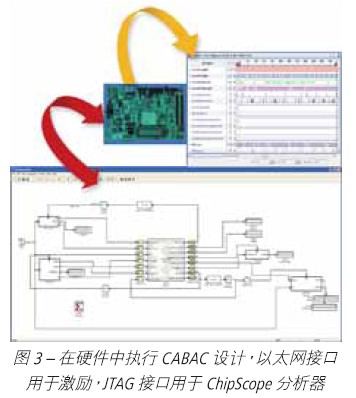

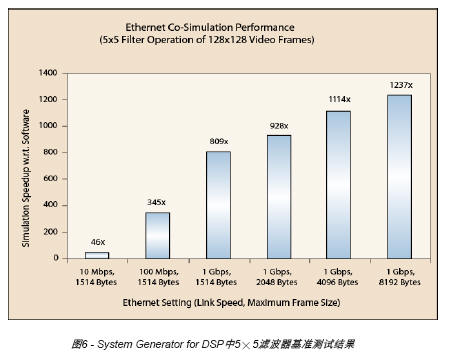

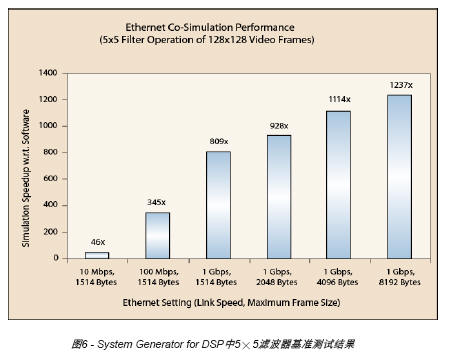

24 采用以太网硬件在环路实现高带宽DSP仿真设计

System Generator v8.1提供全新的千兆位级以太网硬件在环接口,支持使用Xilinx ML402 FPGA平台进行高带宽协仿真

通

2010-03-05 09:13:10 27

27 SYSTEM VIEW教材

SYSTEM VIEW是一个用于现代工程与科学系统设计及仿真的动态系统分析平台。

2010-04-10 11:08:05 32

32

采用Gardner算法,对QPSK调制解调系统中的位同步系统进行设计与实现,大大提高了系统性能和资源利用率。重点阐述采用FPGA开发环境System Generator系统设计工具进行位同

2010-07-21 16:12:40 26

26 软件仿真频率细化过程的分析与实现

介绍频率细化过程,并对移频法频率细化(ZOOM)过程中的几个问题进行了分析,最后介绍用MATLAB语言仿真频率细

2009-12-08 15:19:57 672

672

深入了解赛灵思System Generator中的时间参数

基于模型的设计(MBD)因其在缩小实时系统抽象的数学建模和物理实现之间差距方面的光明前景而备受关注。通过使用相同的

2009-12-29 11:40:30 1300

1300

HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够

2010-01-06 14:39:30 1181

1181

通常情况下,在设计基于FPGA的大型信号处理系统的时候,设计人员往往需要进行费时费力的仿真。以Xilinx System Generator for DSP为代表的FPGA设计工具,通过提供可靠的硬件在环接口(

2010-07-10 12:18:07 583

583

针对网络数据流存储的瓶颈问题,提出了一种网络数据流存储算法分析与实现方法,仿真结果表明,模型能显著提高网络数据流的实时存储能力

2011-05-26 15:57:33 21

21 该设计是基于System Generator设计平台,在Matlab/Simulink环境下搭建系统模型,再进行功能仿真和验证,完成QPSK调制器的设计。仿真结果表明,所设计的调制器能产生正确QPSK波形,达到了预期效果

2011-10-17 16:10:51 65

65 通过对P码产生机理的分析,利用MATLAB对算法进行了仿真实现。仿真结果表明,采用该算法能够产生任意时刻、长度的P码。利用产生的P码数据,对其相关特性等进行了分析,从而进一步

2012-05-08 15:40:11 55

55 本文首先对CIC、HB、FIR滤波器的原理及设计作了简单的说明,最后用Matlab结合System generator对本文所设计的DDC滤波器作了一个仿真。

2012-08-06 15:34:48 10298

10298

Xilinx公司推出的DSP设计开发工具System Generator是在Matlab环境中进行建模,是DSP高层系统设计与Xilinx FPGA之间实现的桥梁。在分析了FPGA传统级设计方法的基础上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 SVPWM算法仿真实现及分析,有需要的下来看看

2016-04-14 17:06:44 9

9 Xilinx FPGA工程例子源码:System Generator的设计实例

2016-06-07 14:41:57 22

22 自适应神经模糊算法在光伏MPPT中的仿真分析_荣德生

2017-01-07 18:56:13 0

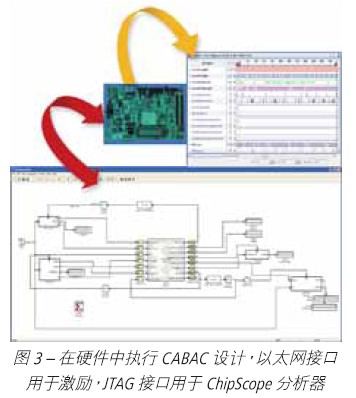

0 环境 Matlab 2014 a Vivado 2014.4 System generator 2014.4 实现步骤 1、模型搭建与仿真 在simulink环境下工程搭建如下 图3 四路加

2017-02-08 01:10:08 473

473

最新版System Generator支持快速开发和实现基于All Programmable FPGA、SoC和MPSoC的无线电设计 赛灵思日前宣布推出高级设计工具System Generator

2017-02-09 01:23:41 279

279 一直都在System Generator下做图像处理相关的算法,感觉SysGen挺强大的,前几天突发奇想,能否直接用SysGen实现数据的通信呢,毕竟一句HDL代码都不写对于做FPGA的人来说却是很有吸引力的。

2017-02-10 19:51:11 2619

2619

前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53:11 3779

3779

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21:33 7392

7392

通常情况下,在设计基于FPGA的大型信号处理系统的时候,设计人员往往需要进行费时费力的仿真。以Xilinx System Generator for DSP为代表的FPGA设计工具,通过提供可靠

2017-10-23 15:00:24 0

0 利用System Generator软件平台,实现基于模块化建模方法的变换器建模,并简化语言编写控制系统的复杂过程。研究了从MATLAB-Xilinx环境中导出使用模块化建模方法搭建的控制算法。通过

2017-11-15 14:31:34 4985

4985

LTE System Toolbox 提供用于设计、仿真和验证 LTE 和 LTE-Advanced 通信系统且符合标准的函数和应用程序。该系统工具箱加速了 LTE 算法和物理层 (PHY) 部署

2017-11-16 15:44:01 4039

4039 现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29:06 7299

7299 基于System Generator软件,在xc7z020-1clg484芯片上设计了一种高速盲均衡器。该盲均衡器由延迟模块、滤波模块、误差计算模块和系数更新模块构成,采用MCMA算法,使用并行

2017-11-18 05:06:01 1881

1881

Xilinx System Generator 是专门为数字信号算法处理而推出的模型化设计平台,可以快速、简单地将DSP系统的抽象算法转换成可综合的、可靠的硬件系统,弥补了大部分对C语言以及Matlab工具很熟悉的DSP工程师对于硬件描述语言VHDL和Verilog HDL认识不足的缺陷。

2018-07-19 09:32:00 3716

3716

本文在分析Rife,MRife和傅里叶系数插值迭代3种算法的基础上,将串行迭代变为并行迭代,由此得出了一种快速频率估计算法,并分析了新算法与前3种算法的异同。计算机仿真结果证实新算法能够快速、高精度估计单频信号的频率,便于工程实现,适合应用在雷达、电子对抗等对处理实时性要求非常高的领域。

2017-11-23 15:36:00 8831

8831 PLD/FPGA 常用开发软件System Generator 9.10。 业内领先的高级系统级FPGA开发高度并行系统。

2017-11-26 11:34:56 12

12 本视频产品演示介绍了 Xilinx 系统生成器(System Generator)和 Xilinx ISE® 项目浏览器(Project Navigator)设计环境之间的新整合。

2018-06-06 13:46:00 3024

3024

新的System Generator,算法开发人员可在其熟悉的MATLAB和Simulink模型化设计环境中创建生产质量级的DSP实现方案,而且相校传统 RTL 可大幅缩短设计时间。最新版提供了更高级的设计抽象,并可通过新型的模块集中、更快的仿真和编译运行时间,将无线电算法的设计生产力提高7倍。

2018-08-20 10:13:00 763

763 了解如何将Vivado HLS设计作为IP模块整合到System Generator for DSP中。

了解如何将Vivado HLS设计保存为IP模块,并了解如何将此IP轻松整合到System Generator for DSP的设计中。

2018-11-20 05:55:00 2941

2941 了解如何在System Generator中使用多个时钟域,从而可以实现复杂的DSP系统。

2018-11-27 06:42:00 3450

3450 了解如何使用Vivado System Generator for DSP进行点对点以太网硬件协同仿真。

System Generator提供硬件协同仿真,可以将FPGA中运行的设计直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

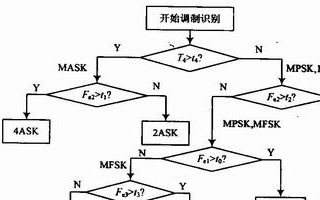

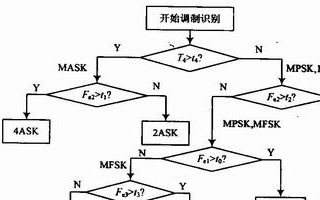

4262 中识别率不高,而基于人工神经网络的识别方法计算复杂度较高。信号的高阶累积量算法具有很好的抗噪性能,故对基于高阶累积量的通信信号调制识别算法的研究受到了广泛重视。文献利用高阶累积量实现了对 2ASK

2019-03-14 10:32:58 1573

1573

System Generator 数字上下变频 (DUC/DDC)模块集的易用性大幅提升,使得更加便于无线算法开发。这些新型模块还添加了有助于加速验证和编译运行时间的增强功能,所有这些模块提供了七八种参数设置。

2019-07-31 09:22:49 2293

2293 当用Matlab完成数字信号处理算法仿真后,如何在DSP芯片上实时实现,是电气信息类大学生需要掌握的一项重要的工程实践能力。在仿真过程中,有算法移植、DSP工程建立和算法实现这三个关键环节。本文介绍

2020-09-10 16:08:12 32

32 Rife算法的基础上,通过对输入信号进行频谱搬移,给出了一种修正Rife(MRife)算法.该算法易于并行实现。Monte Caro仿真表明,MRife算法具有频率估计精度高、整个量化频率范围内性能

2021-03-30 11:28:54 7

7 根据椭圆曲线密码体制的几种关键算法,采用Modelsim仿真工具设计相应的算法模块。然后将各模块代码通过System Gene

2021-06-12 10:17:00 1294

1294

用Systemview实现对QPSK系统的仿真与分析(测试测量计量的区别)-该文档为用Systemview实现对QPSK系统的仿真与分析讲解文档Systemview 是一种基于 windows 平台

2021-09-30 12:16:15 11

11 本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

./oschina_soft/arXiv2020-RIFE.zip

2022-06-07 14:17:18 2

2

电子发烧友App

电子发烧友App

评论