资料介绍

1引言

TMS320VC54211、2(以下简称VC5421)是TI公司推出的一款双核定点DSP芯片,它拥有两个DSP子系统,每个子系统都有一个DSP核,并且均有独立的数据和程序存储空间,可以进行两核之间的通信,并且两个子系统共享一套片外总线。

此外,每个子系统各自拥有2k 16bit字的片内ROM,并存储有Bootloader程序。当DSP芯片上电或复位时,两个DSP核可分别启动自身独立的Bootloader程序,以实现用户程序的上电自举。

双核DSP自启动和单核DSP自启动的实现方法有较大的差别,这一点在DSP系统设计中需要特别注意。本文对双核DSP芯片VC5421的引导模式进行了深入的分析和研究,给出了使用16位并行引导模式进行双核DSP引导的实现方案。

2 TMS320VC5421的Boot模式

VC5421可提供16位并行引导、8位并行引导和串行EEPROM引导等三种Boot模式来实现用户程序的上电自举。

其中16位并行引导模式是通过片外存储器接口(EMIF)以DMA方式将代码从16-bit字宽的片外数据存储器搬移到片内程序存储空间;

8位并行引导模式则是通过片外存储器接口(EMIF)以DMA方式将代码从8-bit字宽的片外数据存储器搬移到片内的程序存储空间;

而串行EEPROM引导模式主要是通过多通道缓冲串口2(McBSP 2)从主设备中搬移代码并实现上电自举。

和54系列中其它芯片不同的是,VC5421片内ROM中的Bootloader程序并不支持HPI、并行I/O和标准串口模式的自启动方式。在其所支持的三种boot模式中,16位并行引导模式是最常用的。本文对这种模式进行了深入分析,给出了使用该模式进行双核DSP程序引导的方案,并通过实验验证了该方案的正确性。

2.1 并行引导模式的选择

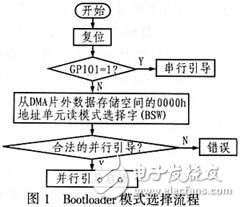

VC5421的两个DSP核在DSP芯片上电或复位时,到底以哪种模式实现上电自举,主要由两个核的公共引脚XIO和各自的GPIO0/ROMEN、GPIO1引脚决定。当XIO为0(低电平)时,将不从ROM引导,也就是说,将不使用VC5421片内ROM中的Bootloader程序实现上电引导,而是用HPI模式实现上电自举;当XIO为1(高电平),GPIO0/ROMEN为0时,将使用片外存储器中用户自己编写的Bootloader程序实现上电自举;当XIO为1 GPIO/ROMEN为1 GPIO1为0或1时,将分别使用并行或者串行引导模式实现上电自举。因此,在实施相应的上电自举前,必须将引脚状态设置正确,以保证Bootloader程序按预定的模式执行。Bootloader模式的选择流程见图1。

当Bootloader程序检测到并行引导模式时,程序将以DMA方式从片外数据存储区的0000h单元取出模式选择字(BSW)来进一步决定是8位还是16位的并行引导模式。10AAh意味着选择了16位并行引导模式,而如果选择8位并行引导模式,取出的两个字节将是08h和AAh。之后,程序将按照Boot表进行加载。图2是并行引导模式的选择流程。

2.2 16位并行引导模式的Boot表

Bootloader程序要搬移的代码必须组织成一定的格式,这就是Boot表。16位并行引导模式的Boot表如表1所列。

表1 16位并行导模式Boot表

此外,需要注意的是,由于在多数程序中都有跳转指令或循环指令,所以,Boot表中的程序入口地址必须和程序的cmd文件中分配的地址保持一致,也就是说,当在CCS中进行调试时,如果程序Load到5000h,Boot表中的程序入口地址就应该是5000h。

2.3 Boot表的生成

Boot表可由hex500格式转换工具生成,也可以自己编写一个文件格式转换程序来把.out文件转换成所需的文件格式。本设计通过编写一个C++程序来将.out文件转换成.hex文件,然后再在文件的开始处增加相应的标志位和寄存器设置字,从而形成完整的Boot表。

3 VC5421片外总线冲突的解决方案

由于VC5421是双核DSP,每个核有各自的存储空间和Bootloader程序,但两核共享一套片外总线和一个XIO引脚。这样,当两核的复位引脚A_RS和B_RS同时收到复位低电平信号时,将同时申请片外总线的控制权。这就造成了申请片外总线的冲突。而且Bootloader程序总是检查该核有没有片外总线的控制权,如果没有,将循环检查直到取得片外总线的控制权。为了避免这种情况的发生,应该以合理的顺序给两个核上电。

由于VC5421中A核带有用来控制时钟频率的锁相环电路,所以应该先对A核进行复位,再启动A核,然后利用A核的用户程序来控制B核的复位,以实现两个核的启动。

根据系统需要,本设计使用Altera公司的CPLD芯片来产生各种控制信号。其电路连接示意图如图3所示。A核的复位信号A_RS由CPLD芯片直接给出,并在系统上电或复位的同时对A核进行复位。而B核的复位信号B_RS则通过CPLD映射到DSP的I/O空间0000h地址单元的第6位:B核复位控制位(在系统复位后值为0)如图4所示。在A核启动后,通过用户程序写B_RS位可为B核提供复位信号。

4 VC5421的并行引导自启动操作

4.1 用户程序的搬移

两个DSP核要完成各自的功能,执行的用户程序是不尽相同的,而且A核的用户程序还要控制B核的复位,因此两个DSP核的Boot表内容是不同的。由DMA方式内部存储器图可知,程序空间的第0页和第1页属于A核,第2页和第3页属于B核。因此,需要注意的是,当Bootloader程序搬移用户程序时,A核的用户程序要被搬移到内部程序空间的第0页上,而B核的用户程序则要被搬移到第2页上。于是B核Boot表中的程序入口XPC和目的XPC应被设置成0002h。

4.2 Boot表的放置

本系统用4Mbit(256k×16)FLASH器件SST39VF400A作为片外数据存储器。页选信号由DSP通过CPLD给出,并且映射到DSP中I/O空间的0000h地址单元的低5位(系统复位后5位均为0,即第0页)。如图4所示。另外,此地址单元的第5位(CFG位)是控制FLASH映射的配置位。当CFG为0时,FLASH被映射到DMA片外数据空间的0000h,此时,Bootloader程序可以以DMA方式从FLASH中搬移数据并进行自启动;当CFG为1时,FLASH被映射到CPU片外数据空间的8000h,在这种情况下,可以通过程序向FLASH中烧写数据。因此,这一位在系统上电或复位后将被设置成0,以使A核能够顺利启动。

由于两个DSP核的Boot表内容不同,故应视Boot表的大小,将两个Boot表放到FLASH的不同页上,以便对两个核分别实行引导。本设计将A核的Boot表放到第0页,将B核的Boot表放到第1页。

4.3 外总线控制权的释放

如图5所示,在GPIO控制寄存器(地址3Ch)中,XIO_GRANT位为1代表相应的DSP核取得了片外总线的控制权;而在还没有取得控制权(XIO_GRANT位为0)但在申请片外总线的控制权时,相应的XIO_REQ位应置为1;CORE_SEL位用于表示程序在哪个核上运行,当在CPU A上运行时,读A核的GPIO控制寄存器的CORE_SEL位将返回到“0”,而当同一个程序在CPU B上运行时,读B核的GPIO控制寄存器的CORE_SEL位将返回到“1”。有关GPIO控制寄存器的其它相关位,设计时可查阅有关的参考文献1。

4.4 FLASH的烧写

笔者根据SST39VF400A的资料编写了一个DSP程序,该程序可同时将A核的Boot表烧写到FLASH的第0页,而将B核的Boot表烧写到第1页。

在系统上电或复位后,A核首先运行它的Boot-loader程序(此时FLASH的第0页映射到DMA片外数据空间的0000h地址单元),A核启动后执行用户程序。用户程序首先将页选设置成第1页,这样,FLASH的第一页将被映射到DMA片外数据空间的0000h;然后,A核释放片外总线控制权,并给B核发出复位信号,此时由于只有B核复位,且A核已释放片外总线的控制权,因此,B核将申请到片外总线控制权,同时执行Bootloader程序的启动以完成整个DSP引导。完整的启动过程流程图如图6所示,下面是A核的启动测试程序代码:

- DSP+ZYNQ双核通信案例开发手册

- 基于ARM7和DSP双核控制的逆变电源设计

- 内置MCU和DSP的双核SOC芯片JMT1801ED数据手册 21次下载

- 内置MCU和DSP的双核SOC芯片JMT1808R数据手册 24次下载

- 多DSP并行系统设计方案解析 0次下载

- 基于双口RAM芯片实现DSP系统与ICCD并行接口的设计方案解析 2次下载

- TMS320VC5416DSP并行自举方案的设计与实现 12次下载

- 基于DSP_ARM的双核结构数字视频监控系统设计 2次下载

- ARM与DSP双核系统中的通信接口设计_赵学亮 7次下载

- 基于ARM7和DSP双核控制的逆变电源设计 24次下载

- 闪烁存储器DSP并行引导装载方法 41次下载

- C5402 DSP芯片自举引导方法的分析与研究 35次下载

- TMS320VC5402 DSP的并行I/O引导装载方法研究 43次下载

- DSP并行引导方法在氢钟自动调谐系统中的应用 21次下载

- 基于双DSP的高压无功补偿装置设计与实现

- 双核cpu和单核cpu的区别 3505次阅读

- 双核dsp和单核dsp的区别 951次阅读

- RTOS实现双核MCU消息通信 1109次阅读

- 先楫HPM6000系列MCU双核的通信方式和资源分配 3693次阅读

- Intel Arc显卡可以双卡并行吗? 1558次阅读

- 基于片上可编程系统解决方案实现视频编解码IP核的设计 880次阅读

- 基于Nios II系统实现LCD显示控制IP核的设计 1401次阅读

- 锐尔威视科技全志A20双核 CloverBox方案板/开发板介绍 4318次阅读

- STM32单片机控制蓝牙的电路 1.6w次阅读

- 基于TI TMS320F28M35H52C 的非对称双核 MCU 提高系统性能方案 3255次阅读

- 什么是双核、双芯和超线程 处理器多核速度是不是越快? 7262次阅读

- 中颖单片机双核(DSP和MCU)SH99F100基于工业控制中的应用 1929次阅读

- 基于DSP/BIOS的多信号并行处理软件架构设计 1825次阅读

- 双DSP柔性处理系统研究 1419次阅读

- 铁电存储器FM18L08在DSP系统中的应用 1822次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1489次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 91次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 9次下载 | 免费

- 6基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 3次下载 | 免费

- 8基于单片机的红外风扇遥控

- 0.23 MB | 3次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30319次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537791次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233045次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论