资料介绍

SN65LV1023A

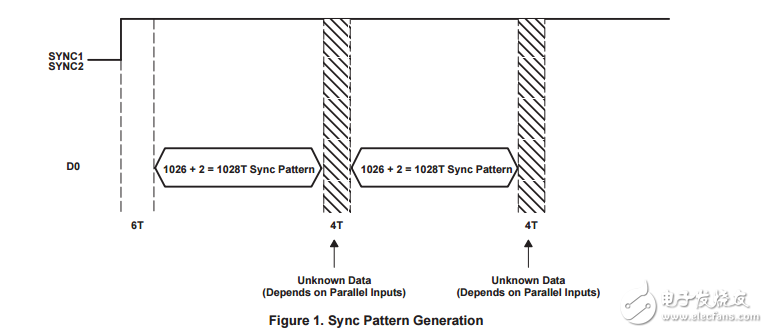

This document is an errata to the SN65LV1023A data sheet (Literature No. SLLS570)。 Purpose This document describes the SYNC pattern behavior of the SN65LV1023A. A logic error was found and the detail is discussed here. Sync Pattern Generation The sync pattern generation is designed to work as the following: After SYNC1 or SYNC2 is held high for at least 6T(T = 1 refclk cycle), the SYNC pattern is generated on the serial line for 1026T. During this 1026−cycle SYNC pattern transmission, it is not required that SYNC1 or SYNC2 be held high. Now there are two different cases in general where user might use this SYNC pattern generation: Case#1) SYNC1 or SYNC2 is held high once at least 6T but no more than 1026T: In this case, the sync pattern generation should generate 1026T of SYNC pattern only once and the data that follow the SYNC pattern on the serial line should reflect the parallel inputs. In this scenario the sync pattern generation is working as it is designed. Case#2) SYNC1 or SYNC2 is held high continuously more than at least 1038T (6T to invoke the first series of SYNC pattern, and 1026T which is the duration of the first series of SYNC pattern, and 6T to invoke the second series of SYNC pattern): If the sync pattern generator were to operate as it is intended, a user should be able to observe the continuous SYNC pattern on the serial line. For example, if the SYNC1 or SYNC2 is held high for 1039T, a user will see the SYNC pattern being generated continuously for 2052T (=1026T+1026T)。 However, as shown in Figure 1 the device behaves in a way that if the SYNC1 or SYNC2 is held high more than 1038T, it sends out 1028T of SYNC pattern plus 4T of data (which reflect the data that is present on the parallel input at that time) and another 1026T of SYNC pattern. Figure 1 basically shows what would happen to the data on the serial line if the SYNC1 or SYNC2 is held for an extended period of time.

- SN65LV1023A-EP SN65LV1224B-EP LVDS串行器/解串器数据表

- 10 MHz至66 MHz,10:1 LVDS串行器/去串行器SN65LV1023A数据表

- 4位同步二进制计数器SN54LV161A SN74LV161A 数据表

- 4位同步二进制计数器SN54LV163A SN74LV163A数据表

- DC1023A-模式

- SN65LV1023A,SN65LV1224B,pdf(10-MHz to 66-MHz, 10:1-LVDS Seri

- SN65LVDS100,SN65LVDT100,SN65LV

- SN65LVDS348,SN65LVDT348,SN65LV

- SN65LVDS179,SN65LVDS180,SN65LV

- SN54LV27A,SN74LV27A,pdf(TRIPLE

- SN54LV132A,SN74LV132A,pdf(Quad

- SN54LV10A,SN74LV10A,pdf(TRIPLE

- SN54LV21A,SN74LV21A,pdf(DUAL 4

- SN54LV175A, SN74LV175A,pdf(QUA

- SN54LV174A, SN74LV174A,pdf(HEX

- 永磁同步电机电磁噪声的生成原理 315次阅读

- 闭包在错误处理中的应用模式探索 299次阅读

- 导致PLC信号干扰的错误操作 429次阅读

- 图解Spring Bean生成流程,非常详尽 674次阅读

- 最常见的PLC编程逻辑错误 1018次阅读

- 为什么在Verilog HDL设计中一定要用同步而不能用异步时序逻辑? 1114次阅读

- LV-A(T):支持部分掉电电子元件的逻辑器件 607次阅读

- Rust代码启发之返回值异常错误处理 2003次阅读

- 组合逻辑生成的时钟有哪些危害 3992次阅读

- 微雪电子SN65VHD230 CAN接口通信模块简介 3832次阅读

- PADS Layout和Router之间的同步模式解析 1.1w次阅读

- 在FPGA逻辑设计中编程语言最容易忽略的错误 1976次阅读

- 德州仪器推出超小型封装的LVDS串行/解串器 2781次阅读

- 解析存储跨中心双活中,数据同步逻辑错误的解决方案 2855次阅读

- 同步源和PLL源在功率分析仪中的作用 4396次阅读

下载排行

本周

- 1TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 2开关电源基础知识

- 5.73 MB | 6次下载 | 免费

- 3100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 4嵌入式linux-聊天程序设计

- 0.60 MB | 3次下载 | 免费

- 5基于FPGA的光纤通信系统的设计与实现

- 0.61 MB | 2次下载 | 免费

- 651单片机窗帘控制器仿真程序

- 1.93 MB | 2次下载 | 免费

- 751单片机大棚环境控制器仿真程序

- 1.10 MB | 2次下载 | 免费

- 8基于51单片机的RGB调色灯程序仿真

- 0.86 MB | 2次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33564次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6653次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537796次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191185次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论