资料介绍

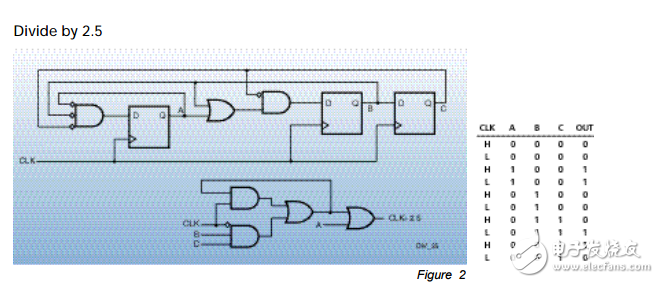

T his article describes how to divide clocks by 1.5, 2.5, and by 3, and 5 with a 50% duty-cycle output. Dividing an incoming clock frequency by any integer number is trivial, and division by any even number always generates a 50% duty cycle output. However, sometimes it is necessary to generate a 50% duty cycle frequency that is not an even integer sub-multiple of the source clock. These circuits are useful in XC4000-family and Spartan-family devices, where they are simple and efficient, and both cheaper and faster than any external phase-locked-loop alternative. Virtex devices do not need to use these tricks because they can implement these and many other functions in either of their four dedicated delay-locked-loop circuits, if the incoming clock rate is higher than 25 MHz. How They Work Each circuit assumes a 50/50 duty cycle of the incoming clock, otherwise the fractional divider output will jitter, and the integer divider will have unequal duty cycle. All four circuits use combinatorial feedback around a look-up table, which works perfectly and is glitch-free, but may cause your circuit simulator to fail. These circuits have a look-up table input driven from the clock signal, with minimal skew between the A and B inputs. The chosen vertical clock line must, therefore, also have access to a LUT input. This is best achieved by coding the design as a Hard Macro. Divide by 1.5 in One CLB. This circuit divides the clock by 1.5, generating 60 MHz from a 90 MHz input for example (Figure1)。 The two flip-flops form a ÷3 circuit, and the G and H look-up tables together generate two output periods at the H output. The first output pulse is driven by the A flip-flop, the second output pulse is derived from the B flipflop, but is delayed half an incoming clock cycle. The output stays Low while the clock is High, and stays High, after B has gone Low, until the clock goes Low again. It is this latch circuit that may cause simulator problems. by Peter Alfke, Xilinx Applications Eng

- CLOCK常见问题解答

- AD设计的PCB天线原文件 0次下载

- Gowin Fixed Point DIVIDER用户指南

- Gowin Integer Multiply Divider IP用户指南

- Gowin时钟资源(Clock)用户指南

- NY8L系列高频时钟分频应用注意事项

- 基于AN_Clock_Optimization模拟到数字转换的参考设计

- 基于Matlab的机构与机器人分析资料下载 11次下载

- 同步电路设计中CLOCK SKEW的分析说明 21次下载

- 1000+例各类获奖电赛作品资料集(电路篇、代码篇、教程篇……) 0次下载

- 简易的电子时钟的clock函数的详细资料合集免费下载 24次下载

- tsl2561相关资料 10次下载

- ICS307 Clock Generator 0次下载

- FPGA_Alarm_Clock 0次下载

- The Design of a Clock Synchron

- SOC设计中Clock Gating的基本原理与应用讲解 468次阅读

- RQS_CLOCK-12时钟设置建议 515次阅读

- 浅谈功分器和耦合器的区别 1065次阅读

- 功分器和合成器的主要区别 714次阅读

- FPGA中Bank和Clock Region之前有什么关系? 799次阅读

- Power Divider和Power Splitter 1301次阅读

- SYSREF和Device clock是否需要同源?SYSREF有哪几种模式? 3131次阅读

- Xilinx跨时钟域时序约束 2000次阅读

- 揭开xenomai双核系统下clock机制的面纱 1758次阅读

- 分析clock tree的小工具——CCOPT Clock Tree Debugger(一) 9786次阅读

- 降低Clock Uncertainty流程 5236次阅读

- 三个命令生成的报告中均可显示Clock Skew的具体数值 4552次阅读

- 时序分析基本概念之生成时钟详细资料介绍描述 8437次阅读

- WEBENCH Clock Architect:让硬件工程师少些烦恼,多分轻松 640次阅读

- 读Datasheet英文原文的原因分析 4198次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论