资料介绍

本文转载自:VagueCheung的博客

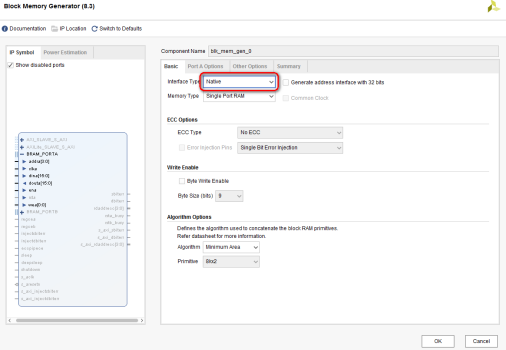

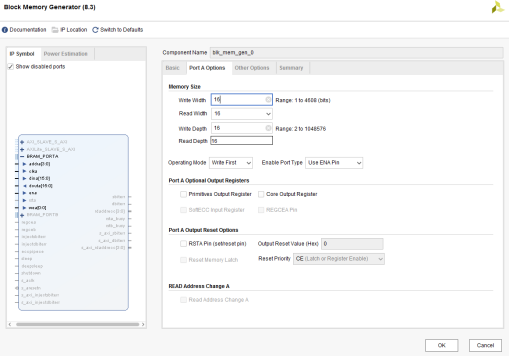

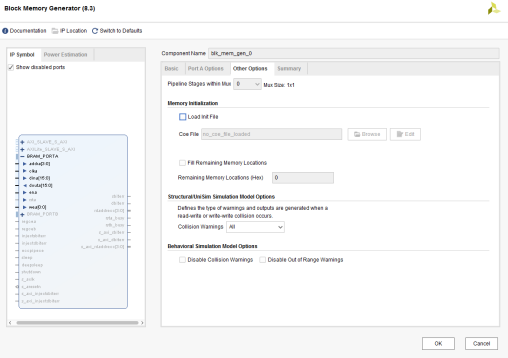

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3

BRAM IP核包括有5种类型:

Single-port RAM 单端口RAM

Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

True Dual-port RAM 双端口RAM

Single-por ROM 单端口ROM

Dual-port ROM 双端口ROM

BRAM核支持两种总线形式的输入输出:Native or AXI4

以下图配置为例:Single-port RAM

Testbench 测试代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/11/21 15:52:48

// Design Name:

// Module Name: test_bench_BRAM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test_bench_BRAM(

);

reg[15:0] mem1_re[0:15]; //输入数据存储器

integer i;

// blk_mem_gen_0 inputs

reg clka;

reg ena;

reg wea;

reg[3:0] addra;

reg[15:0] dina;

// blk_mem_gen_0 outputs

wire[15:0] douta;

blk_mem_gen_0 blk_mem_gen_m0

(

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.douta(douta) //数据输出接口 读出

);

always #5 clka = ~clka;

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re); //数据是[1 2 3 4 5 6 7 8 9]

initial begin

clka = 0;

ena = 0;

wea = 0;

addra = 0;

dina = 0;

#150 ena = 1;

begin

for(i=0;i

#10 wea

addra

/*if(i == 0) begin

addra

end

else if (i == 1) begin

addra

end

else if(i == 2) begin

addra

end

else if(i == 3) begin

addra

end

else begin

wea

end*/

dina

if(i == 15) begin

dina

wea

end

$display("mem_a[%d] = %h", i, mem1_re[i]);

end

end

#40000 $finish;

end

endmodule

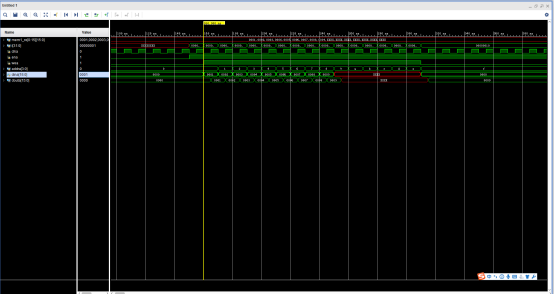

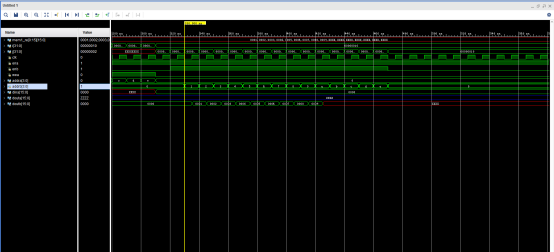

仿真结果如下:

配置为simple dual port ram

Testbench

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/11/21 15:52:48

// Design Name:

// Module Name: test_bench_BRAM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test_bench_BRAM(

);

reg[15:0] mem1_re[0:15]; //输入数据存储器

integer i;

integer j;

// blk_mem_gen_0 inputs

reg clk;

reg ena;

reg enb;

reg wea;

reg[3:0] addra;

reg[3:0] addrb;

reg[15:0] dina;

// blk_mem_gen_0 outputs

wire[15:0] douta;

wire[15:0] doutb;

/*****单端口 网络配置的IP核

blk_mem_gen_0 blk_mem_gen_m0

(

.clka(clka), //BRAM 输入时钟信号

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.douta(douta)

);*******/

/**************简单双端口RAM A进B出**************/

blk_mem_gen_0 blk_mem_gen_m0

(

.clka(clk), //BRAM 输入时钟信号

.ena(ena), //BRAM 时钟使能信号

.wea(wea), //写使能信号

.addra(addra), //地址信号

.dina(dina), //数据输入接口 写入

.clkb(clk), //BRAM 输入时钟信号

.enb(enb), //BRAM 时钟使能信号

.addrb(addrb), //地址信号

.doutb(doutb)

);

always #5 clk = ~clk;

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re);

initial begin

clk = 0;

ena = 0;

enb = 0;

wea = 0;

addra = 0;

addrb = 0;

dina = 0;

#150 ena = 1;

begin

for(i=0;i

#10 wea

addra

dina

if(i == 15) begin

dina

wea

addra

end

$display("mem_a[%d] = %h", i, mem1_re[i]);

end

for(j=0;j

#10 addrb

enb

if( j == 15) begin

enb

addrb

end

end

end

#40000 $finish;

end

endmodule

测试仿真结果:

- Xilinx_Vivado_zynq7000入门笔记 71次下载

- Vivado中xilinx_courdic IP核(求exp指数函数)使用

- MicroBlaze(Vivado版)设置说明详细资料免费下载 0次下载

- Xilinx Vivado SDK 2017.2 0616 1 Win64软件免费下载 320次下载

- VIVADO——IP封装技术封装一个普通的VGA IP-FPGA 15次下载

- 摄像头的硬件函数(IP核) 13次下载

- PCI总线IP核(华为的商用) 30次下载

- VGA显示IP核(包括驱动) 18次下载

- USB IP核 13次下载

- PCI Express IP核应用参考设计 14次下载

- USB2.0 IP核源代码 35次下载

- FFT变换的IP核的源代码 10次下载

- 基于Xilinx_FPGA_IP核的FFT算法的设计与实现 37次下载

- FPGA中IP核的生成 11次下载

- 如何仿真IP核(建立modelsim仿真库完整解析) 35次下载

- LogiCORE JTAG至AXI Master IP核简介 849次阅读

- 从Xilinx FFT IP核到FPGA实现OFDM 1125次阅读

- Video In to AXI4-Stream IP核知识介绍 1429次阅读

- 使用VCS仿真Vivado IP核时遇到的问题及解决方案 1993次阅读

- 如何进行FFT IP配置和设计 2206次阅读

- 使用VIvado封装自定IP并使用IP创建工程 5265次阅读

- xilinx Vivado工具使用技巧 3934次阅读

- 调用Vivado IP核的方法 4648次阅读

- Vivado中的IP核封装 1w次阅读

- Xilinx Vivado硬件诊断和校验 2151次阅读

- Vivado软件仿真DDS核的过程中应该注意的问题 9659次阅读

- Vivado将模块封装为IP的方法介绍 7748次阅读

- 赛灵思Vivado开发套件与IP核的原理作用分析 1924次阅读

- 在Vivado下利用Tcl实现IP的高效管理 5708次阅读

- Vivado环境下如何在IP Integrator中正确使用HLS IP 4324次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论