资料介绍

描述

在这个项目中,我将介绍在 Vivado 中为 Vivado 版本 2020.2 中的 Digilent 的 Arty Z7 FPGA 开发板设置基本硬件设计的步骤。此硬件设计是我在此处找到的 PetaLinux 2020.2 教程的起点。

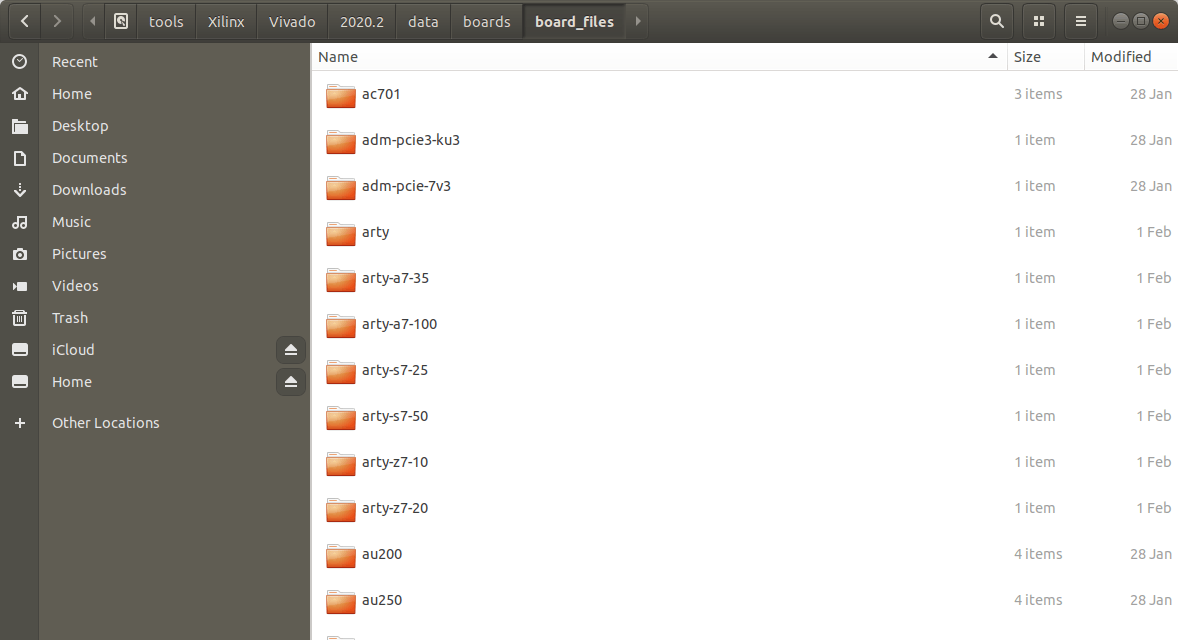

安装板定义文件

由于 Arty Z7 上的 FPGA 有一套硬件,它总是连接到开发板上,Digilent(以及许多其他设计/销售基于 Xilinx 的 FPGA 开发板的公司)为那些静态的提供板预设文件用户可以在其 Vivado 安装中安装的配置。这使用户不必花时间配置硬件设计的那一部分,而直接跳到他们设计的自定义部分。

在此处下载所有 Digilent FPGA 开发板的板预设文件。解压缩文件夹并将/new/board_files文件夹的内容复制到/

创建新的 Vivado 项目

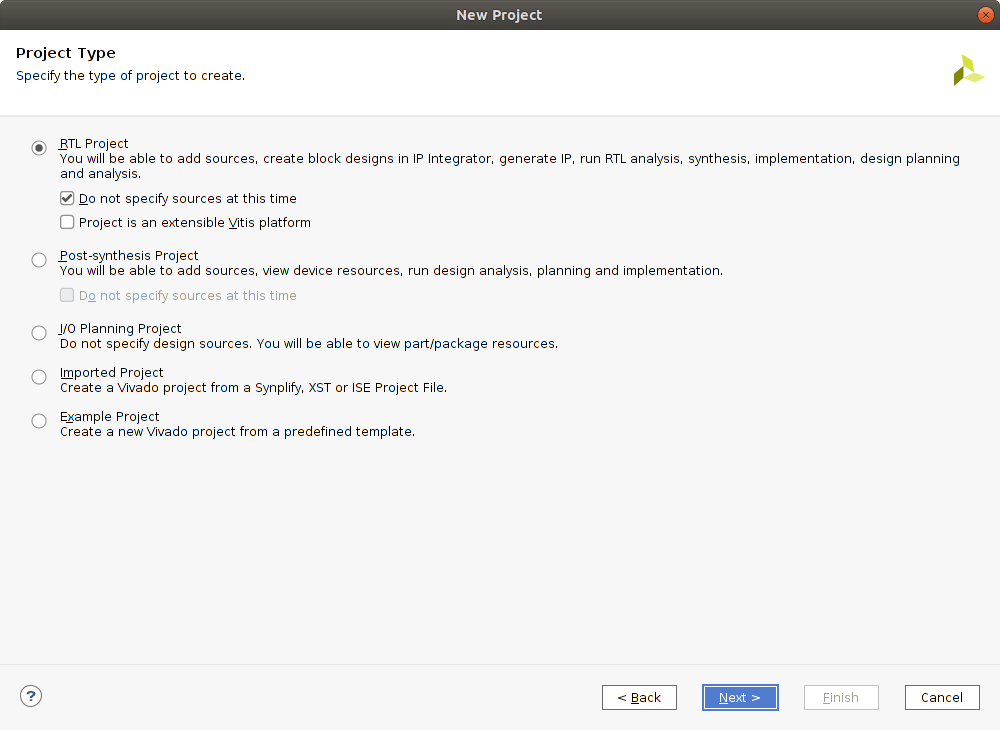

启动 Vivado 并选择创建新项目的选项。在弹出的前几个窗口中为其指定所需的名称并指定所需的文件路径。其中一个窗口将询问正在创建的项目类型。这是一个正在创建的基本 RTL 项目,它不是可扩展的 Vitis 平台,这意味着它不是针对加速应用程序和专用组件(例如它们所需的特定内核)的项目。因此,不要选中Project is an extensible Vitis platform框。除非您已经准备好将 RTL 文件(Verilog 或 VHDL 文件)导入到项目中,否则请选中“此时不要指定源”框。

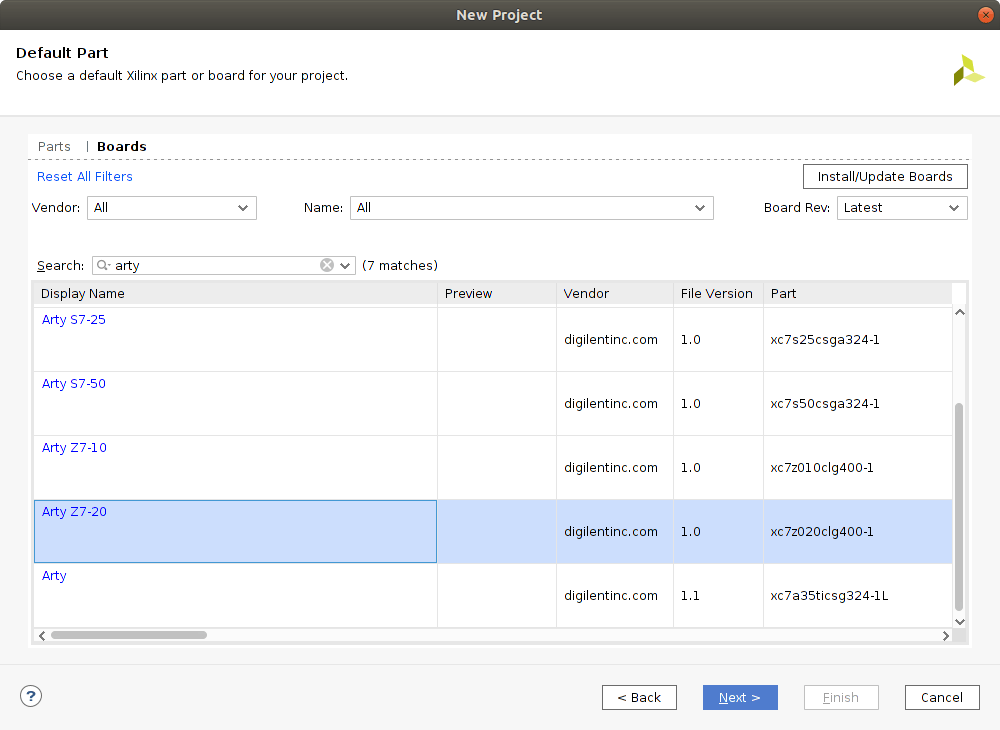

为了使该项目中安装在上一步中 Vivado 中的 Arty Z7 板的板预设文件可访问,请切换到Default Part窗口中的Boards选项卡并搜索关键字Arty 。我正在使用 Arty 板的 Arty Z7-20 版本,但请务必选择您正在使用的相应 Arty 型号。

创建块设计

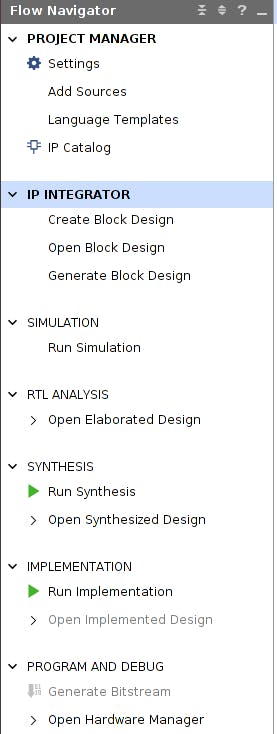

生成新项目后,第一步是创建新的块设计。从 Vivado 窗口左侧的 Flow Navigator 窗口中选择Create Block Design选项。

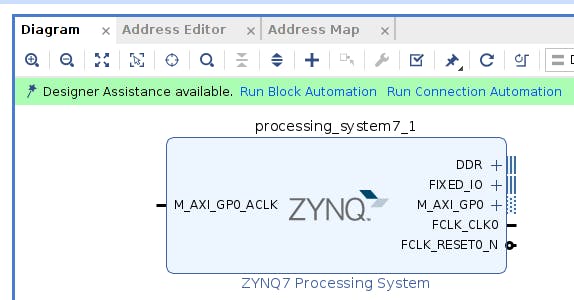

空白块设计生成后,单击中间的 + 符号,然后在出现的窗口的搜索栏中键入zynq 。双击弹出的ZYNQ7 处理系统选项,添加挂钩以访问在 FPGA 的可编程逻辑中物理实例化的 Zynq ARM 处理器。

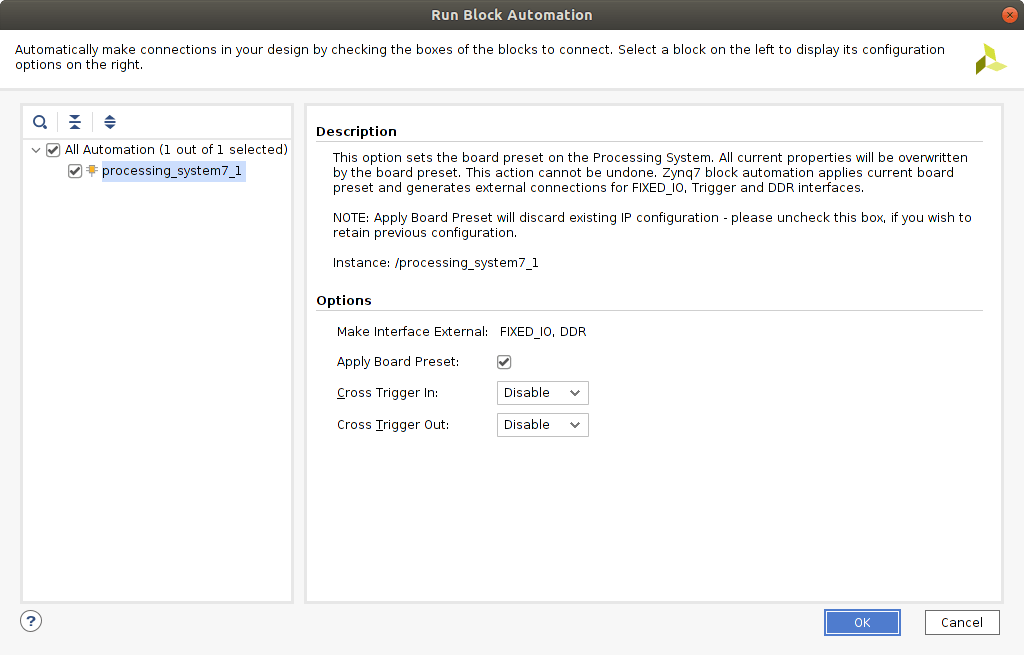

一旦 Zynq 处理系统 IP 模块出现在模块设计中,顶部将出现一个横幅,其中包含 Run Block Automation 选项。单击此链接,将出现一个窗口,指定运行块自动化将执行的操作。在这种情况下,它从第一步中安装在 Vivado 中的电路板预设文件中应用 Arty Z7-20 的电路板预设。单击确定,然后等待块自动化完成。

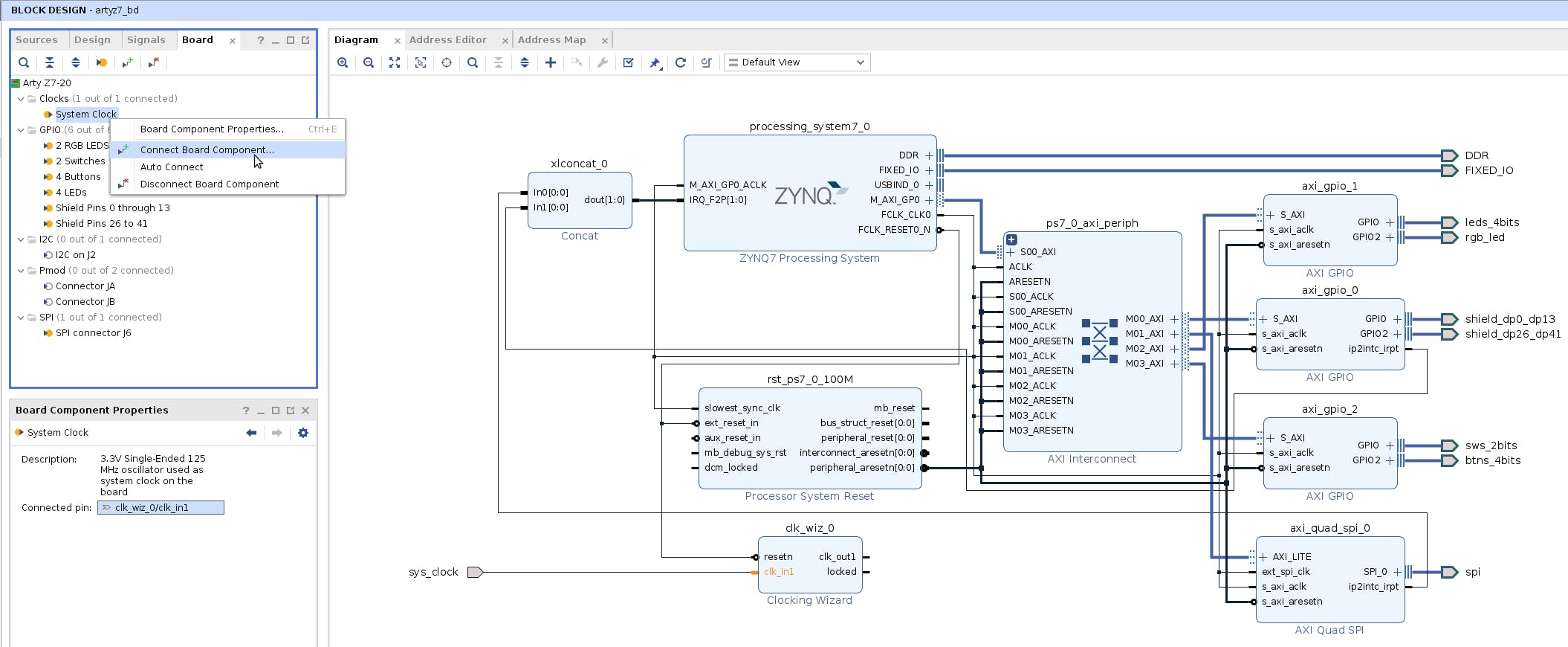

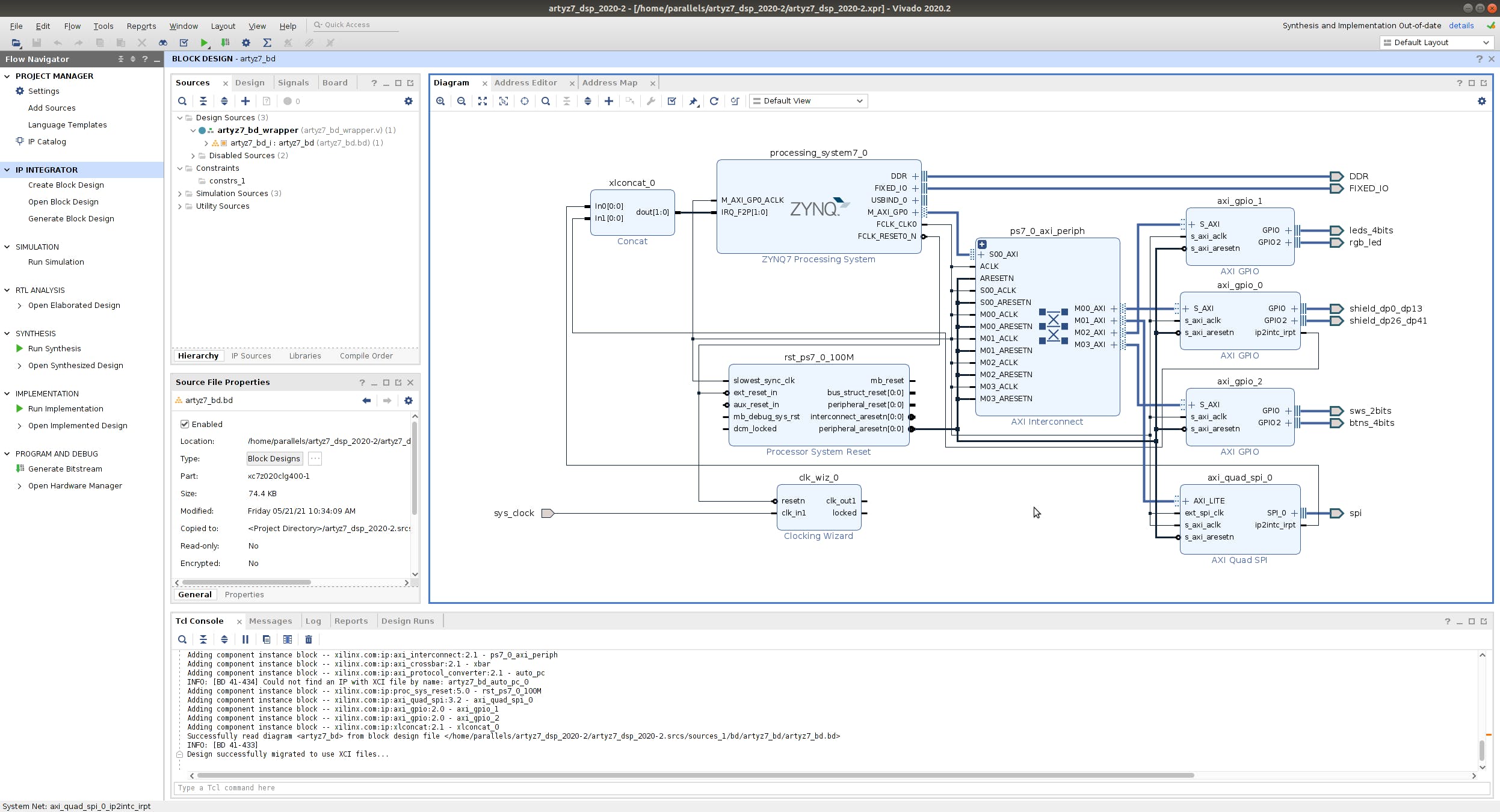

Zynq 处理系统的模块自动化完成后,可以使用图表左上角窗口中的Board选项卡将 Arty 板外设快速添加到模块设计中(如下所示,窗口中的其他选项卡位于源、设计和信号)。

右键单击要添加到模块设计的每个所需外围设备,然后选择自动连接或连接板组件... (允许特定的 IP 选择来连接外围设备而不是自动连接选项)。

请注意,并非所有外设都可以添加到单个模块设计中,因为其中一些外设需要访问 FPGA 上的相同封装引脚,并且如果没有某种添加了多路复用电路 (RTL)。

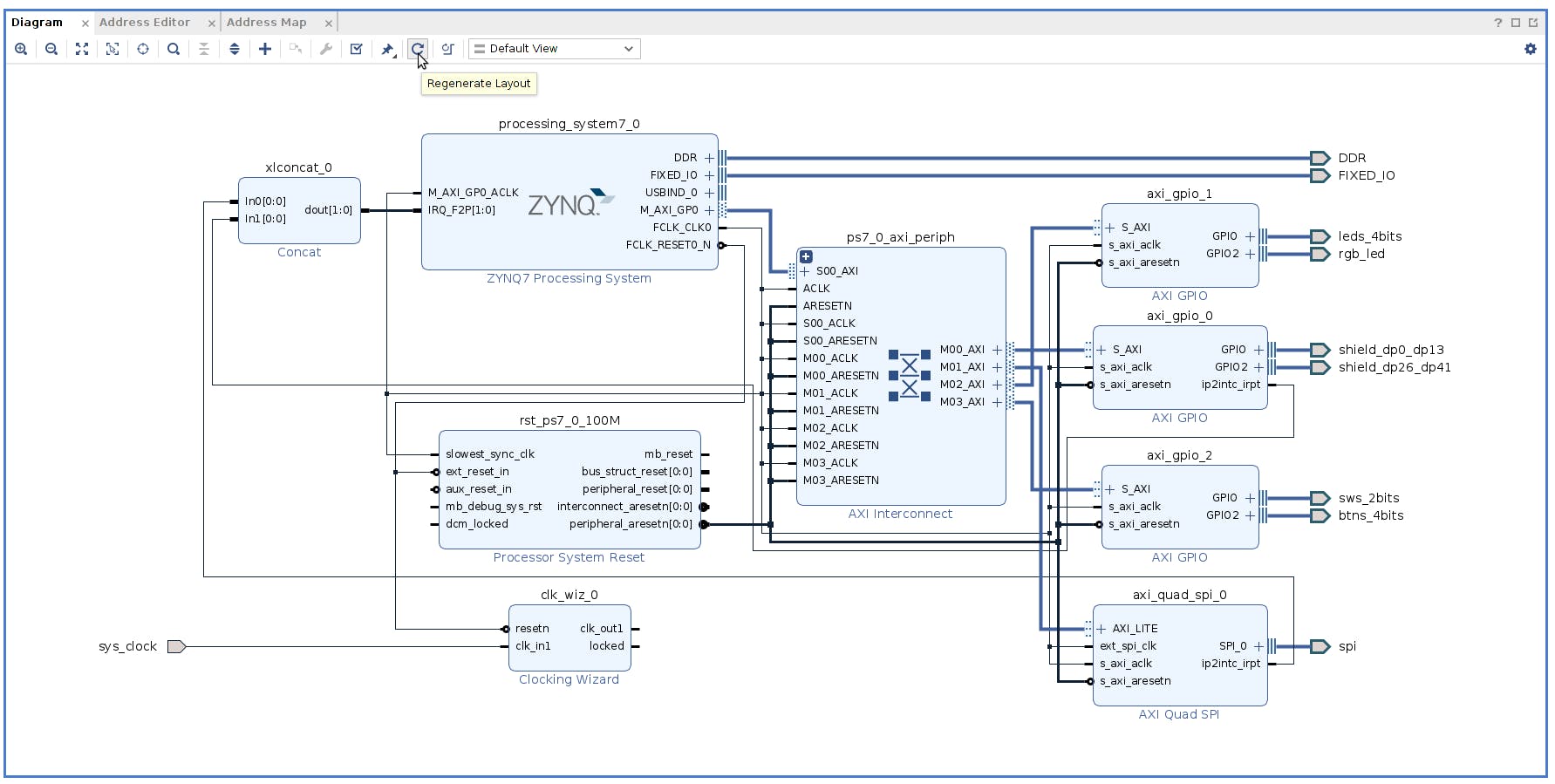

作为一个基本的起点,我添加了系统时钟、4 个 LED (LD0 - LD3)、2 个开关 (SW0 - SW1)、4 个按钮 (BTN0 - BTN3)、2 个 RGB LED (LD4 - LD5),所有 Arduino屏蔽引脚 (0 - 41) 和 SPI 连接器 (J6)。选择运行出现的所有连接自动化的选项,并在出现的窗口中为每个选项保留默认选择,详细说明运行连接自动化将执行的操作。

连接所有内容后,使用位于图表顶部工具栏上的圆形箭头按钮重新生成布局(也就是使块设计看起来漂亮且有条理)。之后,验证设计以验证没有严重警告或错误(现在可以忽略常规级别的警告)。单击位于图表顶部工具栏上的带有复选标记的框的图标以运行验证。

成功验证后保存并关闭块设计。

创建 HDL 包装器

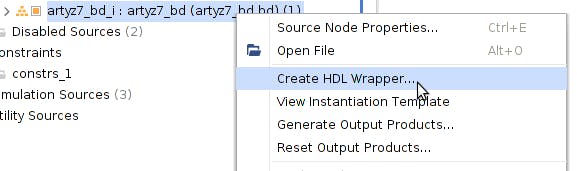

返回到Board选项卡所在的同一个小窗口中的Sources选项卡,您会在顶部看到块设计文件。右键单击它并选择选项Create HDL Wrapper...这将创建将块设计实例化到项目中的顶级 Verilog 文件。

选择该选项以允许 Vivado 管理包装器并自动对其进行更新。

允许 Vivado 生成 HDL 包装器并等待更新...文本从Sources选项卡的右上角消失。

运行综合、实现和生成比特流

至此,设计已完成,可以进行综合、布局和布线,并为其生成比特流。Synthesis 必须首先运行,因此从Flow Navigator窗口中选择Run Synthesis或按 F6。

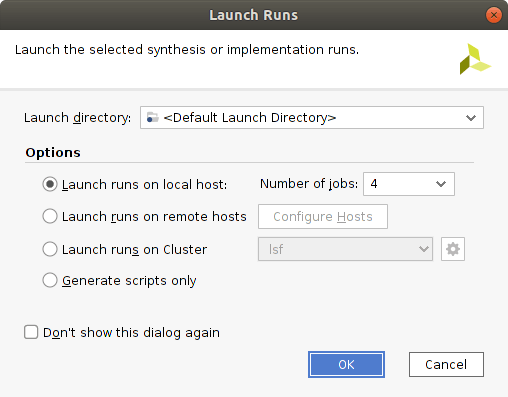

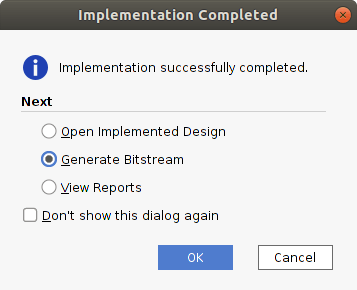

将出现一个窗口,指示即将启动哪些综合运行,在这种情况下,只有一个综合要运行,因此将选项设置为默认值并单击 OK。成功完成后,将出现一个对话框,询问下一步要采取的操作。选择Run Implementation选项对设计进行布局和布线,然后单击 OK。将出现另一个窗口,指示即将启动哪些实现运行,再次将选项设置为默认值,然后单击确定。

实施成功完成后,将出现另一个对话框,询问下一步要采取的操作。选择生成比特流的选项,然后单击确定。再次,将选项设置为默认值,然后在随后出现的窗口中单击“确定”,指示将要启动哪些运行以生成比特流。

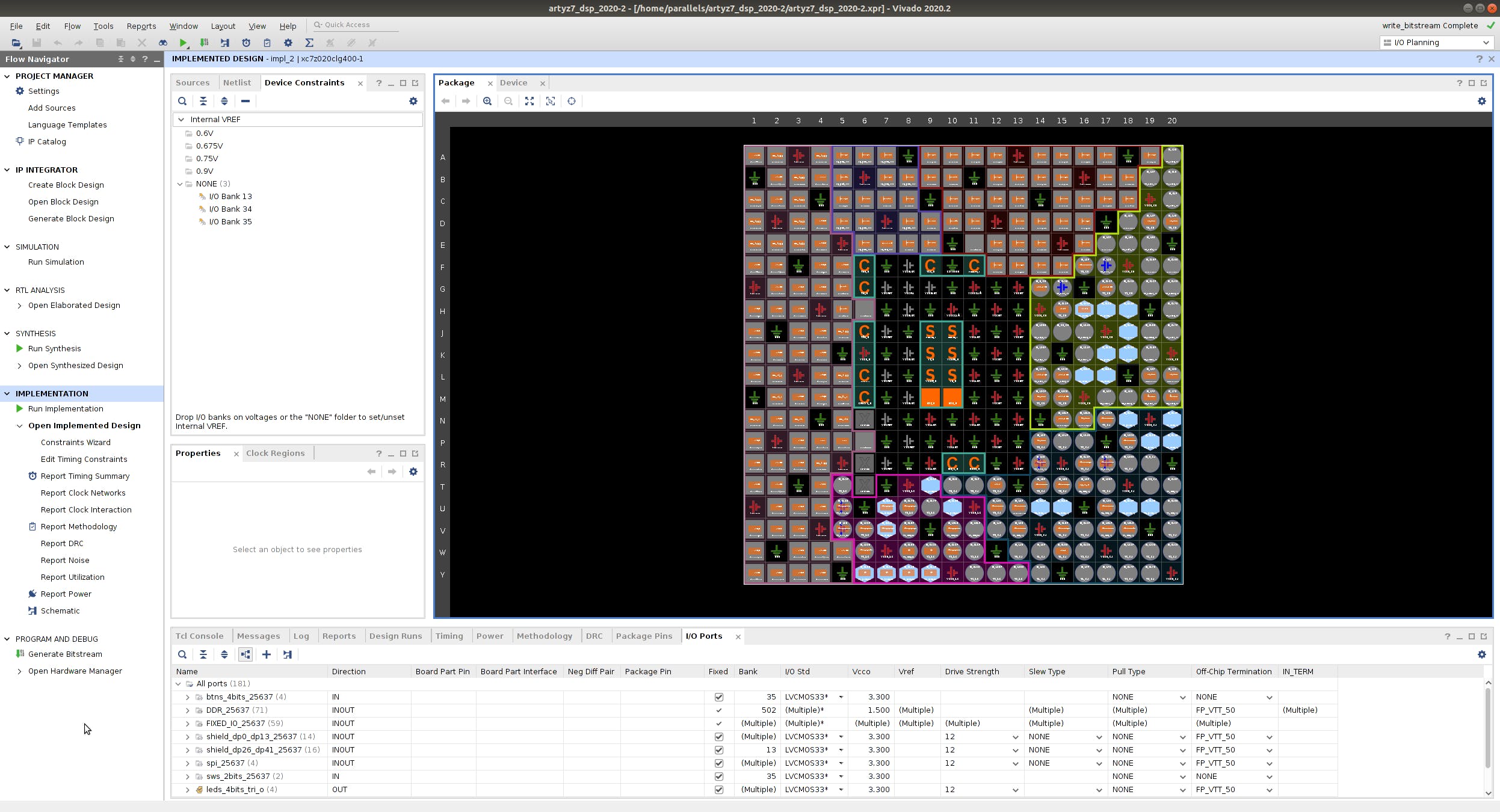

成功生成比特流后,选择打开已实现设计的选项并查看 Arty Z7 的 FPGA 设计的最终结果。Package选项卡将概述哪些信号连接到哪些封装引脚,Device选项卡将显示 Block Design 中创建的设计使用了多少可编程逻辑。

出口硬件

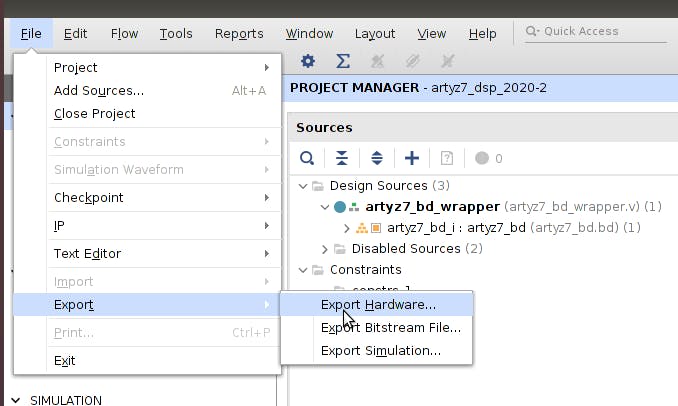

为了在 Vitis 创建的嵌入式应用程序中使用此硬件设计,或作为使用 PetaLinux 创建的嵌入式 Linux 映像的基础,需要将其打包并从 Vivado 中导出。

单击Vivado 主窗口左上角的文件选项卡,然后选择导出>导出硬件...

选择选项以在导出的硬件平台中包含比特流并指定所需的输出文件路径。我个人喜欢为各自的 Vivado 项目使用主项目文件夹。弹出窗口中的最后一个屏幕将汇总您的选择以供验证。单击完成以将硬件导出为 Xilinx 文件类型.XSA

- 使用Genode控制Zybo Z7 GPIO - 第2/2部分

- 基于Digilent Arty S7加速计的Windows鼠标

- 使用 Zybo Z7的Genode 操作系统框架实现

- 在MATRIX Voice ESP32上开始使用蓝牙

- Arty S7 FPGA板上的LED图案

- 在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

- 使用Genode控制Zybo Z7 GPIO

- 通过Edge Impulse开始使用TinyML

- Eclypse Z7上的Zmod ADC和DAC:正弦波环回

- AN5361_开始使用基于STM32CubeIDE双核STM32H7微控制器的项目

- 如何开始Z-Wave700系列产品的开发 1次下载

- Vivado设计流程指导手册 51次下载

- MYD-C7Z010和MYD-C7Z020 Linux开发手册的详细资料说明 21次下载

- xc7z020和xc7z010 FPGA芯片的电路原理图免费下载 501次下载

- Arty Board Artix-7 FPGA开源创客开发板用户手册 205次下载

- 如何在Zynq SoC上开始使用FreeRTOS 2309次阅读

- 在Vivado中实现ECO功能 2786次阅读

- Tcl在Vivado中的应用 1552次阅读

- Vivado中的Elaborate是做什么的? 1540次阅读

- Vivado在FPGA设计中的优势 1670次阅读

- 如何升级Vivado工程脚本 1869次阅读

- digilent APSoC Zynq-7000开源创客开发板介绍 2797次阅读

- digilentAPSoC Zynq-7000开源创客开发板介绍 2500次阅读

- digilent Arty A7-100 FPGA开源创客开发板介绍 6649次阅读

- Vivado 2017.1和Vivado 2016.4性能对比分析 1w次阅读

- Zybo Z7上OpenCV和SDSoC的结合 1933次阅读

- Arty A7开发板如何存储比特流配置文件和应用程序 1867次阅读

- Vivado使用误区与进阶——在Vivado中实现ECO功能 5451次阅读

- Tcl在Vivado中的基础应用 4966次阅读

- ISE约束导入vivado总共分几步 8911次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论