资料介绍

描述

这是如何为 Alinx 制造的AXU2CGA /B Zynq UltraScale+ FPGA 开发板创建硬件加速器平台的分步教程,该平台 可用于在 Xilinx Vitis 工具集下运行具有加速功能的 GNU Radio 应用程序。

添加 EA4GPZ 开发的gr-satellites并构建您自己的 OOT 模块也包含在这套教程中。

创建 Vitis 平台有几个主要步骤:

- 第 1 部分 - 创建 Vivado 硬件设计

- 第 2 部分 - 软件 - 构建 PetaLinux 和 GNU Radio

- 第 3 部分 - 使用 DPU 创建 Vitis 平台和应用程序

- 第 4 部分 - 在 Colab 和 Vitis-AI 中构建 AI 模型

先决条件

您应该已经从 AMD-Xilinx 安装了以下软件工具:

- 葡萄 2021.2

- 维瓦多 2021.2

- Petalinux 2021.2

这是第 1/4 部分:创建 Vivado 硬件设计

我们应该首先准备文件夹层次结构。为此,请执行以下命令:

mkdir axu2cgb

cd axu2cgb

mkdir hardware

mkdir software

mkdir platform

cd hardware

创建 Vivado 硬件设计

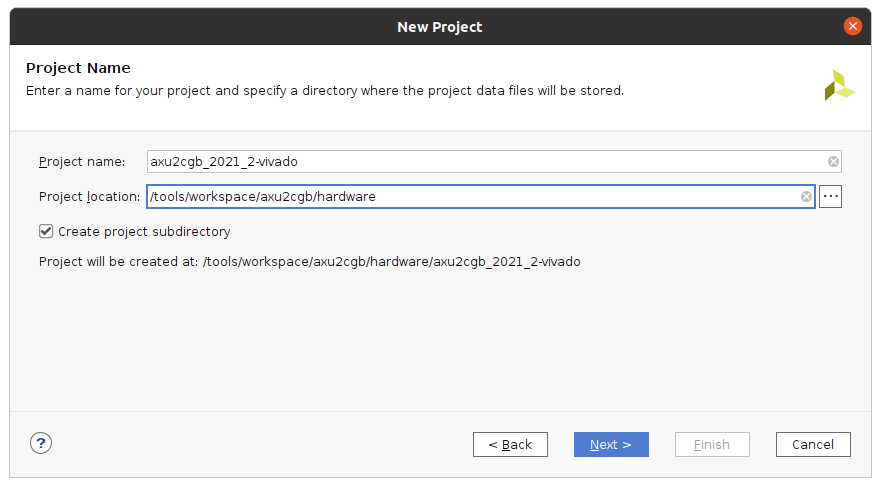

1- 运行 Vivado 并在硬件文件夹中创建一个名为“axu2cgb_2021_2-vivado”的项目。

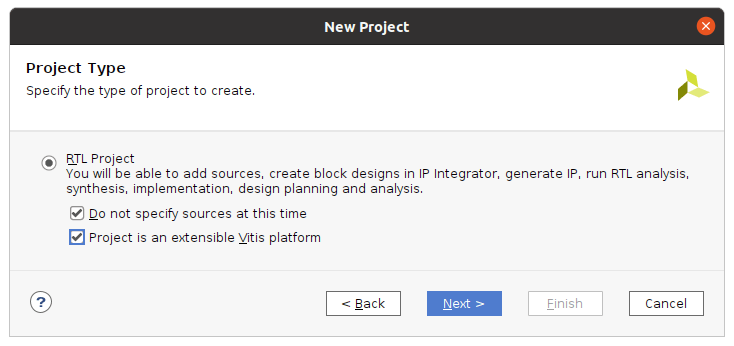

2- 在项目类型页面上,选择 RTL 项目并选择以下选项:

- 此时不要指定来源

- 项目是一个可扩展的 Vitis 平台

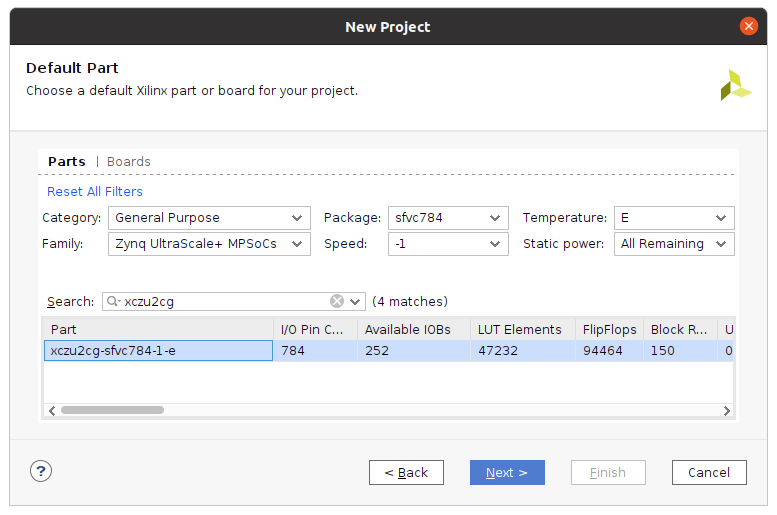

3- 在零件选项卡中选择名为xczu2cg-sfvc784-1-e的正确零件,然后单击下一步并完成。

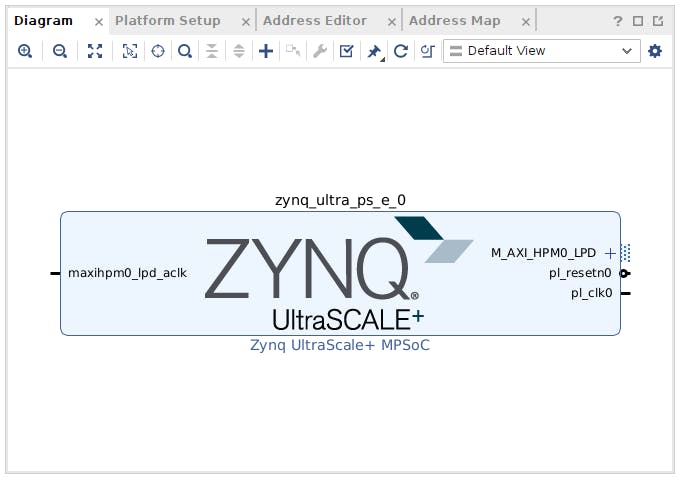

4- 创建模块设计并添加Zynq UltraScale+ MPSoc IP。

5- 现在我们需要为定制的 AXU2CGB 板仔细重新配置 Zynq Ultrascale+ 模块。

您将需要开发板用户手册,可从制造商网页下载:

http://www.alinx.vip:81/ug_en/AXU2CG_User_Manual.pdf

下载并打开它。我们需要根据 AXU2CGB 板的用户手册提供的数据来设置 Zynq 模块中的几乎所有设置。

注意:您可以跳过下面的整个第 6 节,只需执行第 7 节中的 TCL 命令即可一次性完成 Zynq 模块配置。

6- 双击电路板设计中的 Zynq 模块并浏览所有可用设置。

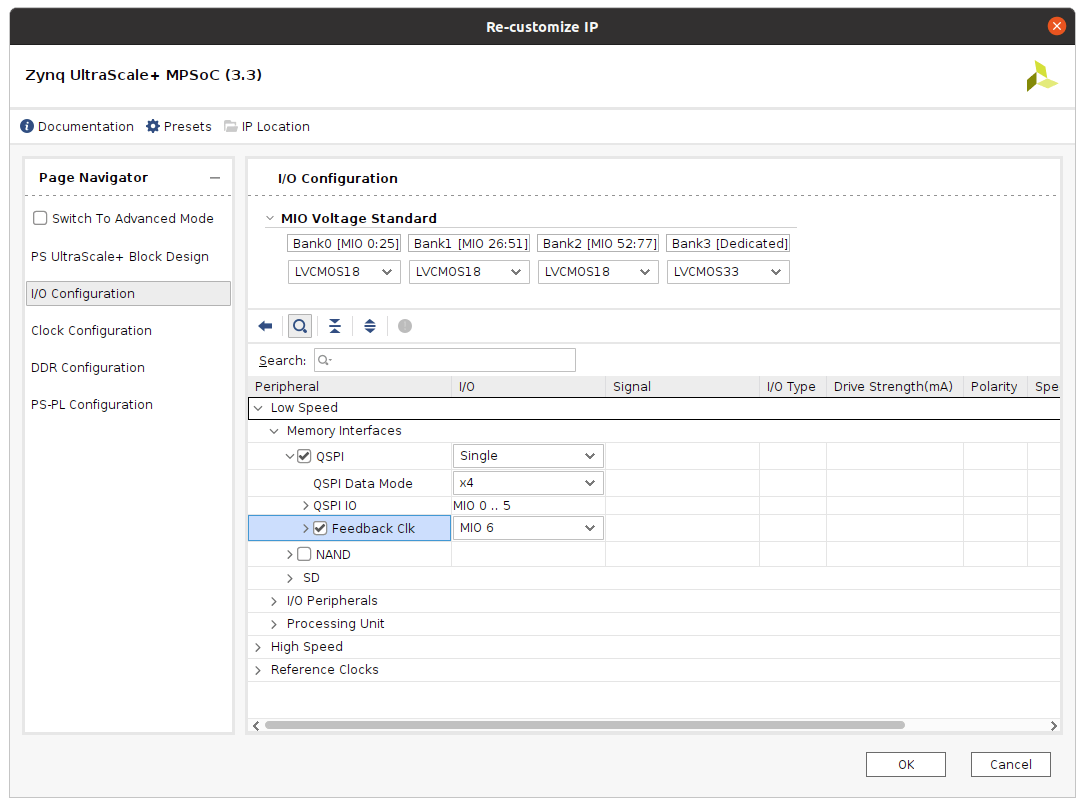

6-1- QSPI 配置

- 启用 QSPI 并在低速部分设置以下内容:

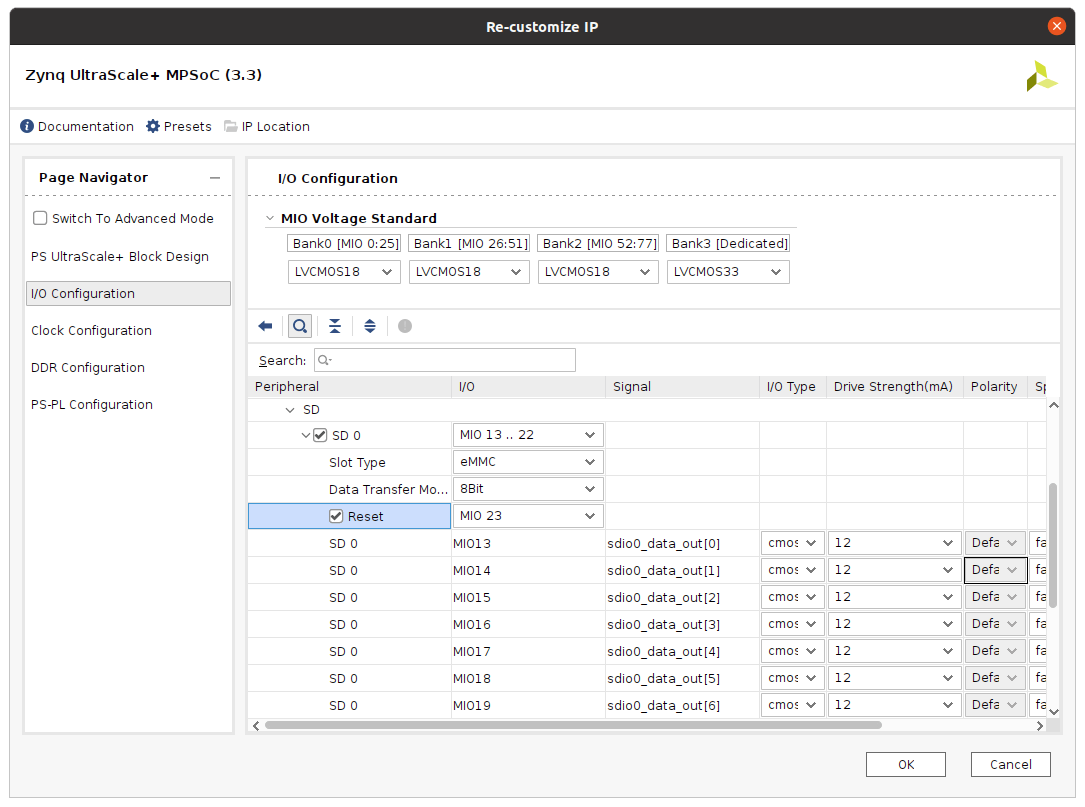

6-2- eMMC 配置

- 启用 SD 0 并选择:MIO13..22

- 插槽类型:eMMC

- 数据传输模式:8Bit

- 启用复位,然后选择 MIO23。

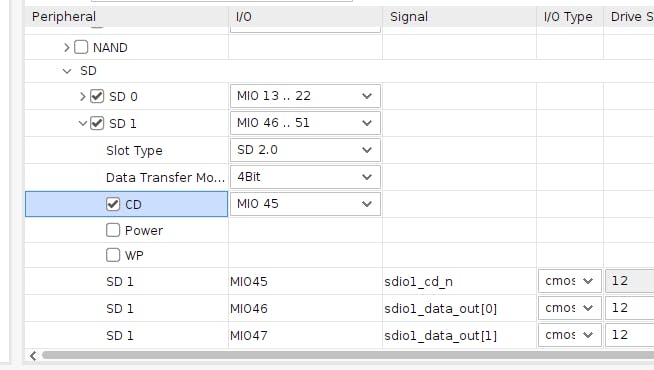

6-3- SD卡配置

- 启用 SD 1

- 选择 MIO 46..51

- 插槽类型:SD 2.0

- 数据传输模式:4Bit

- 启用 CD 以检测 SD 卡插入并选择 MIO45

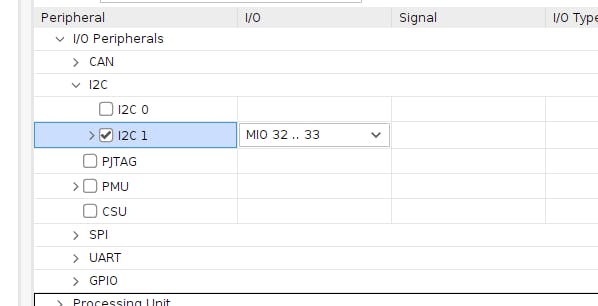

- 启用 I2C 1

- 选择 MIO 32..33

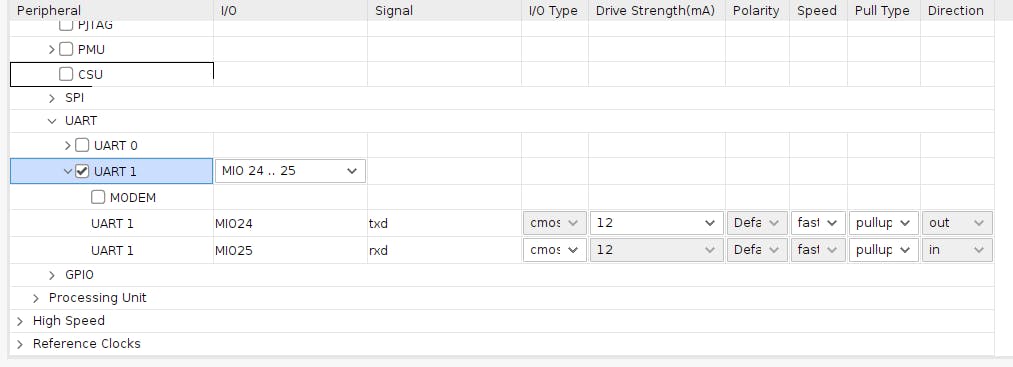

6-5- UART 配置

- 使能串口 UART 1

- 选择 MIO 24..25

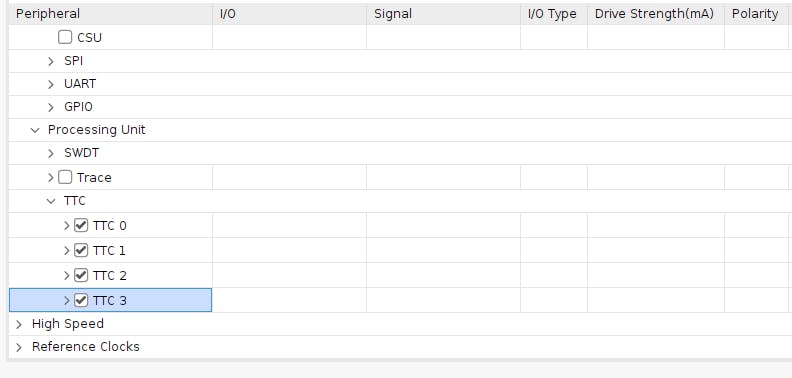

6-6- 启用 TTC0 - TTC3

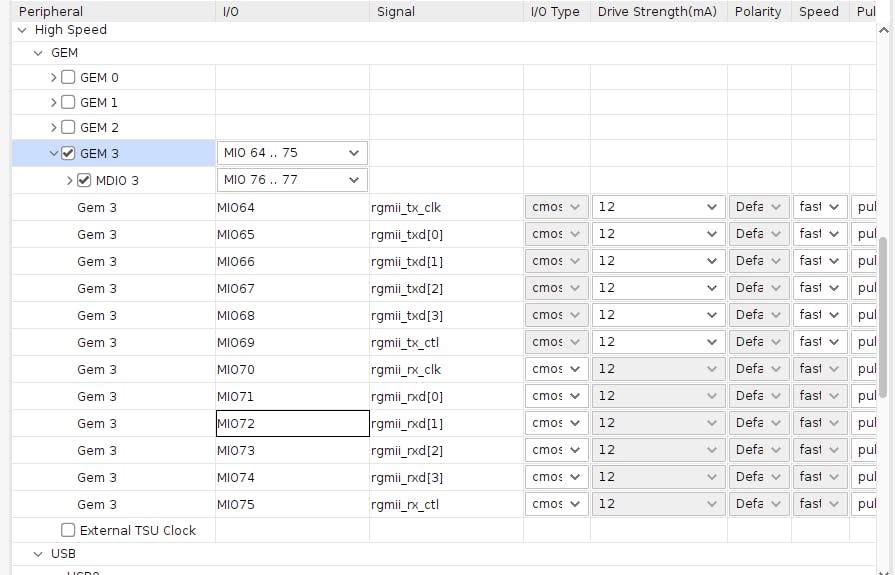

6-7- 千兆以太网配置

- 启用 GEM3 和 MDIO3

- 选择 MIO 64..75 GEM3

- 为 MDIO3 选择 MIO 76..77

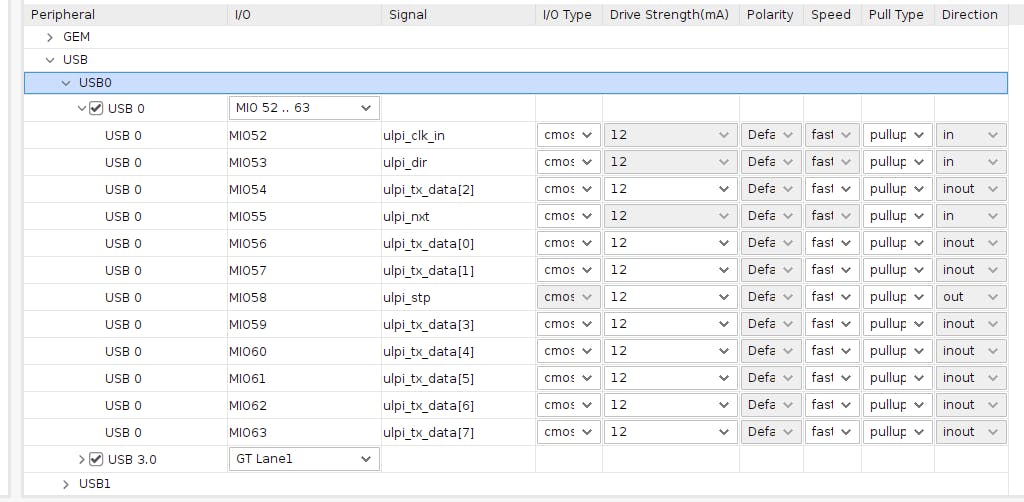

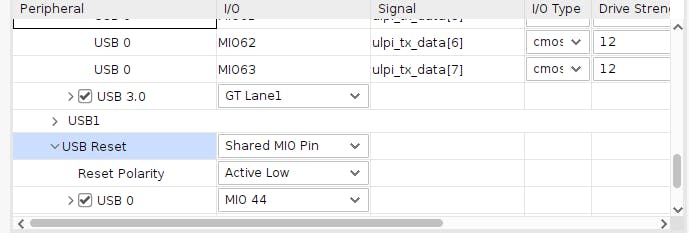

- 启用 USB 0

- 选择 MIO 52..63

- 启用 USB 3.0 并选择 GT Lane1

- 如下配置 USB 复位:

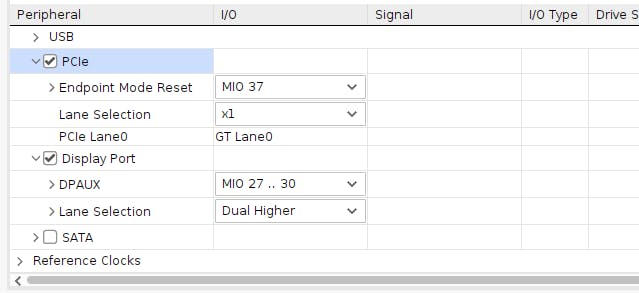

6-9- 配置 PCIe 和 Display Port

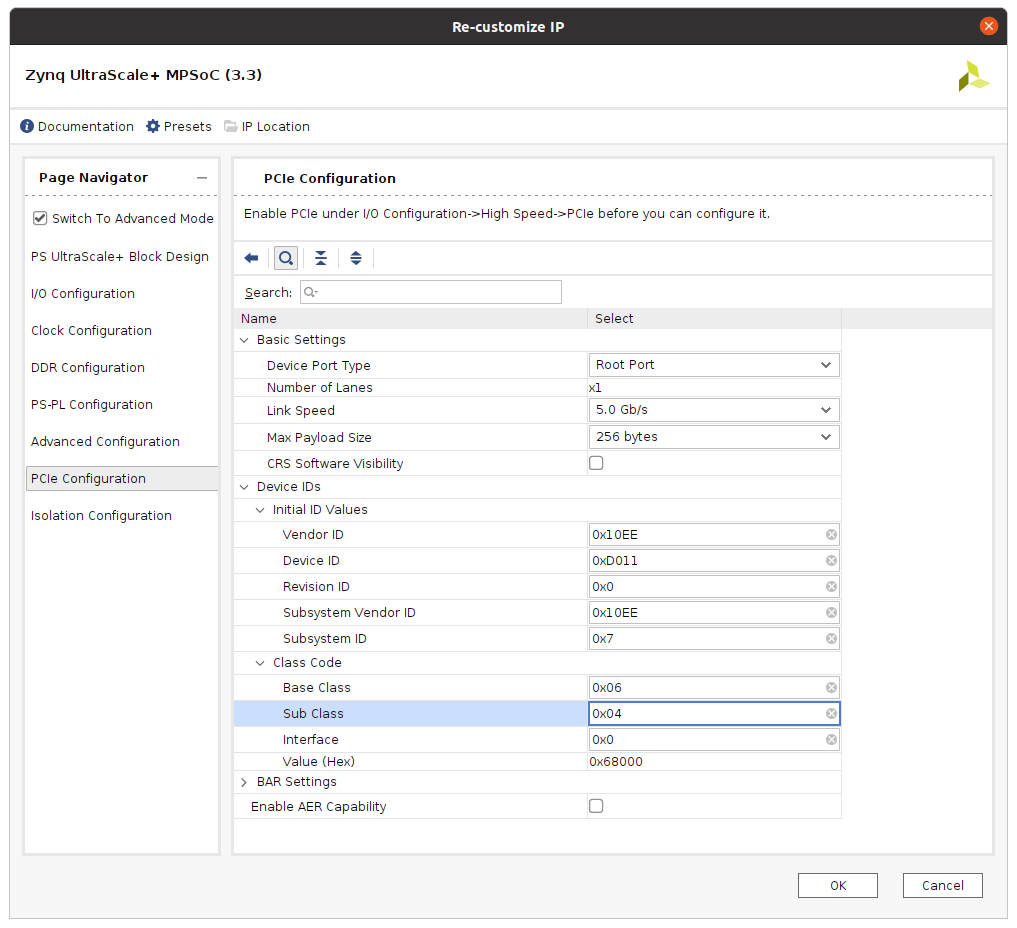

6-10- 附加 PCIe 配置

- 在页面导航器中启用切换到高级模式(左上角)

- 选择PCIe 配置选项卡。设置以下内容:

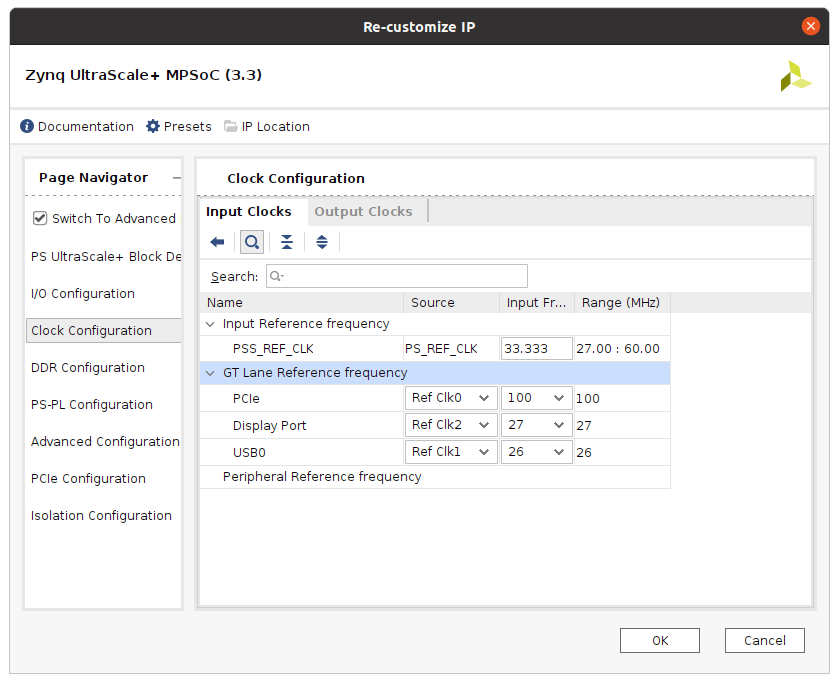

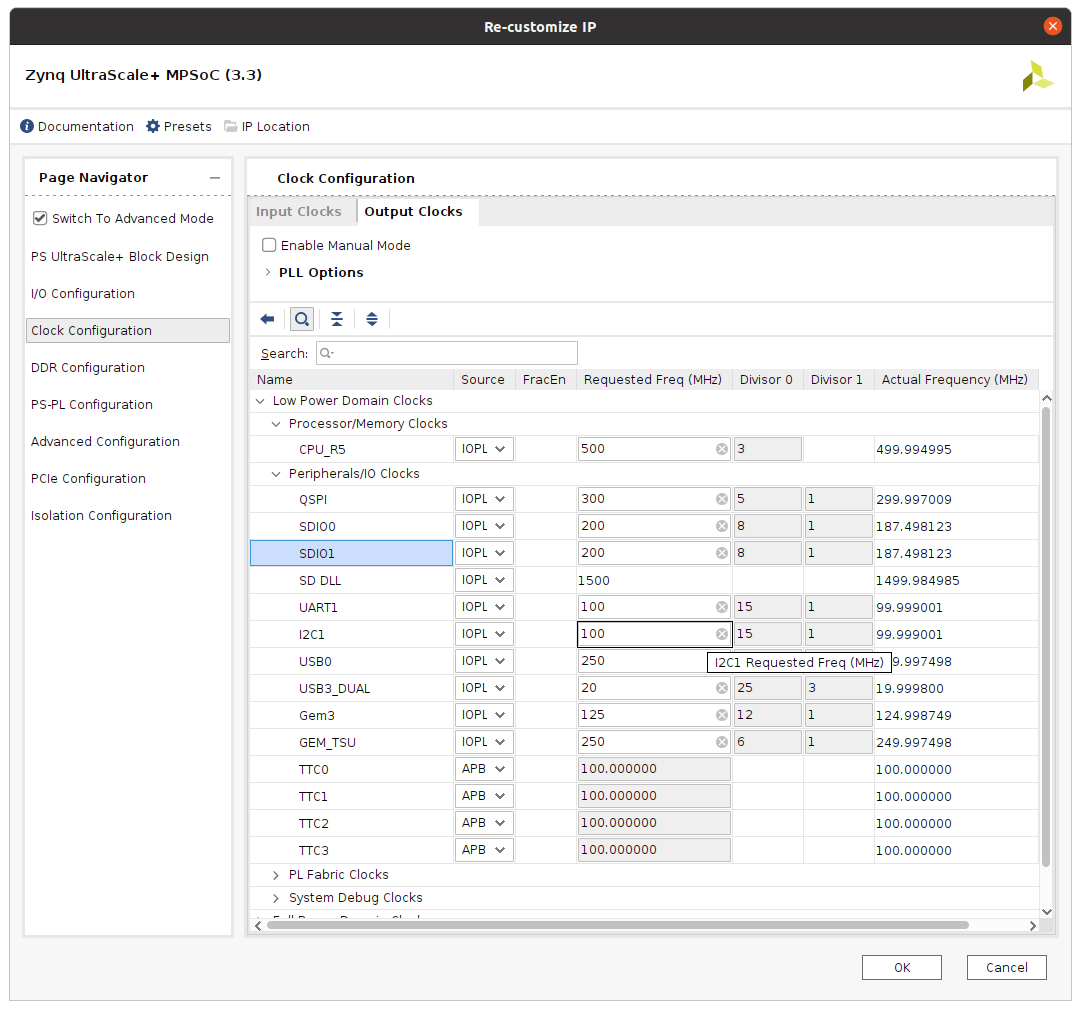

6-11- 时钟配置

选择时钟配置选项卡和输入时钟选项卡。设置以下内容:

- 输入参考频率 > PSS_REF_CLOCK:33.333MHz;

- PCIe:参考 Clk0,100MHz

- 显示端口:Ref Clk2,27MHz;

- USB0:参考时钟 1,26MHz。

6-12 在输出时钟选项卡中

- 如果未选择 IOPLL,则将其更改为 IOPLL。因此,它与同一个 PLL 对应。

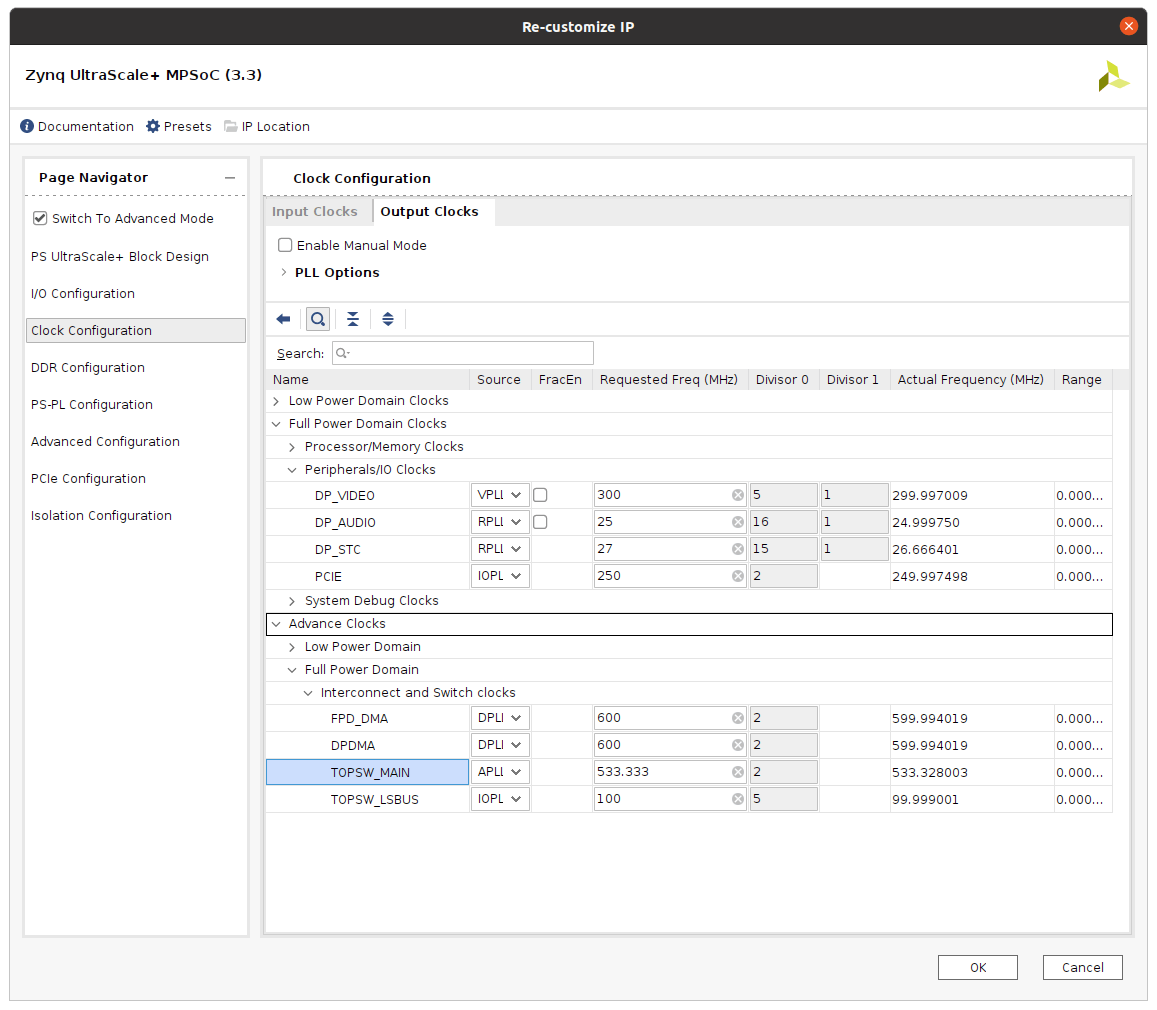

6-13-输出时钟继续

- DP_VIDEO:更改为 VPLL

- DP_AUDIO 和 DP_STC:更改为 RPLL。

- 其余的保持默认

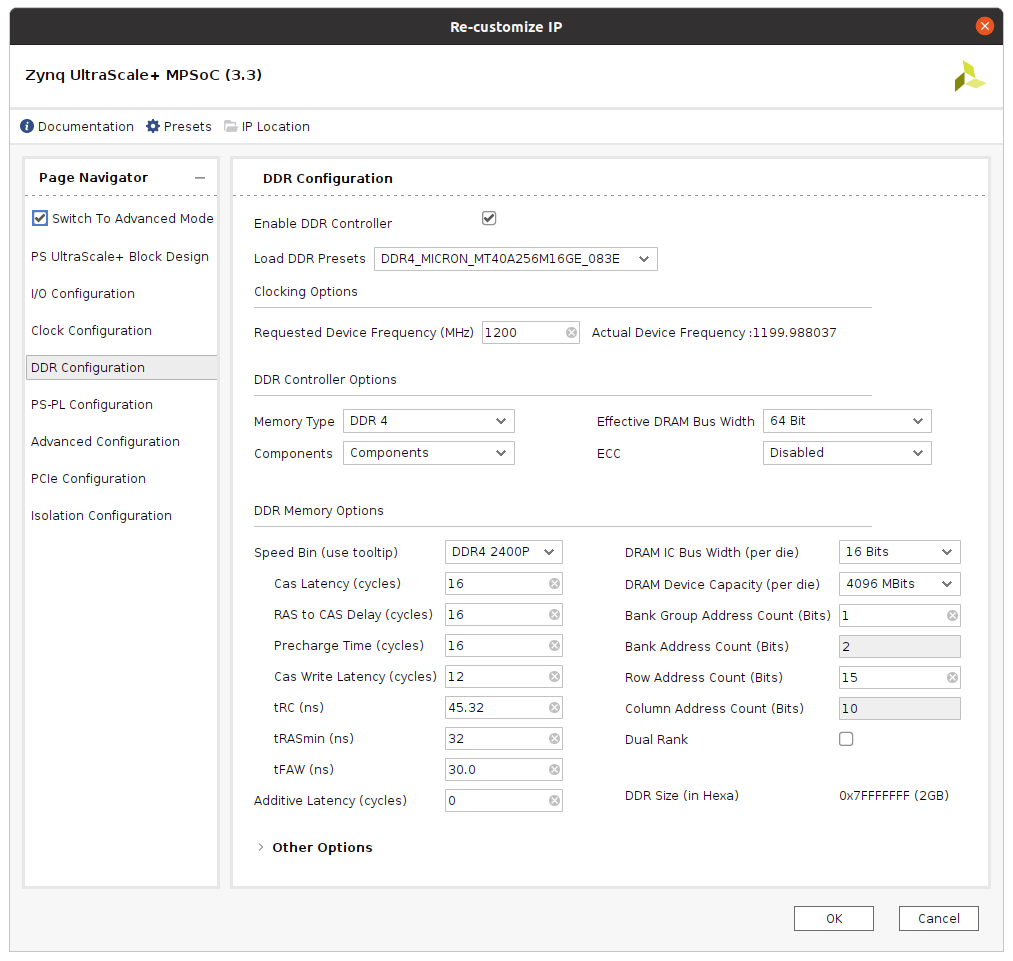

6-14- DDR 配置

- 加载 DDR 预设:选择DDR4_MICRON_MT40A256M16GE_083E

- 其他选项保持默认。

6-15- 单击确定,然后配置完成

7- 如果您需要一次重复整个 Zynq UltraScale+ 模块配置,这里有一个 TCL 命令。该命令可以在 TCL 控制台中执行。

set_property -dict [list CONFIG.PSU__DPAUX__PERIPHERAL__IO {MIO 27 .. 30} CONFIG.PSU__GEM__TSU__ENABLE {0} CONFIG.PSU__ENET0__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET1__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET2__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET3__PERIPHERAL__ENABLE {1} CONFIG.PSU__ENET3__GRP_MDIO__ENABLE {1} CONFIG.PSU__I2C1__PERIPHERAL__ENABLE {1} CONFIG.PSU__I2C1__PERIPHERAL__IO {MIO 32 .. 33} CONFIG.PSU__PCIE__PERIPHERAL__ENABLE {1} CONFIG.PSU__PCIE__PERIPHERAL__ENDPOINT_IO {MIO 37} CONFIG.PSU__PCIE__PERIPHERAL__ROOTPORT_IO {MIO 37} CONFIG.PSU__USB0__REF_CLK_SEL {Ref Clk1} CONFIG.PSU__PCIE__DEVICE_PORT_TYPE {Root Port} CONFIG.PSU__PCIE__CLASS_CODE_SUB {0x04} CONFIG.SUBPRESET1 {DDR4_MICRON_MT40A256M16GE_083E} CONFIG.PSU__QSPI__PERIPHERAL__ENABLE {1} CONFIG.PSU__QSPI__PERIPHERAL__DATA_MODE {x4} CONFIG.PSU__QSPI__GRP_FBCLK__ENABLE {1} CONFIG.PSU__SD0__PERIPHERAL__ENABLE {1} CONFIG.PSU__SD0__SLOT_TYPE {eMMC} CONFIG.PSU__SD0__RESET__ENABLE {1} CONFIG.PSU__SD1__PERIPHERAL__ENABLE {1} CONFIG.PSU__SD1__PERIPHERAL__IO {MIO 46 .. 51} CONFIG.PSU__SD1__GRP_CD__ENABLE {1} CONFIG.PSU__SD1__SLOT_TYPE {SD 2.0} CONFIG.PSU__TTC0__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC1__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC2__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC3__PERIPHERAL__ENABLE {1} CONFIG.PSU__UART1__PERIPHERAL__ENABLE {1} CONFIG.PSU__UART1__PERIPHERAL__IO {MIO 24 .. 25} CONFIG.PSU__USB0__PERIPHERAL__ENABLE {1} CONFIG.PSU__USB0__RESET__ENABLE {1} CONFIG.PSU__USB0__RESET__IO {MIO 44} CONFIG.PSU__USB__RESET__MODE {Shared MIO Pin} CONFIG.PSU__USB3_0__PERIPHERAL__ENABLE {1} CONFIG.PSU__USB3_0__PERIPHERAL__IO {GT Lane1} CONFIG.PSU_BANK_0_IO_STANDARD {LVCMOS18} CONFIG.PSU_BANK_1_IO_STANDARD {LVCMOS18} CONFIG.PSU_BANK_2_IO_STANDARD {LVCMOS18} CONFIG.PSU__DISPLAYPORT__PERIPHERAL__ENABLE {1} CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__SRCSEL {VPLL} CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__SRCSEL {RPLL} CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__SRCSEL {RPLL} CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__SRCSEL {APLL} CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__SRCSEL {IOPLL} CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__SRCSEL {IOPLL}] [get_bd_cells zynq_ultra_ps_e_0]

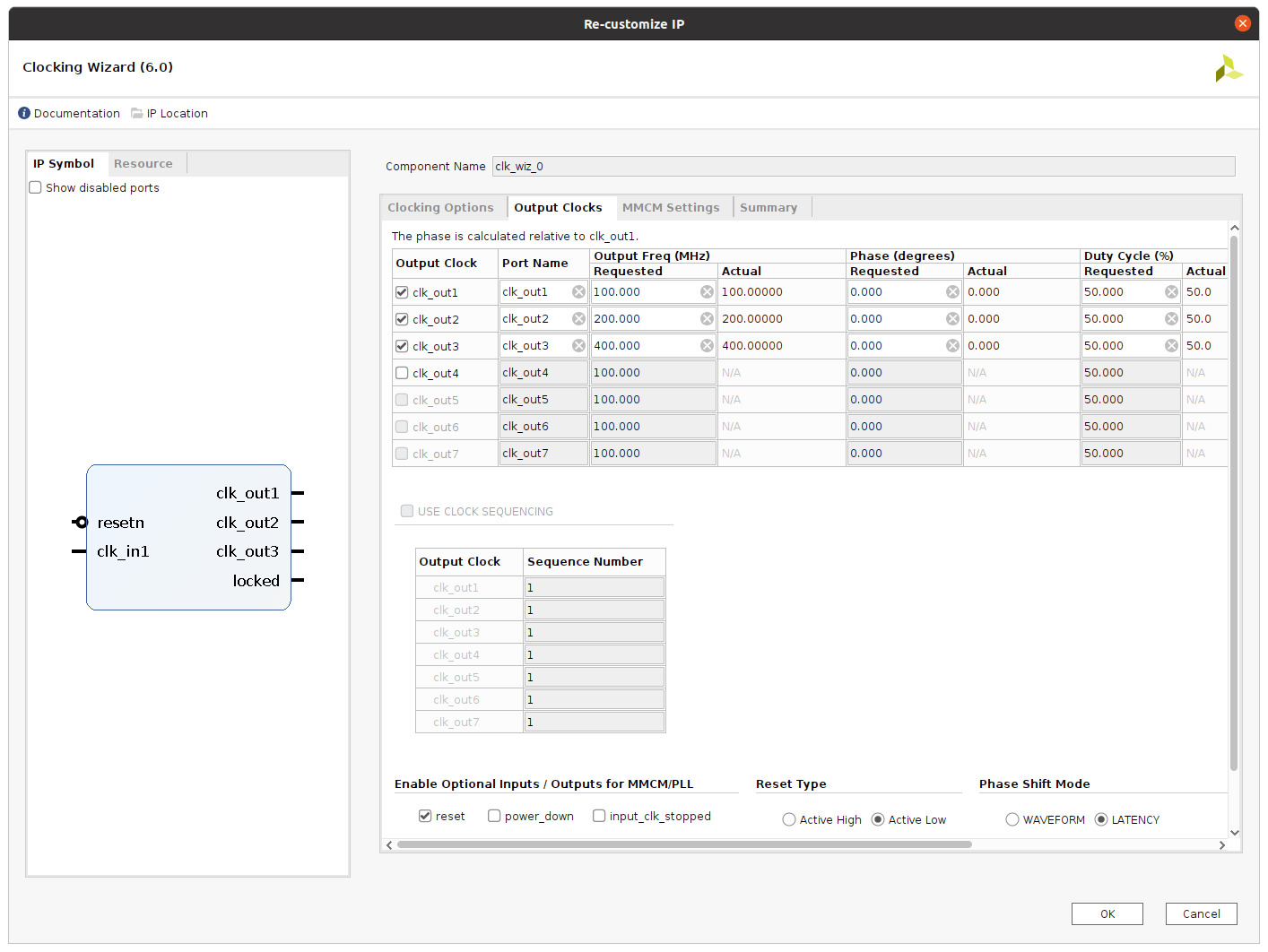

8- 将Clocking Wizard添加到模块设计中并双击clk_wiz_0 IP 模块以打开 Re-Customize IP 对话框

单击输出时钟选项卡。在输出时钟列中启用 clk_out1 到 clk_out3。如下设置请求的输出频率:

- clk_out1至100 MHz

- clk_out2至200 MHz

- clk_out3至400 MHz

在对话框的底部,将重置类型设置为低电平有效。

# Equivalent TCL command for adding the Clocking Wizard

create_bd_cell -type ip -vlnv xilinx.com:ip:clk_wiz:6.0 clk_wiz_0

set_property -dict [list CONFIG.CLKOUT2_USED {true} CONFIG.CLKOUT3_USED {true} CONFIG.CLKOUT2_REQUESTED_OUT_FREQ {200.000} CONFIG.CLKOUT3_REQUESTED_OUT_FREQ {400.000} CONFIG.RESET_TYPE {ACTIVE_LOW} CONFIG.MMCM_CLKOUT1_DIVIDE {6} CONFIG.MMCM_CLKOUT2_DIVIDE {3} CONFIG.NUM_OUT_CLKS {3} CONFIG.RESET_PORT {resetn} CONFIG.CLKOUT2_JITTER {102.086} CONFIG.CLKOUT2_PHASE_ERROR {87.180} CONFIG.CLKOUT3_JITTER {90.074} CONFIG.CLKOUT3_PHASE_ERROR {87.180}] [get_bd_cells clk_wiz_0]

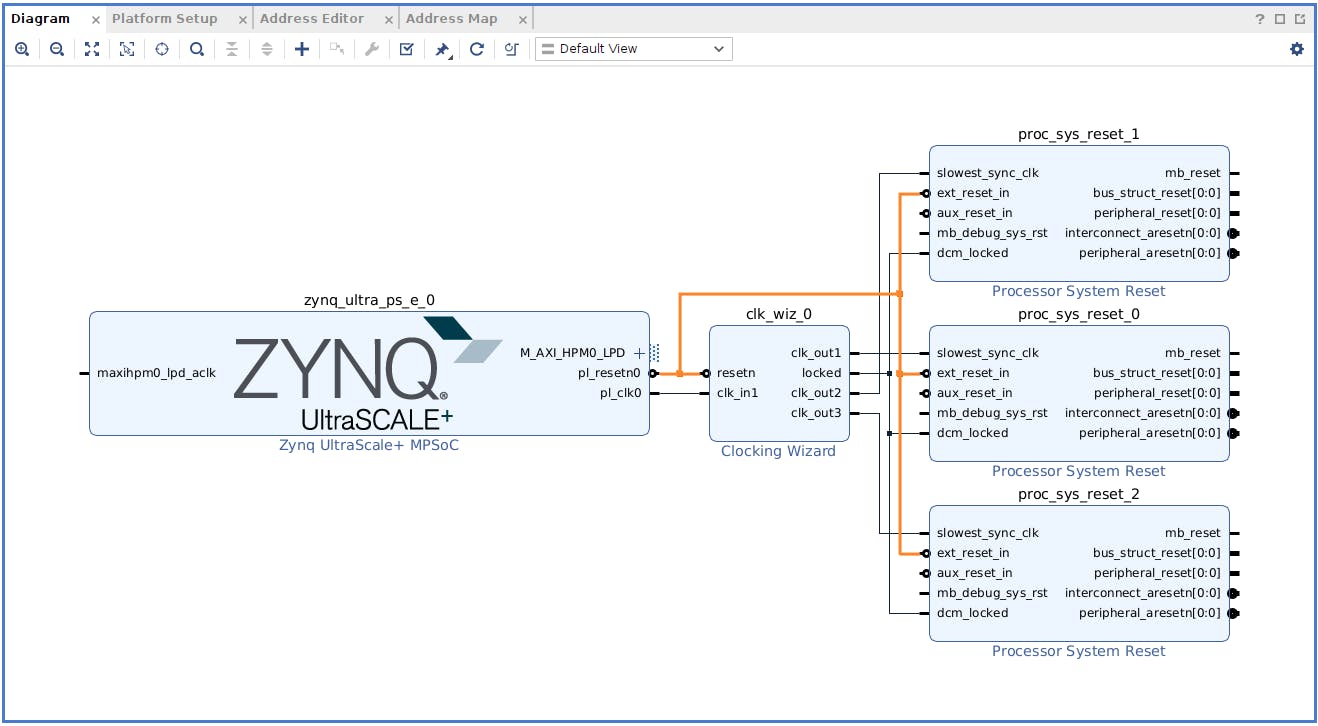

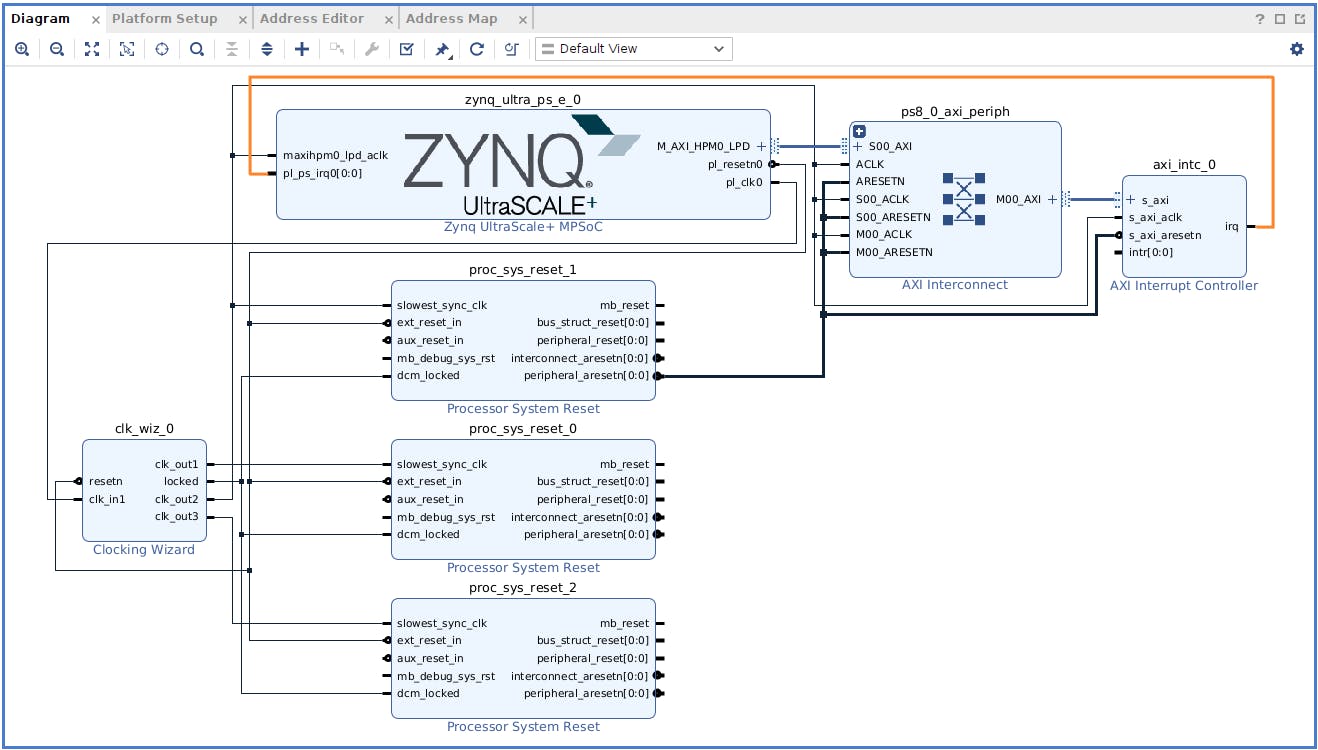

9- 在设计中添加三个处理器系统复位IP 并将 IP 连接在一起,如下图所示

# Adding 3 Processor System Reset IPs

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_0

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_1

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_2

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_clk0] [get_bd_pins clk_wiz_0/clk_in1]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins clk_wiz_0/resetn]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_1/ext_reset_in]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_0/ext_reset_in]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_2/ext_reset_in]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out1] [get_bd_pins proc_sys_reset_0/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out2] [get_bd_pins proc_sys_reset_1/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out3] [get_bd_pins proc_sys_reset_2/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_1/dcm_locked]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_0/dcm_locked]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_2/dcm_locked]

regenerate_bd_layout

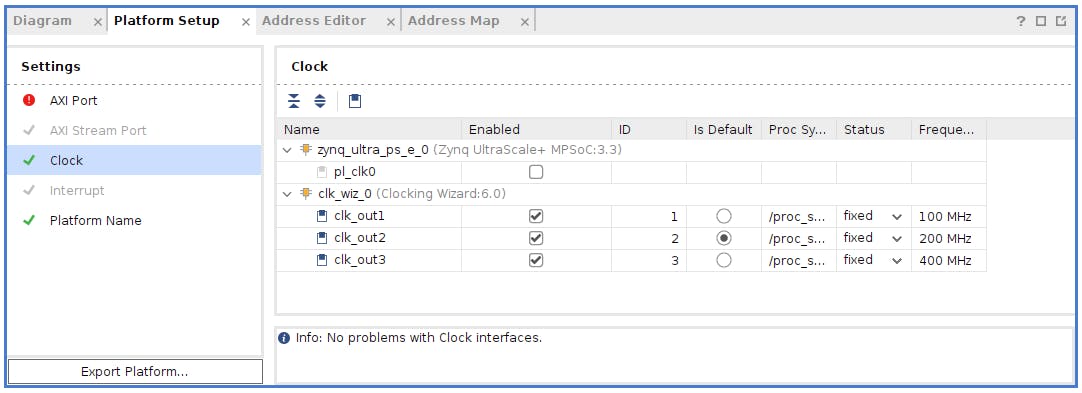

10-平台设置

为平台启用所有三个时钟。使用菜单窗口 -> 平台设置。将时钟 2 设置为默认值。

11-添加中断支持。

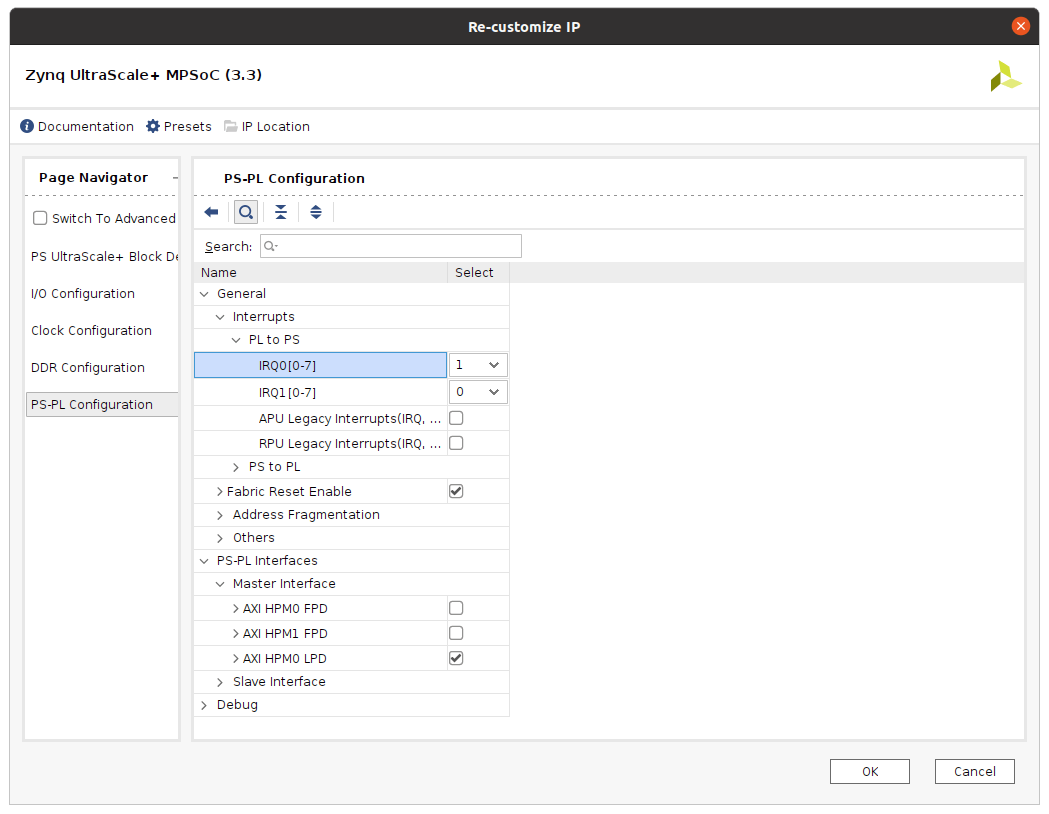

再次双击Zynq UltraScale+ MPSoC模块

- 选择PS-PL 配置 > PS-PL 接口 > 主接口

- 启用AXI HPM0 LPD选项

- 禁用AXI HPM0 FPD和AXI HPM1 FPD

- 启用常规 > 中断 > PL 到 PS > IRQ0[0-7]中断

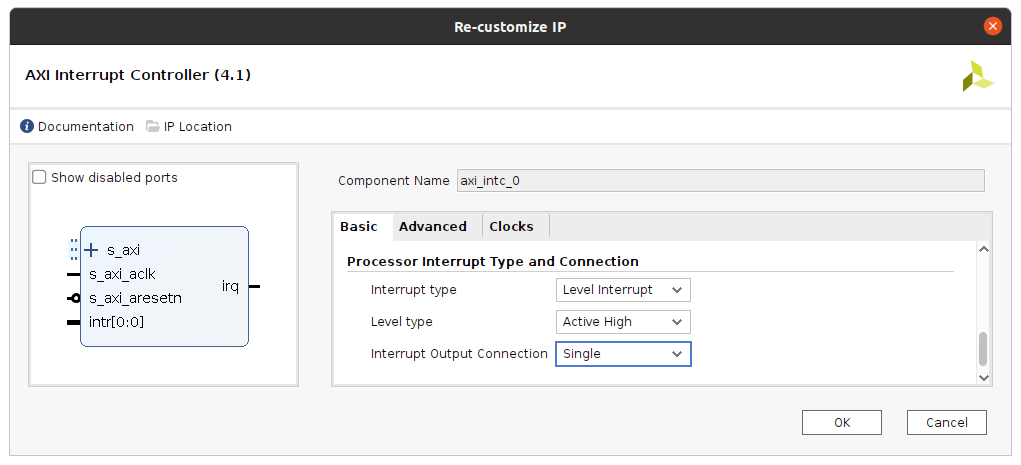

添加AXI 中断控制器 IP并将其配置为单中断输出连接。点击确定

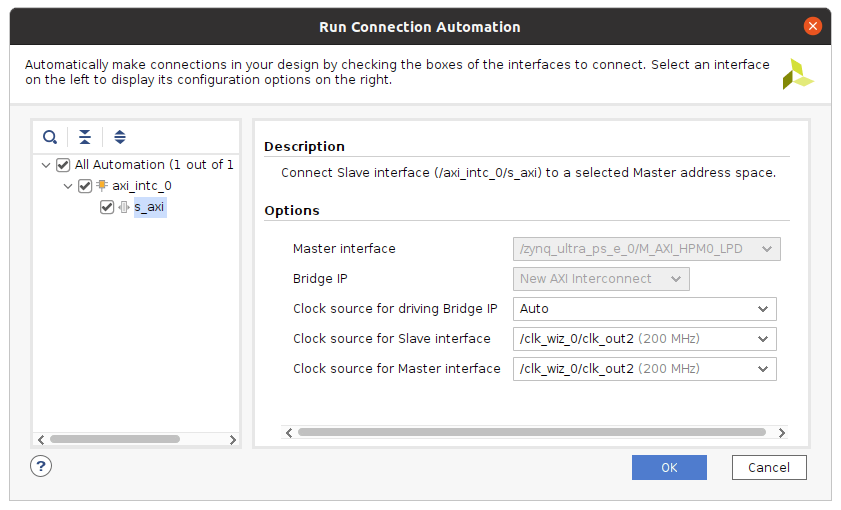

然后单击“运行连接自动化”链接。

选择 clk_out2 (200 MHz) 作为主从接口的源,然后按 OK。

将irq输出引脚连接到 Zynq 中断输入。

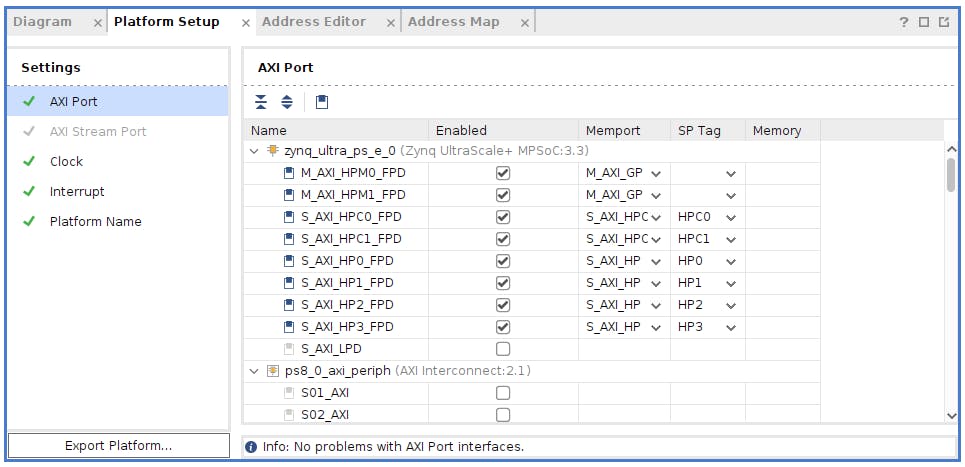

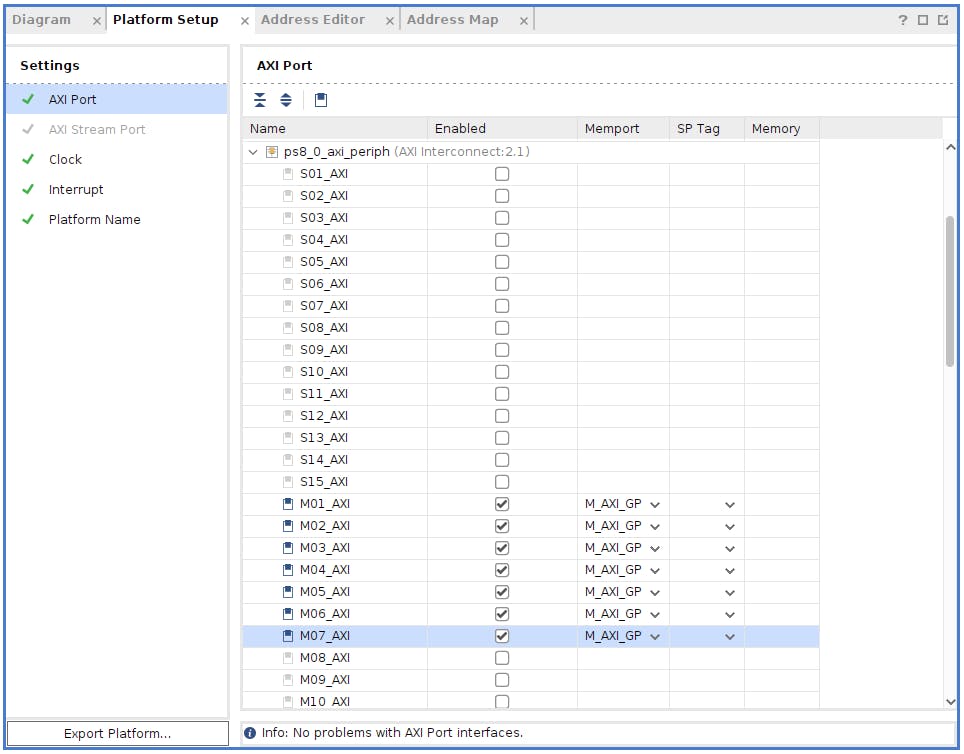

12- 在平台设置选项卡中为平台启用 AXI 接口:

- 启用zynq_ultra_ps_e_0下的前八个接口并为其设置SP Tag 。

- 在 ps8_0_axi_periph 下启用M01_AXI 到M07_IXA接口

等效的 TCL 命令:

# Enable AXI Interfaces in Platform Setup

set_property PFM.AXI_PORT {M_AXI_HPM0_FPD {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M_AXI_HPM1_FPD {memport "M_AXI_GP" sptag "" memory "" is_range "false"} S_AXI_HPC0_FPD {memport "S_AXI_HPC" sptag "HPC0" memory "" is_range "false"} S_AXI_HPC1_FPD {memport "S_AXI_HPC" sptag "HPC1" memory "" is_range "false"} S_AXI_HP0_FPD {memport "S_AXI_HP" sptag "HP0" memory "" is_range "false"} S_AXI_HP1_FPD {memport "S_AXI_HP" sptag "HP1" memory "" is_range "false"} S_AXI_HP2_FPD {memport "S_AXI_HP" sptag "HP2" memory "" is_range "false"} S_AXI_HP3_FPD {memport "S_AXI_HP" sptag "HP3" memory "" is_range "false"}} [get_bd_cells /zynq_ultra_ps_e_0]

set_property PFM.AXI_PORT {M01_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M02_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M03_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M04_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M05_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M06_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M07_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"}} [get_bd_cells /ps8_0_axi_periph]

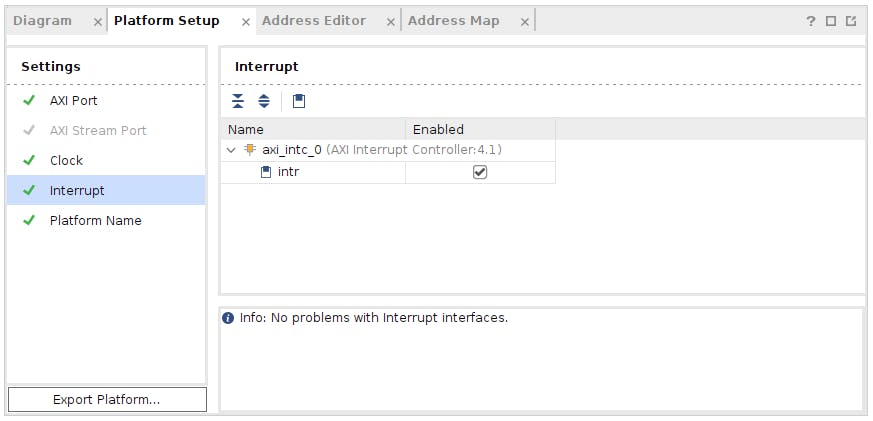

13-在中断选项卡中,启用intr

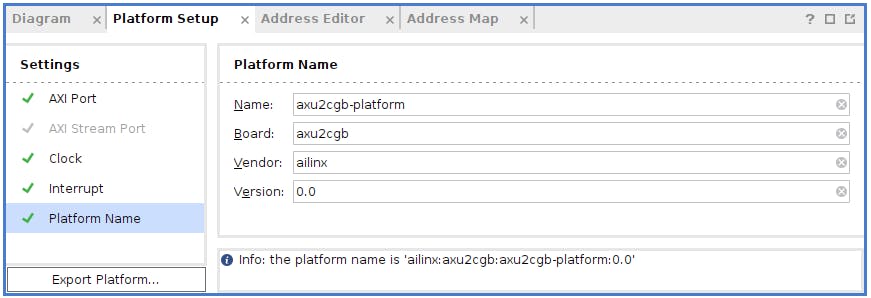

14-更新平台名称

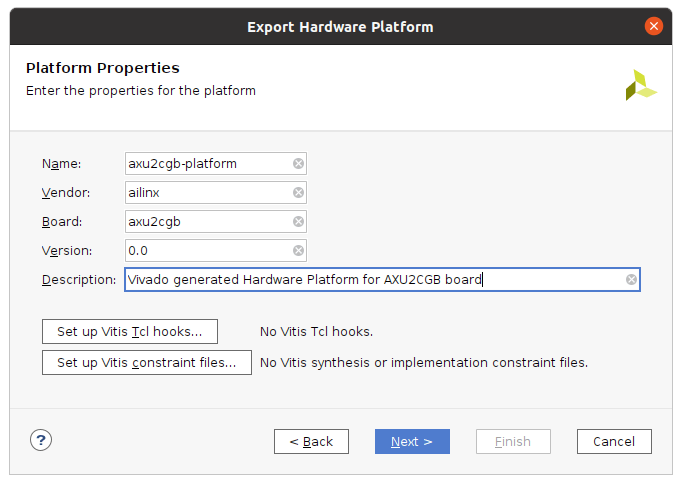

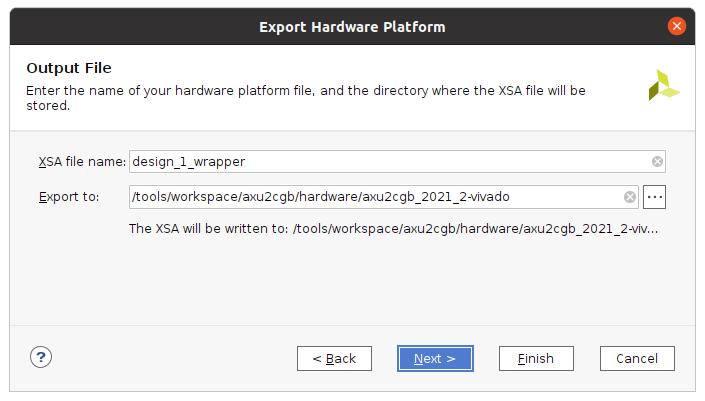

15-出口硬件-XSA

- 验证块设计 - 按F6 (忽略 axi_intc_0/intr 警告)

- 创建 HDL Wrapper (在Source选项卡中,右键单击 Design Sources 组中的 design_1.bd 文件)

- Generate Block Design并选择Synthesis Options to Global。然后单击生成。

- 生成比特流- 单击Flow Navigator窗口中的按钮。

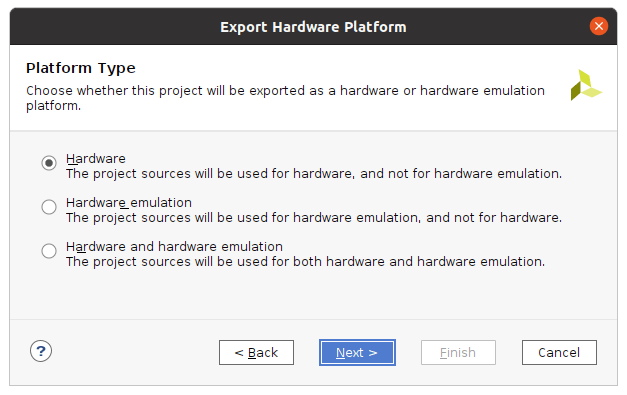

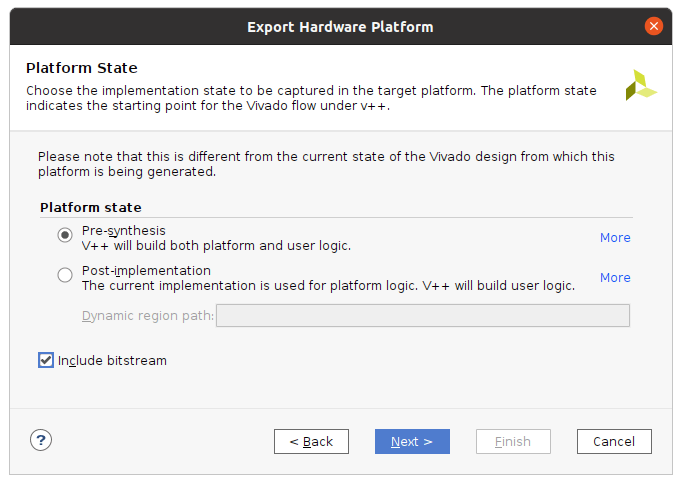

- 导出平台- 单击Flow Navigator窗口中的按钮。选择Hardware ,然后Pre-synthesis并启用Include bitstream。

这是创建平台的第一个 Vivado 部分的结束。您现在可以关闭 Vivado 程序。

要继续,请转到项目的第二个 - PetaLinux 部分:

快速通道

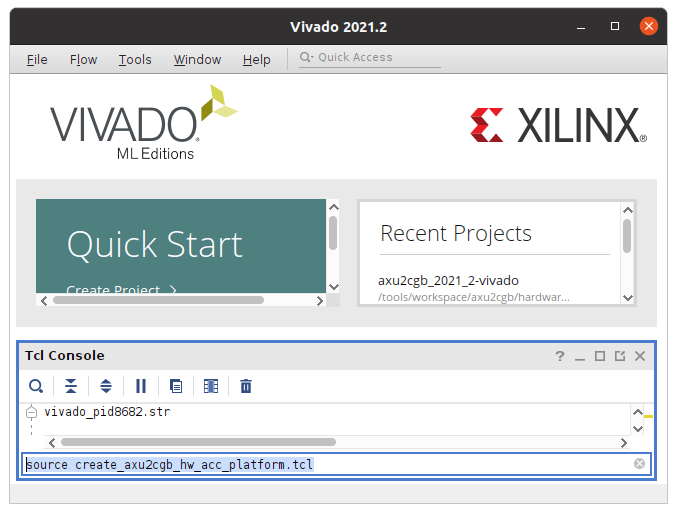

如果您被困在某个地方,可以附加一个 TCL 脚本来创建上述整个项目。

使用 source 命令在 Tcl 控制台窗口中启动 Vivado 后立即运行脚本。

source create_axu2cgb_hw_acc_platform.tcl

当 TCL 脚本完成时:

- 验证块设计- 按 F6

- 创建 HDL 包装器

- Generate Block Design并选择Synthesis Options to Global。

- 生成比特流

- Export the Platform 并选择Hardware , Pre-synthesis并启用Include bitstream。

下一步

- LabView工具包WebSocket-API主机下载 68次下载

- AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第4部分

- AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第3部分

- 如何在arduino IDE上安装STM32的开发板工具包 3次下载

- AXU2CG FPGA XLINX核心板原理图 36次下载

- GNU Radio开源软件无线电平台的简介

- 如何使用KEELOQ3开发工具包作为开发工具来在目标板上仿真和调试固件

- 如何使用入门工具包开发工具在目标板上仿真和调试固件的详细资料概述

- 如何使用PIC32MX1/2/5入门工具包在目标板上仿真和调试固件的详细概述

- 如何使用高性能工具包作为开发工具在目标板上仿真和调试固件

- PIC32以太网入门工具包的中文介绍和使用的详细概述

- 如何使用PIC32MZ嵌入式连接(EC)入门工具包的详细使用说明

- 电压基准如何影响ADC性能,第2部分 10次下载

- 使用触摸传感器的设备的输入和控制,第2部分:控制器和开发包 5次下载

- 多媒体启动工具包

- 软件无线电安全之GNU Radio基础知识 3079次阅读

- NPOI WEG报表工具包简介 808次阅读

- ADI公司设计工具:ADIsimRF第2部分 948次阅读

- ADC眼中的虚拟评估,第2部分 624次阅读

- Arm®ML处理器 嵌入式评估工具包介绍 1797次阅读

- 基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 开发板评测 9051次阅读

- 实时控制技术满足实时工业通信发展的需求 —— 第2部分 993次阅读

- firefly NCC S1--MDK - SSD模型工具包介绍 2068次阅读

- 米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍 2975次阅读

- 北大语言计算与机器学习研究组推出一套全新中文分词工具包pkuseg 3647次阅读

- Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞 2620次阅读

- Zynq UltraScale+ MPSoC 上的多个Linux UIO设计 3219次阅读

- 细数工具包Kanzi® UI及Kanzi Connect®其中每个插件实现的功能 1w次阅读

- 无源元件并非真的“无源”:第1部分——电容 2433次阅读

- 混合信号系统接地揭秘之第二部分 1663次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论