资料介绍

描述

目标:该项目的主要目标是展示高级综合设计流程在实现数字系统中的能力和能力。

由于这是我在 hackster 中的第一个项目,因此我尝试逐步解释所有细节。如果您有兴趣学习高级合成技术来设计数字系统,请参阅此处。

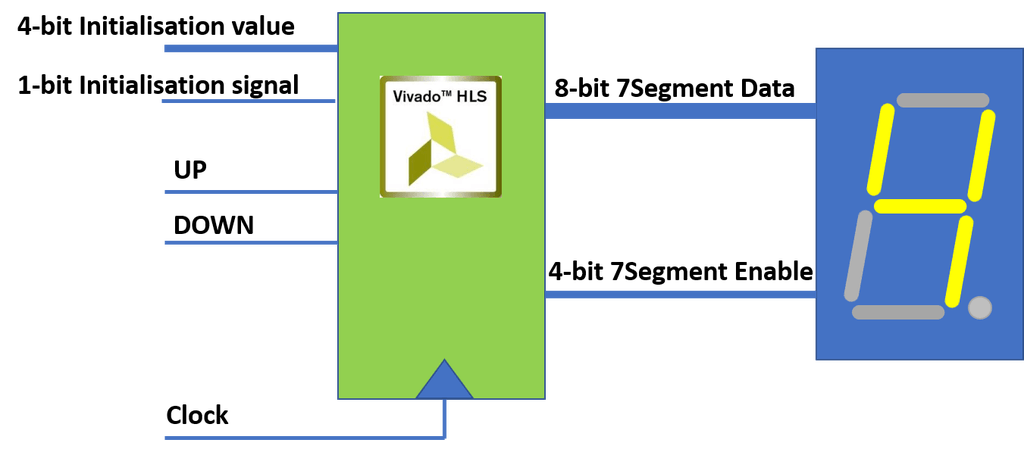

项目描述:在这个项目中,我将设计一个带有初始化信号的 0-9 加/减计数器。图 1 显示了该项目的概览。

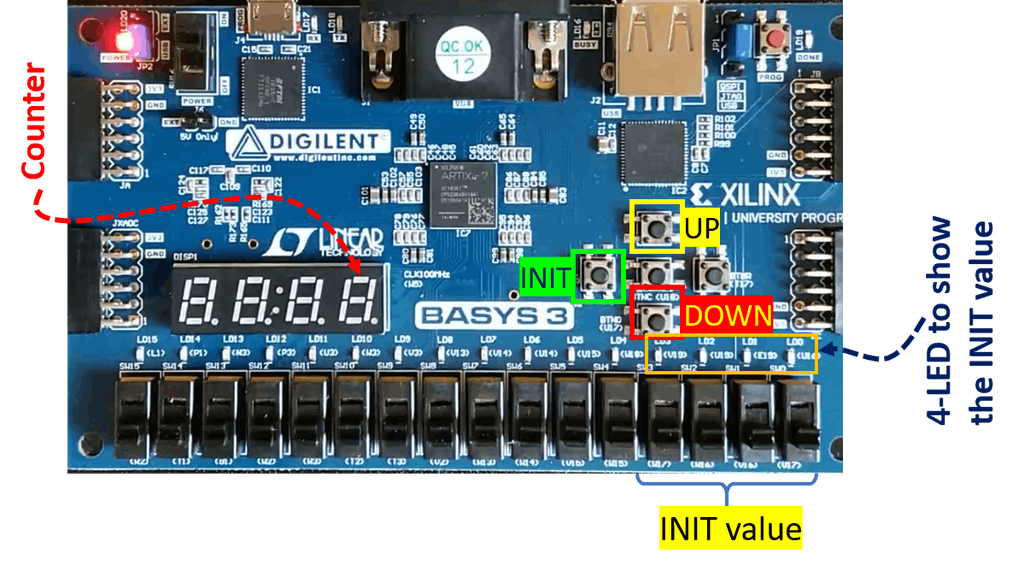

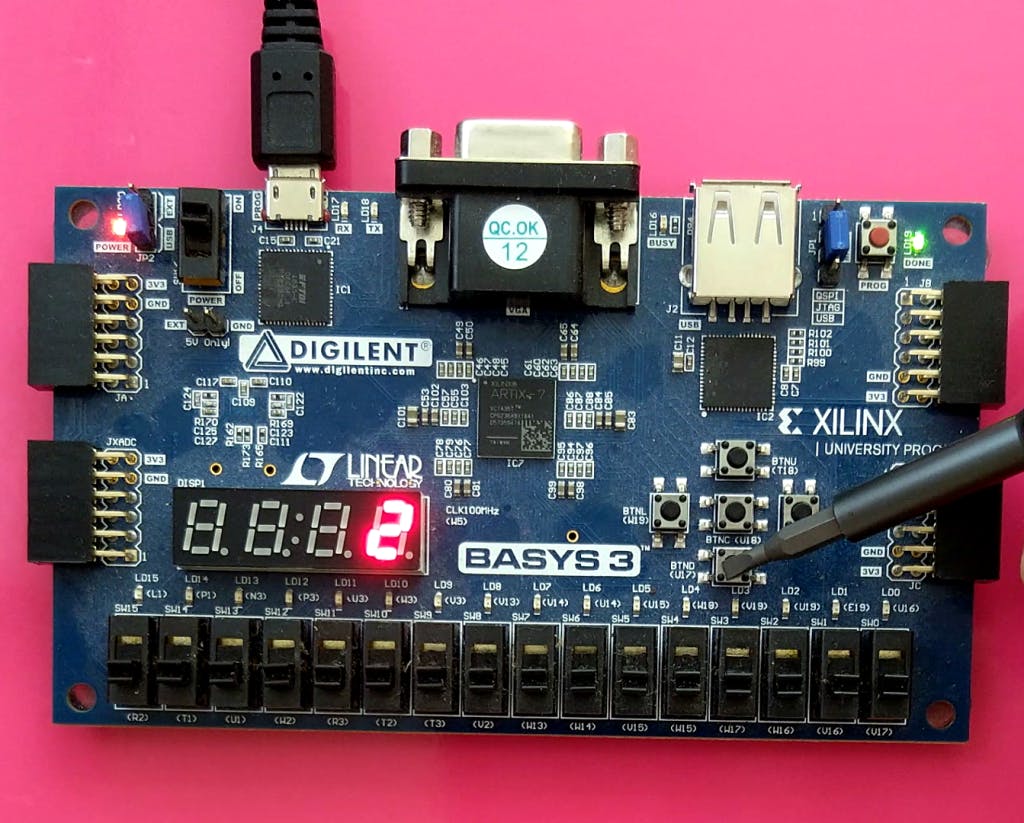

为了实现这个项目,我使用了 Vivado Design Suite – HLx Editions 提供的 Xilinx HLS 平台。此外,我将使用 Basys 3 评估板作为目标 FPGA 平台。图 2 显示了板上最终递增/递减计数器的布局。右侧的 7 段显示计数器。UP 按钮用于向上计数,DOWN 按钮用于向下计数。INIT 按钮初始化计数器。用“INIT value”表示的四个滑动开关用于输入初始化编号。此外,四个 LED 显示该值。

我们分三个阶段来实施这个项目:C/C++ 描述、逻辑综合和电路板编程。

第 1 阶段:C/C++ 描述(Vivado-HLS 项目)

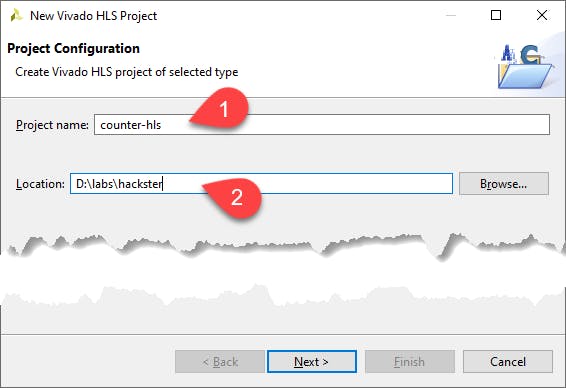

1- 运行 Vivado-HLS IDE 并创建一个新项目。

2- 在创建新项目向导的第一页中,插入“counter-vhls”作为项目名称,并为项目文件选择适当的位置。

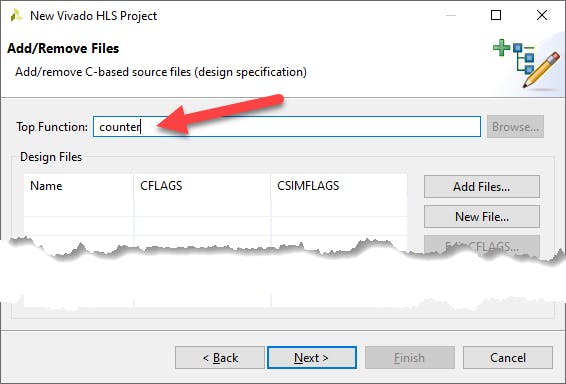

3-选择“计数器”作为顶级功能名称。

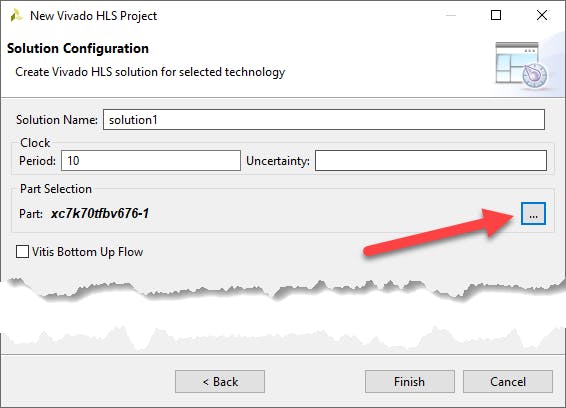

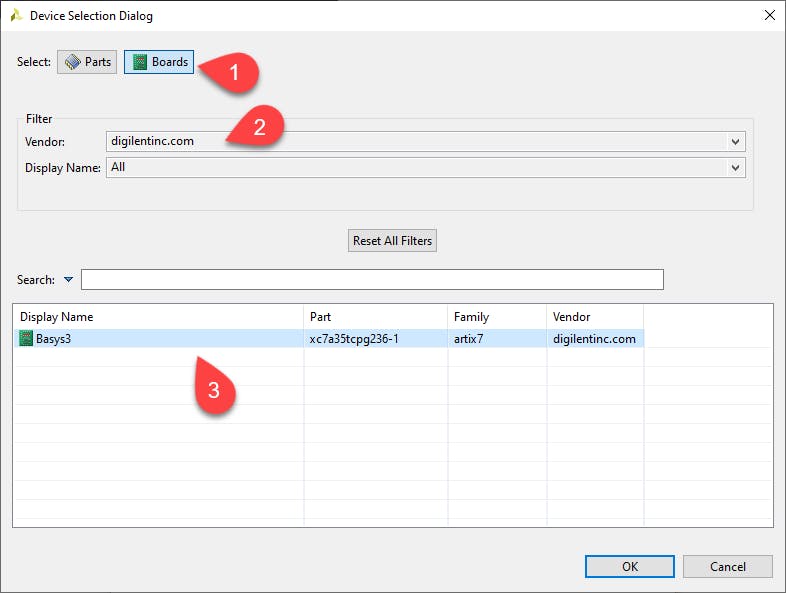

4- 在“解决方案配置”页面中,单击省略号按钮选择 FPGA 平台。

5- 设备选择对话框将打开。点击Boards,找到digilent vendor,选择Basys3 board,点击OK。

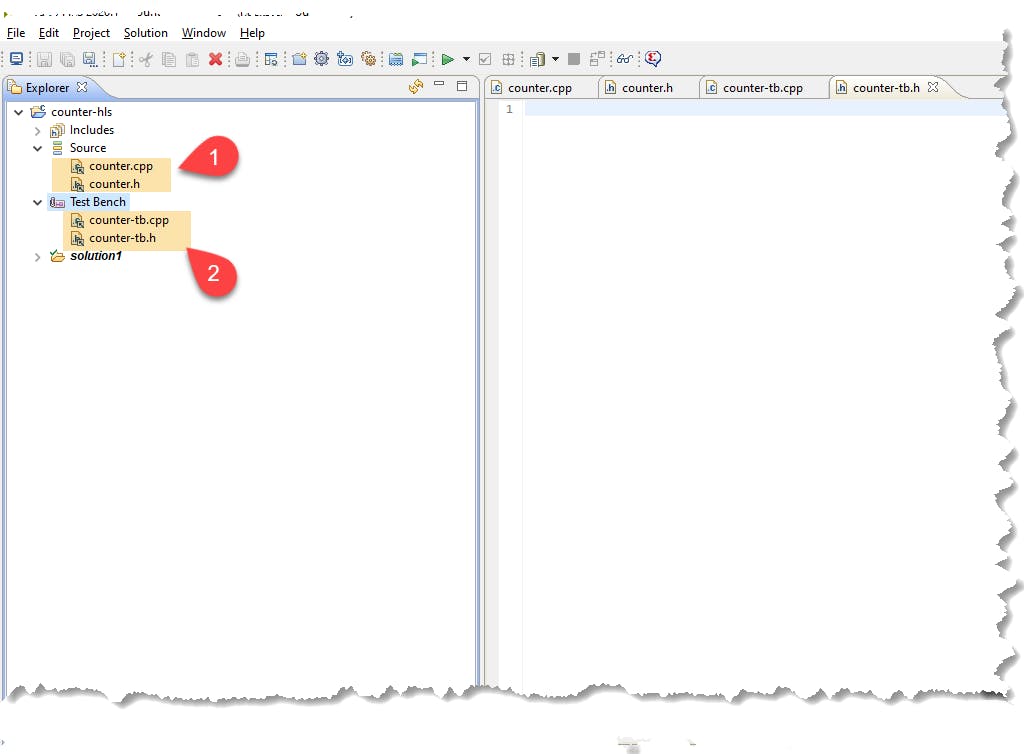

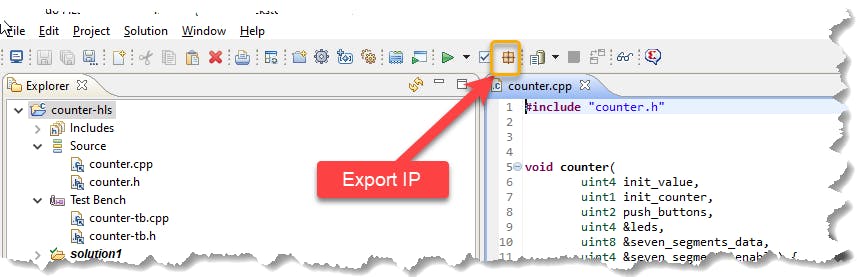

6- 在 Source 文件夹下创建两个名为“counter.cpp”和“counter.h”的新文件。

7- 在 Test Bench 文件夹下创建两个名为“counter-tb.cpp”和“counter-tb.h”的新文件。

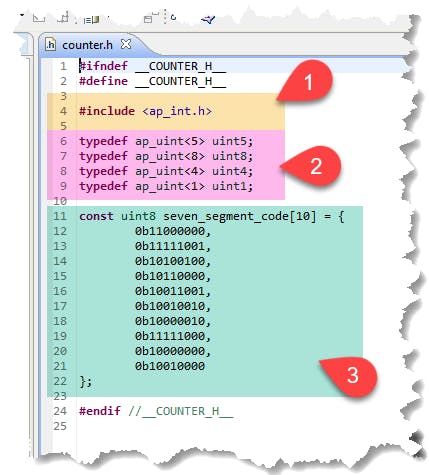

8-让我们编写设计头文件如下。如下图所示,该文件中的代码分为三个部分:

1- 首先,由于我们要使用 HLS 任意精度数据类型,我们应该包含“ap_int.h”头文件。2- 其次,我们定义了一些稍后在设计中使用的数据类型 3- 最后,我们定义了一个常量数组,用于保存对应于从 0 到 9 的数字的 7 段代码。

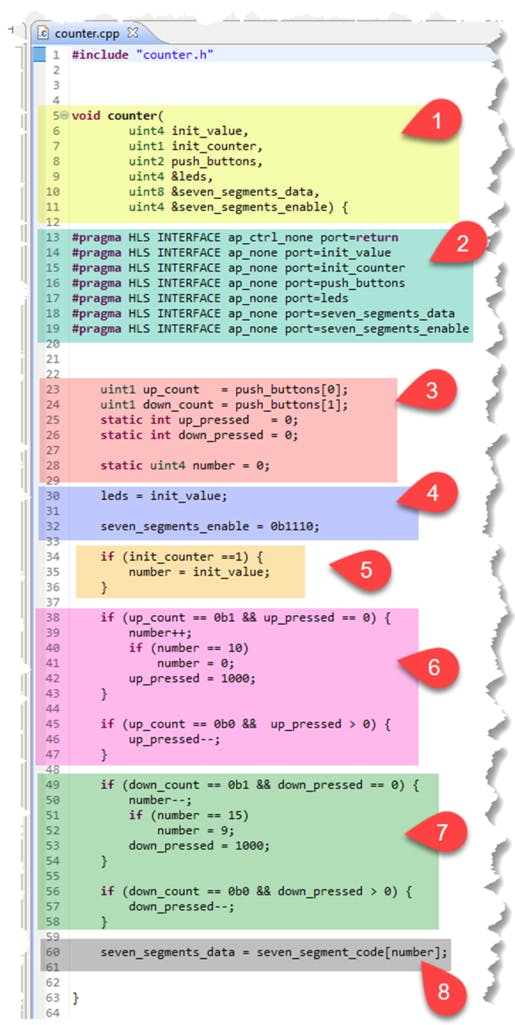

9- 设计源文件包含顶层功能描述。它由八个部分组成。

1-顶级函数参数:该函数包含三个输入和两个输出参数。

init_value变量包含计数器初始值。

reset_counter变量确定何时应该初始化计数器。当它为 1 时,计数器获取init_value参数中的值。

push_buttons变量确定向上或向下计数。

Seven_segments_data变量包含对应于计数器状态的 7 段代码

Seven_segments_enable变量启用目标 7 段。

2-端口接口:本节定义与顶级函数参数对应的端口接口。这些接口定义了实现参数数据事务的硬件结构。由于我们有一个简单的设计,并且我们希望简单的电线实现参数,我选择了ap_none作为接口模式。

3-声明变量:在这里,我声明了一些要在设计中使用的变量。如果按下 UP 按钮,up_count 变量将为1 。如果按下 DOWN 按钮,则 down_count 将为1 。up_pressed和down_pressed被声明为静态变量以保存按钮的历史记录。number变量保持计数器状态,因此定义为静态变量。

4-设置输出:此部分将 INIT 值发送到 LED 并启用右侧 7 段。

5-初始化:如果reset_counter信号被激活,这个if 语句初始化计数器状态。

6-向上计数:这部分由两个if 语句组成。第一个检查是否按下了向上按钮。第二个if检查 UP 按钮是否已被释放。

7-向下计数:这部分与向上计数部分非常相似。

8- 7 段码:最后一段发出计数器状态对应的 7 段码。

10- 现在,我们需要一个 C/C++ 测试平台来测试设计。可以在此处找到测试台文件。测试台分为三个步骤:

— 生成测试向量, — 将测试向量应用于设计, — 最后,将硬件输出与黄金模型的输出进行比较并报告任何差异

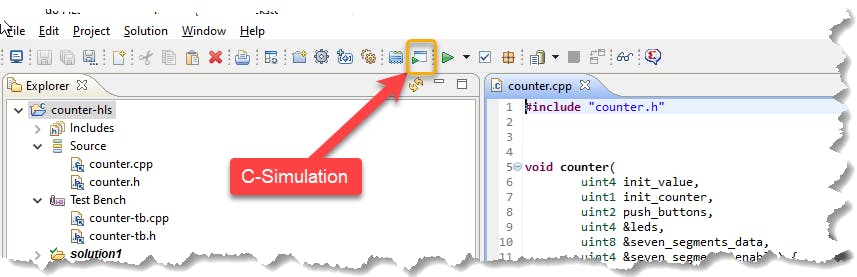

11- 现在我们可以通过单击工具栏中的图标来运行 C 模拟。

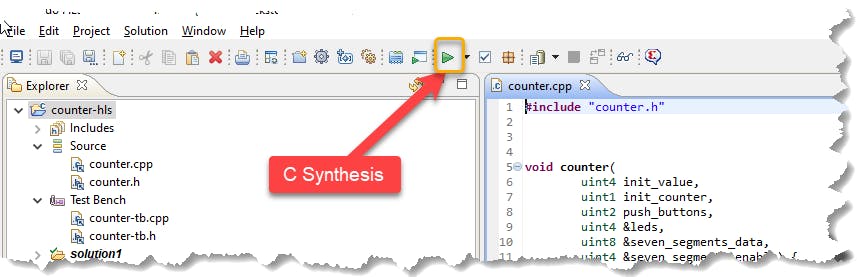

12-成功完成C-Simulation后,我们可以运行高级综合。

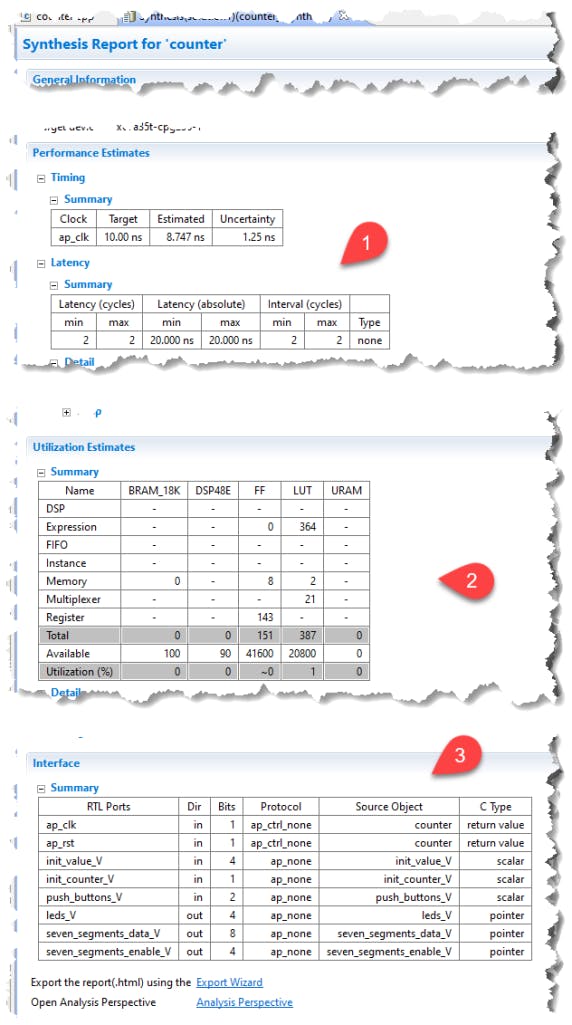

图 13 显示了综合报告的部分内容。它有三个主要部分:

1- 时序信息 2- 资源利用 3- 端口接口

13- 最后,我们应该通过单击其图标来生成和导出设计 RTL-IP。

第 2 阶段:逻辑综合(Vivado 项目)

现在,我们已准备好进行逻辑综合和生成 FPGA 比特流。

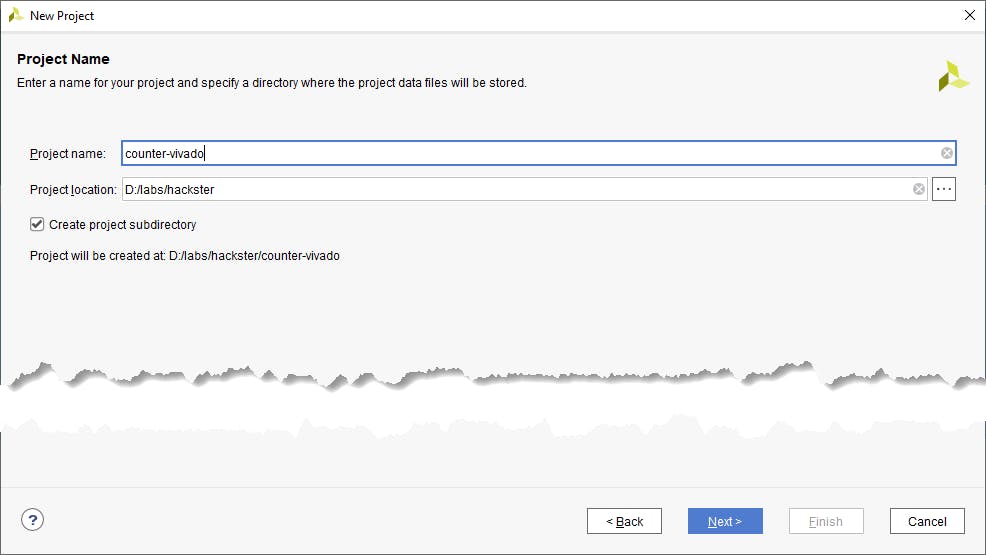

1-创建一个名为counter-vivado的新Vivado项目。请注意,该项目没有任何源文件。

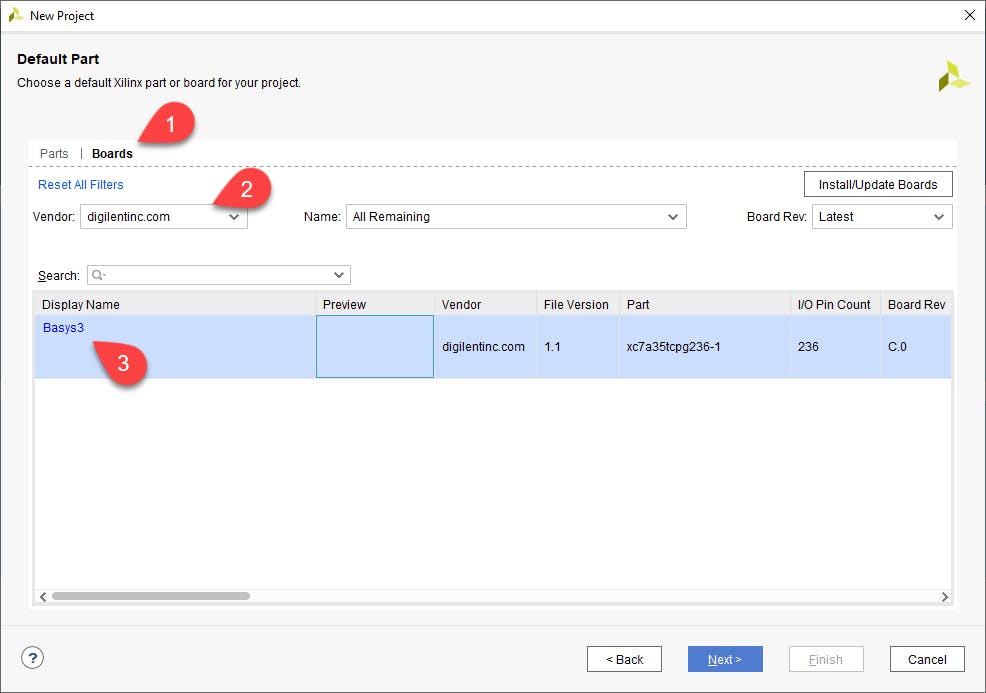

2- 不要忘记选择 Basys-3 板作为目标 FPGA。

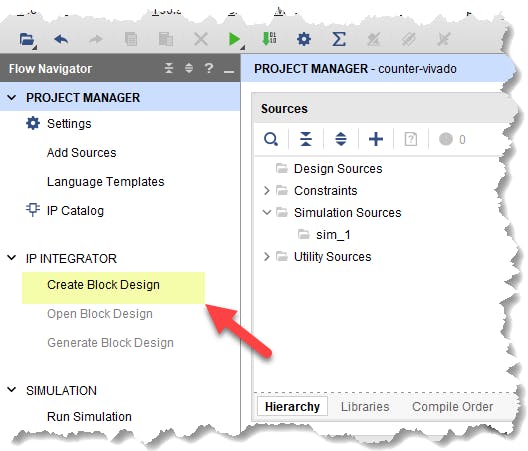

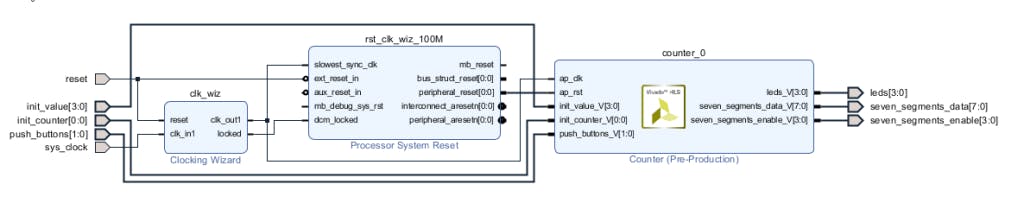

3-创建一个新的块设计

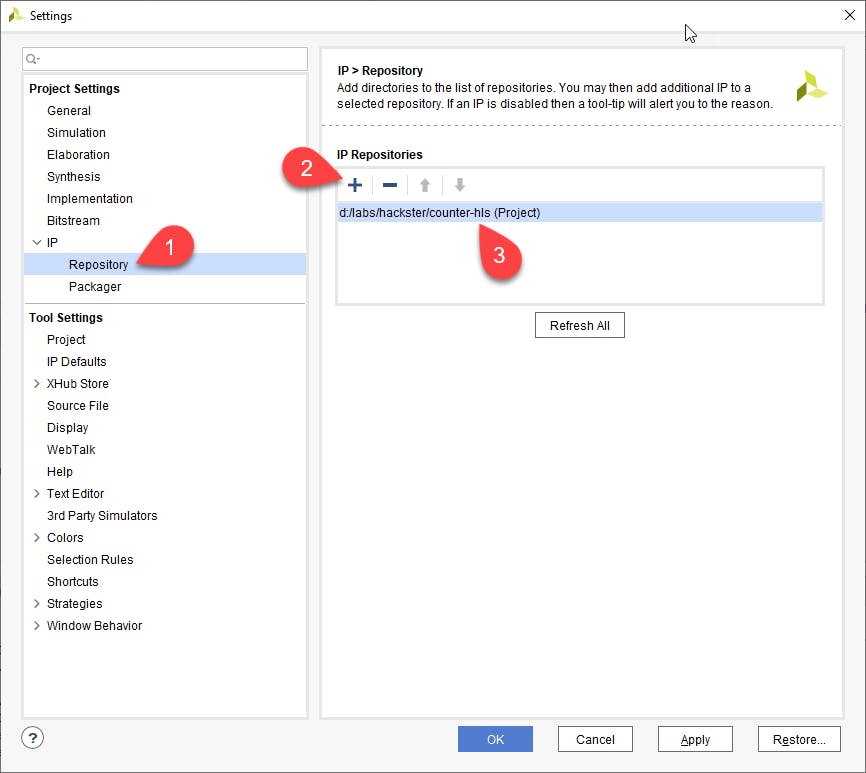

4-右键单击图表区域内的某处并选择“IP设置...”选项

5-然后单击设置对话框中IP下的存储库选项。然后点击右侧的加号,浏览到counter HLS项目文件夹。Vivado 在文件夹中搜索任何可能的 IP 并将其添加到其存储库中。

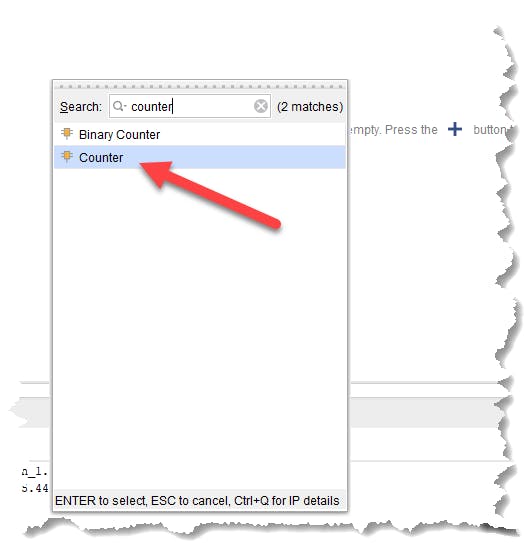

6- 右键单击图表区域内的某处并选择“添加..”选项。然后搜索计数器 IP 并将其添加到 vivado 项目中。

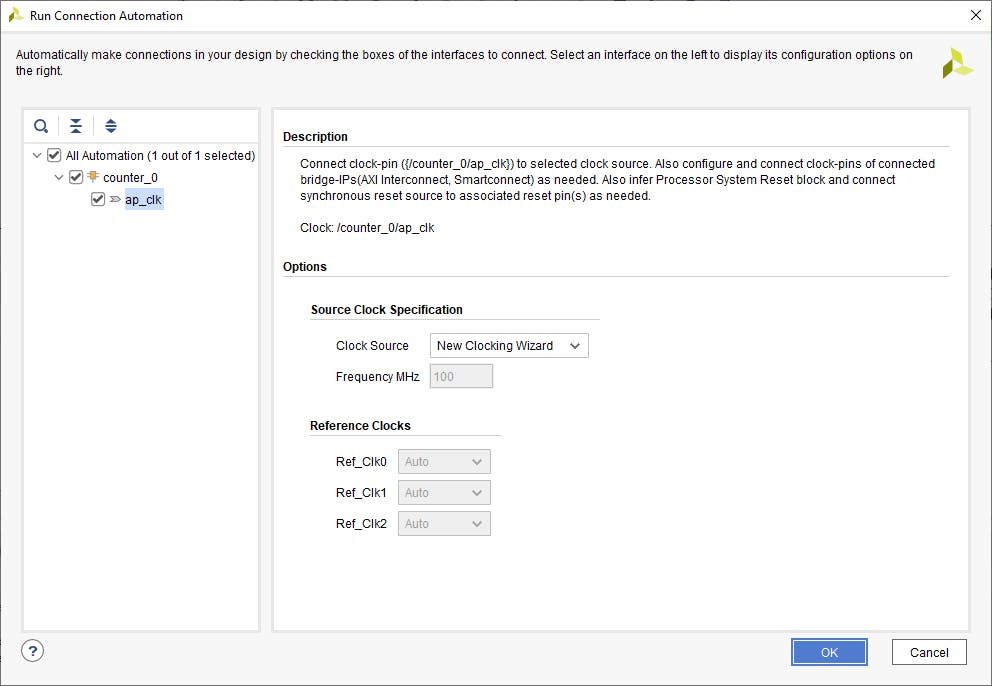

17- 单击图表区域顶部的“运行连接自动化”。

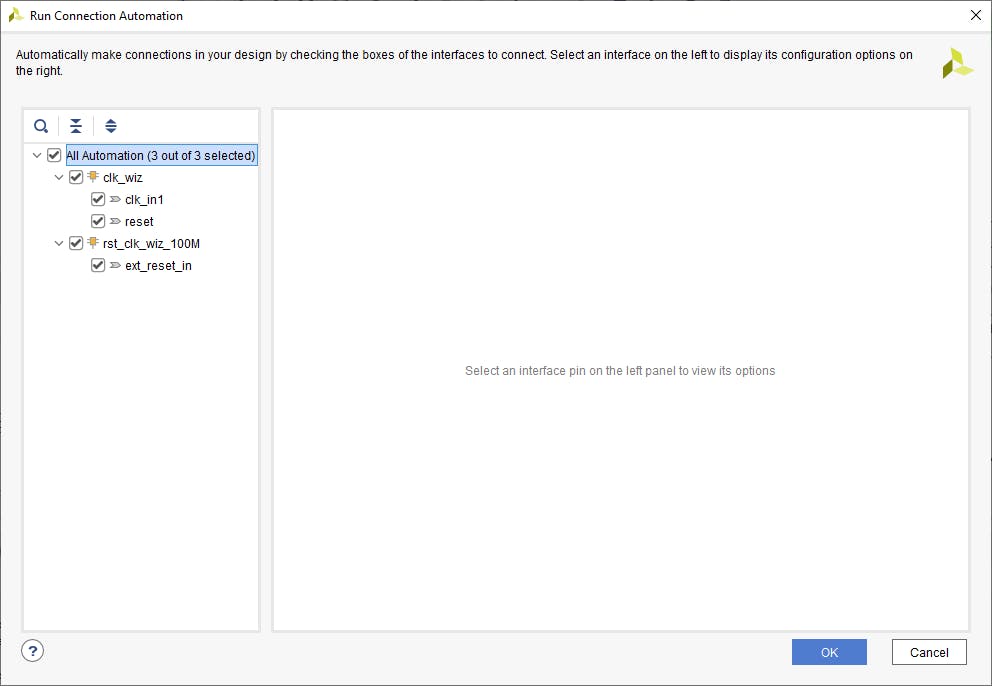

18- 再次单击图表区域顶部的“运行连接自动化”。

9- 在我们的计数器 IP 上选择未连接的端口并将它们设为外部(右键单击端口名称,您将在下拉菜单中看到“设为外部”选项)。

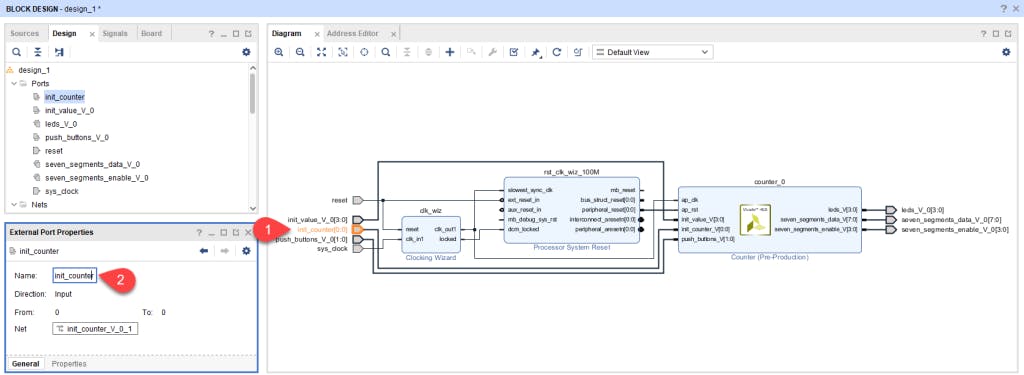

10-您可以通过选择端口并使用“外部端口属性”窗口来重命名端口。

init_counter_V_0 -----------> init_counter

push_buttons_V_0------------> push_buttons

init_value_V_0--------------> init_value

init_counter----------------> init_counter

leds_V_0--------------------> leds

seven_segments_data_V_0 ----> seven_segments_data

seven_segments_enable_V_0---> seven_segments_enable

11- 现在创建一个约束文件,并添加以下约束以将 IP 端口连接到具有适当 I/O 标准的 FPGA 引脚。

## Switches

set_property PACKAGE_PIN V17 [get_ports {init_value[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[0]}]

set_property PACKAGE_PIN V16 [get_ports {init_value[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[1]}]

set_property PACKAGE_PIN W16 [get_ports {init_value[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[2]}]

set_property PACKAGE_PIN W17 [get_ports {init_value[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[3]}]

# LEDs

set_property PACKAGE_PIN U16 [get_ports {leds[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN E19 [get_ports {leds[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property PACKAGE_PIN U19 [get_ports {leds[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property PACKAGE_PIN V19 [get_ports {leds[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

#7 segment display

set_property PACKAGE_PIN W7 [get_ports {seven_segments_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[0]}]

set_property PACKAGE_PIN W6 [get_ports {seven_segments_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[1]}]

set_property PACKAGE_PIN U8 [get_ports {seven_segments_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[2]}]

set_property PACKAGE_PIN V8 [get_ports {seven_segments_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[3]}]

set_property PACKAGE_PIN U5 [get_ports {seven_segments_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[4]}]

set_property PACKAGE_PIN V5 [get_ports {seven_segments_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[5]}]

set_property PACKAGE_PIN U7 [get_ports {seven_segments_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[6]}]

set_property PACKAGE_PIN V7 [get_ports seven_segments_data[7]]

set_property IOSTANDARD LVCMOS33 [get_ports seven_segments_data[7]]

set_property PACKAGE_PIN U2 [get_ports {seven_segments_enable[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[0]}]

set_property PACKAGE_PIN U4 [get_ports {seven_segments_enable[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[1]}]

set_property PACKAGE_PIN V4 [get_ports {seven_segments_enable[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[2]}]

set_property PACKAGE_PIN W4 [get_ports {seven_segments_enable[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[3]}]

#Buttons

set_property PACKAGE_PIN T18 [get_ports push_buttons[0]]

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[0]]

set_property PACKAGE_PIN W19 [get_ports init_counter[0]]

set_property IOSTANDARD LVCMOS33 [get_ports init_counter[0]]

set_property PACKAGE_PIN U17 [get_ports push_buttons[1]]

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[1]]

12- 现在右键单击图表区域内的某处并选择“验证设计”选项。

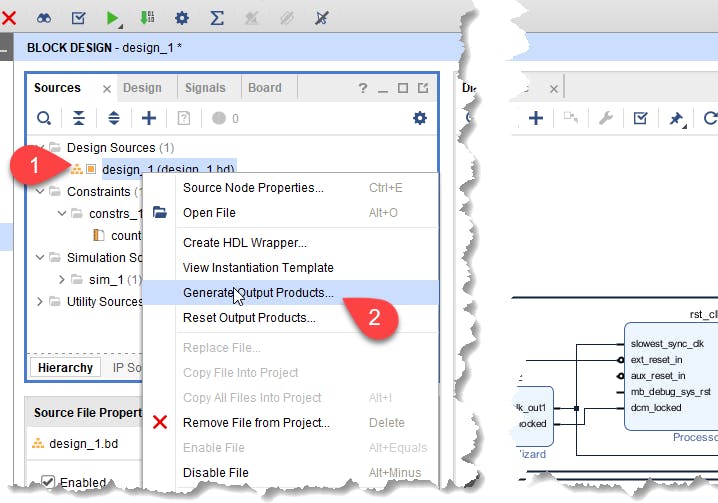

13-成功验证设计后,右键单击“Design Sources”文件夹下的“ design_1 ”并选择“Generate Output Products...”

14- 然后,再次右键单击“Design Sources”文件夹下的“design_1”并选择“Create HDL Wrapper...”

15- 现在单击左侧 Flow Navigator 中 PROGRAM and DEBUG 下的“Generate Bitstream”选项。

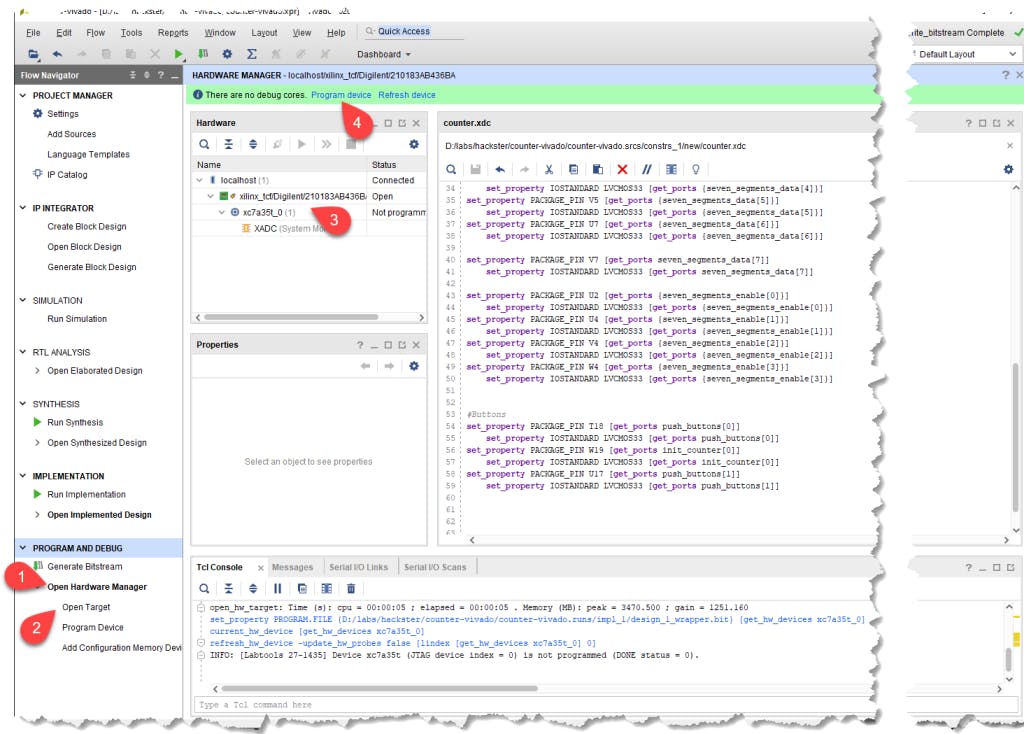

第 3 阶段:电路板编程

1- 最后,对电路板进行编程并检查设计。

如果您对使用 HLS 进行设计感兴趣,请查看具有FPGA 高级合成的数字系统设计:组合电路

- 简单的0至9计数器开源分享

- CC2530中断初始化和中断函数

- 单片机 -定时/计数器的初始化编程及应用

- 51单片机的计时器和计数器

- 51单片机单个数码管0-9循环秒计数

- 51单片机定时/计数器的工作原理

- C51单片机中的定时器和计数器的详细介绍

- 在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决

- 单片机计数器的应用资料说明

- 使用单片机设计0到9999计数器并带有暂停清零功能的程序资料免费下载

- 如何排除代码编写器Studio 2和2.10的初始化问题 4次下载

- SEED-DEC2812初始化函数说明 11次下载

- 定时计数器初始化 16次下载

- Proteus之定时_计数器0用于计数的应用 0次下载

- 单片直接驱动数码管的计数器程序 187次下载

- 同步计数器和异步计数器的区别 4665次阅读

- 字符型、指针型等变量等该如何初始化 1569次阅读

- 计数器怎么用 计数器的作用有哪些 5672次阅读

- SIMATIC S7-1500 PLC加减计数器简述 7248次阅读

- 什么是指定初始化? 935次阅读

- 西门子S7-300PLC高速计数器的计数方式简介 6506次阅读

- SCL语言之加计数-计数器函数S_CU 1709次阅读

- RT-Thread自动初始化机制 2722次阅读

- 如何使用SPI总线设计正交编码器计数器 4336次阅读

- 鸿蒙内核源码:内核空间是怎么初始化的? 1903次阅读

- 计数器函数S_CU的操作步骤 8791次阅读

- 单片机定时器/计数器的结构 8315次阅读

- 如何有效地对神经网络参数进行初始化 4142次阅读

- PCIe总线必须要先完成Flow Control初始化 7977次阅读

- 8253初始化程序分享_8253应用案例 2.2w次阅读

下载排行

本周

- 1EN60335-1安规标准 中文版本

- 1.86 MB | 53次下载 | 1 积分

- 2TDA7850音频功率放大器英文手册

- 0.39 MB | 1次下载 | 免费

- 3VCC启动电路(可下载)

- 748.32 KB | 1次下载 | 免费

- 460KW电机控制器硬件驱动电路设计(可下载)

- 720.01 KB | 1次下载 | 免费

- 5LTD1534RFN N沟道增强型功率MOSFET规格书

- 1.11 MB | 次下载 | 免费

- 6LT1702SI P沟道增强型功率MOSFET规格书

- 1.04 MB | 次下载 | 免费

- 7LT1713SI N沟道增强型功率MOSFET规格书

- 0.85 MB | 次下载 | 免费

- 8反电动势到底如何来理解?(可下载)

- 1.63 MB | 次下载 | 免费

本月

- 1STM32CubeMX用于STM32配置和初始化C代码生成

- 21.90 MB | 626次下载 | 免费

- 2STM32开发板教程之STM32开发指南免费下载

- 24.88 MB | 176次下载 | 3 积分

- 3EN60335-1安规标准 中文版本

- 1.86 MB | 53次下载 | 1 积分

- 4OAH0428最新规格书(中文)

- 2.52 MB | 28次下载 | 10 积分

- 5Altium-常用3D封装库(Step)接插件篇

- 4.95 MB | 26次下载 | 免费

- 6UHV系列雷电冲击电压发生器试验装置详细说明使用

- 1.07 MB | 17次下载 | 免费

- 7介绍一些常用的电子元器件

- 3.20 MB | 8次下载 | 免费

- 8麻将机升降电路

- 0.12 MB | 6次下载 | 1 积分

总榜

- 1matlab软件下载入口

- 未知 | 935124次下载 | 10 积分

- 2开源硬件-PMP21529.1-4 开关降压/升压双向直流/直流转换器 PCB layout 设计

- 1.48MB | 420063次下载 | 10 积分

- 3Altium DXP2002下载入口

- 未知 | 233088次下载 | 10 积分

- 4电路仿真软件multisim 10.0免费下载

- 340992 | 191371次下载 | 10 积分

- 5十天学会AVR单片机与C语言视频教程 下载

- 158M | 183336次下载 | 10 积分

- 6labview8.5下载

- 未知 | 81583次下载 | 10 积分

- 7Keil工具MDK-Arm免费下载

- 0.02 MB | 73814次下载 | 10 积分

- 8LabVIEW 8.6下载

- 未知 | 65988次下载 | 10 积分

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论