完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > DDR2

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力(即:4bit数据读预取)。换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

由于DDR2标准规定所有DDR2内存均采用FBGA封装形式,而不同于广泛应用的TSOP/TSOP-Ⅱ封装形式,FBGA封装可以提供了更为良好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了坚实的基础。回想起DDR的发展历程,从第一代应用到个人电脑的DDR200经过DDR266、DDR333到今天的双通道DDR400技术,第一代DDR的发展也走到了技术的极限,已经很难通过常规办法提高内存的工作速度;随着Intel最新处理器技术的发展,前端总线对内存带宽的要求是越来越高,拥有更高更稳定运行频率的DDR2内存将是大势所趋。

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力(即:4bit数据读预取)。换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

由于DDR2标准规定所有DDR2内存均采用FBGA封装形式,而不同于广泛应用的TSOP/TSOP-Ⅱ封装形式,FBGA封装可以提供了更为良好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了坚实的基础。回想起DDR的发展历程,从第一代应用到个人电脑的DDR200经过DDR266、DDR333到今天的双通道DDR400技术,第一代DDR的发展也走到了技术的极限,已经很难通过常规办法提高内存的工作速度;随着Intel最新处理器技术的发展,前端总线对内存带宽的要求是越来越高,拥有更高更稳定运行频率的DDR2内存将是大势所趋。

种类区别

延迟问题

从上表可以看出,在同等核心频率下,DDR2的实际工作频率是DDR的两倍。这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。换句话说,虽然DDR2和DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但DDR2拥有两倍于DDR的预读取系统命令数据的能力。也就是说,在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以达到400MHz。这样也就出现了另一个问题:在同等工作频率的DDR和DDR2内存中,后者的内存延时要慢于前者。举例来说,DDR 400和DDR2-400具有相同的延迟,而后者具有高一倍的带宽。实际上,DDR2-400和DDR 400具有相同的带宽,它们都是3.2GB/s,但是DDR400的核心工作频率是200MHz,而DDR2-400的核心工作频率是100MHz,也就是说DDR2-400的延迟要高于DDR400。

封装

DDR2内存技术最大的突破点其实不在于用户们所认为的两倍于DDR的传输能力,而是在采用更低发热量、更低功耗的情况下,DDR2可以获得更快的频率提升,突破标准DDR的400MHZ限制。DDR内存通常采用TSOP芯片封装形式,这种封装形式可以很好的工作在200MHz上,当频率更高时,它过长的管脚就会产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。这也就是DDR的核心频率很难突破275MHZ的原因。而DDR2内存均采用FBGA封装形式。不同于广泛应用的TSOP封装形式,FBGA封装提供了更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了良好的保障。DDR2内存采用1.8V电压,相对于DDR标准的2.5V,降低了不少,从而提供了明显的更小的功耗与更小的发热量,这一点的变化是意义重大的。

双通道内存

需要INTEL芯片组的支持,内存的CAS延迟、容量需要相同。不过,INTEL的弹性双通道的出现使双通道的形成条件更加宽松,不同容量的内存甚至都能组建双通道除了以上所说的区别外,DDR2还引入了三项新的技术,它们是OCD、ODT和Post CAS。

离线驱动

OCD(Off-Chip Driver):也就是所谓的离线驱动调整,DDR Ⅱ通过OCD可以提高信号的完整性。DDR Ⅱ通过调整上拉(pull-up)/下拉(pull-down)的电阻值使两者电压相等。使用OCD通过减少DQ-DQS的倾斜来提高信号的完整性;通过控制电压来提高信号品质。

终结电阻器

ODT:ODT是内建核心的终结电阻器。我们知道使用DDR SDRAM的主板上面为了防止数据线终端反射信号需要大量的终结电阻。它大大增加了主板的制造成本。实际上,不同的内存模组对终结电路的要求是不一样的,终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低但是信噪比也较低;终结电阻高,则数据线的信噪比高,但是信号反射也会增加。因此主板上的终结电阻并不能非常好的匹配内存模组,还会在一定程度上影响信号品质。DDR2可以根据自己的特点内建合适的终结电阻,这样可以保证最佳的信号波形。使用DDR2不但可以降低主板成本,还得到了最佳的信号品质,这是DDR不能比拟的。

利用效率

Post CAS:它是为了提高DDR Ⅱ内存的利用效率而设定的。在Post CAS操作中,CAS信号(读写/命令)能够被插到RAS信号后面的一个时钟周期,CAS命令可以在附加延迟(Additive Latency)后面保持有效。原来的tRCD(RAS到CAS和延迟)被AL(Additive Latency)所取代,AL可以在0,1,2,3,4中进行设置。由于CAS信号放在了RAS信号后面一个时钟周期,因此ACT和CAS信号永远也不会产生碰撞冲突。 采用双通道运行,速度是DDR的2倍。 总的来说,DDR2采用了诸多的新技术,改善了DDR的诸多不足,虽然它目前有成本高、延迟慢能诸多不足,但相信随着技术的不断提高和完善,这些问题终将得到解决。

技术特点

DDR2引入了三项新的技术,它们是OCD、ODT和PostCAS。

OCD(Off-ChipDriver):也就是所谓的离线驱动调整。

ODT:ODT是内建核心的终结电阻器。

PostCAS:它是为了提高DDR2内存的利用效率而设定的。

DDR2和DDR3有什么区别

DDR2和DDR3的区别

DDR2和DDR3的插槽是不一样,DDR3比DDR2频率高,速度快,容量大,性能高。

DDR3内存相对于DDR2内存,其实只是规格上的提高,并没有真正的全面换代的新架构。DDR3接触针脚数目同DDR2皆为240pin。但是防呆的缺口位置不同。DDR3在大容量内存的支持较好,而大容量内存的分水岭是4GB这个容量,4GB是32位操作系统的执行上限(不考虑PAE等等的内存映像模式,因这些32位元元延伸模式只是过渡方式,会降低效能,不会在零售市场成为技术主流)当市场需求超过4GB的时候,64位CPU与操作系统就是唯一的解决方案,此时也就是DDR3内存的普及时期。

DDR2与DDR3内存的特性区别:

1、逻辑Bank数量

DDR2 SDRAM中有4Bank和8Bank的设计,目的就是为了应对未来大容量芯片的需求。而DDR3很可能将从2Gb容量起步,因此起始的逻辑Bank就是8个,另外还为未来的16个逻辑Bank做好了准备。

2、封装(Packages)

由于DDR3新增了一些功能,在引脚方面会有所增加,8bit芯片采用78球FBGA封装,16bit芯片采用96球FBGA封装,而DDR2则有60/68/84球FBGA封装三种规格。并且DDR3必须是绿色封装,不能含有任何有害物质。

3、突发长度(BL,Burst Length)

由于DDR3的预取为8bit,所以突发传输周期(BL,Burst Length)也固定为8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3为此增加了一个4-bit Burst Chop(突发突变)模式,即由一个BL=4的读取操作加上一个BL=4的写入操作来合成一个BL=8的数据突发传输,届时可通过A12地址线来控制这一突发模式。

4、寻址时序(Timing)

就像DDR2从DDR转变而来后延迟周期数增加一样,DDR3的CL周期也将比DDR2有所提高。DDR2的CL范围一般在2至5之间,而DDR3则在5至11之间,且附加延迟(AL)的设计也有所变化。DDR2时AL的范围是0至4,而DDR3时AL有三种选项,分别是0、CL-1和CL-2。另外,DDR3还新增加了一个时序参数——写入延迟(CWD),这一参数将根据具体的工作频率而定。

二、与DDR2相比DDR3具有的优点(桌上型unbuffered DIMM):

1.速度更快:prefetch buffer宽度从4bit提升到8bit,核心同频率下数据传输量将会是DDR2的两倍。

2.更省电:DDR3 Module电压从DDR2的1.8V降低到1.5V,同频率下比DDR2更省电,搭配SRT(Self-Refresh Temperature)功能,内部增加温度senser,可依温度动态控制更新率(RASR,Partial Array Self-Refresh功能),达到省电目的。

3.容量更大:更多的Bank数量,依照JEDEC标准,DDR2应可出到单位元元4Gb的容量(亦即单条模块可到8GB),但目前许多DRAM厂商的规划,DDR2生产可能会跳过这个4Gb单位元元容量,也就是说届时单条DDR2的DRAM模块,容量最大可能只会到4GB。而DDR3模块容量将从1GB起跳,目前规划单条模块到16GB也没问题(注意:这里指的是零售组装市场专用的unbuffered DIMM而言,server用的FB与Registered不在此限)。

DDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台...

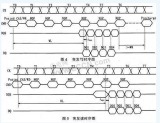

本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

在TMS320C6455/C6454上实现DDR2 PCB布局立即下载

类别:电子资料 2024-10-16 标签:pcbDDR2TMS320C6455

在TMS320DM335 DMSoC上实现DDR2/mDDR PCB布局立即下载

类别:电子资料 2024-10-15 标签:pcbDDR2tms320dm335

华邦自DDR2时期就深入物联网、汽车、工业、电信等高附加值领域,而随着制程升级至DDR3阶段,该公司开始加大对DDR3产能建设的投资力度。高雄工厂今年引...

致远微电子首款多媒体控制和图像显示应用高集成度芯片——ZMP110XP144C

ZMP110XP144C是广州致远微电子推出的首款多媒体控制和图像显示应用的高集成度芯片,采用ARM9内核架构,内部集成了DDR2 SDRAM存储器、图...

不少工程师发现,公司产品量产时突然采购告知所用SDRAM缺货或停产了,让工程师重新找一个替代的型号,轻则找一个PIN TO PIN兼容的就完事了,重则需...

FCI开发了一系列垂直内存插槽,可接受标准DDR2(双倍数据速率)内存模块组件,以便在台式机和服务器中实现内存扩展。 240位DDR2垂直连接器提供用于...

基于FPGA与DDR2 SDRAM器件HY5PS121621实现DDR2控制器的设计

DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最...

全球领先的测试、测量和监测仪器提供商--泰克公司日前宣布,推出完整的 DDR2 协议调试和验证解决方案,基于屡获奖项的 TLA6000 系列逻辑分析仪

DDR2,DDR2是什么意思 DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存...

2010-03-24 标签:DDR2 1462 0

IDT推出DDR3内存模块高精度温度传感器 新器件可提高企业、移动及嵌入式计算系统的可靠性、性能和电源效率 IDT公司(Integrated ...

厂商采取搭售策略 挽回DDR2销售颓势 全球DRAM市场正加速进行世代交替,DDR3芯片因缺货使得价格持续上涨,DDR2价格却严重下跌,且累积库存越...

2010-01-20 标签:DDR2 783 0

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |