完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > FPGA设计

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

fpga你可以理解成把一堆逻辑器件比如与门,或门,选择器等放在一个盒子里,盒子周围就是片子的引脚。通过逻辑编写,把许多的门和许多选择器等器件串联或并联引脚上。就等于把数电实验在fpga里面做。

arm的编程指的是c语言或者汇编的编程,arm一条条的读取语句,顺序实现其功能。

fpga的编程则完全不同。fpga编程本身指的就是编辑其内部的电路结构。fpga运行代码也不是一条条执行的,而是读入代码之后就生成了逻辑门结构。这些逻辑门结构是并行运作的。给输入就同时产生输出。所以fpga的编程语言叫做hdl(硬件描述语言)。hdl中的语句执行是不分先后的。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

开发

FPGA的开发相对于传统PC、单片机的开发有很大不同。FPGA以并行运算为主,以硬件描述语言来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别,也造成了FPGA开发入门较难。目前国内有专业的FPGA外协开发厂家,如[北京中科鼎桥ZKDQ-TECH]等。FPGA开发需要从顶层设计、模块分层、逻辑实现、软硬件调试等多方面着手。

FPGA怎么理解

fpga你可以理解成把一堆逻辑器件比如与门,或门,选择器等放在一个盒子里,盒子周围就是片子的引脚。通过逻辑编写,把许多的门和许多选择器等器件串联或并联引脚上。就等于把数电实验在fpga里面做。

arm的编程指的是c语言或者汇编的编程,arm一条条的读取语句,顺序实现其功能。

fpga的编程则完全不同。fpga编程本身指的就是编辑其内部的电路结构。fpga运行代码也不是一条条执行的,而是读入代码之后就生成了逻辑门结构。这些逻辑门结构是并行运作的。给输入就同时产生输出。所以fpga的编程语言叫做hdl(硬件描述语言)。hdl中的语句执行是不分先后的。

工程师谈:FPGA设计之硬件

做FPGA也有两年了,从刚开始的Verilog开始学起,到后来的最小系统,再到飓风II代开发板设计,到现在的XILINX XC2C系列CPLD开发,覆盖了硬件设计底层的一些经验。其实自己很想玩下FPGA的嵌入式,觉得很有前途的,但是后来自己也只是在学校开发板上过了下瘾。谈谈如何玩FPGA吧

要了解FPGA首先弄懂它的结构,FPGA是基于LUT结构,在器件选型的时候一般是参考它的逻辑单元的大小,然后是功耗和匹配电平的关系,IO口供电电平;内部PLL供电电平;所有的FPGA工作电压都是在3.3V,2.5V,1.2V三者之间选择,当然一定要弄清楚IO口是基于CMOS还是TTL工艺的,两者不能混淆。

选好器件后,接下来是原理图设计。在原理图设计中一般要注意去耦电容的容值大小,时钟电路,内部锁相环电路,下载电路。一般AS下载电路还要注意匹配的配置芯片的大小,在器件手册上都能查到,所以在设计前一定要通读对应的器件手册,一般的配置电路手册上都有参考,少走很多弯路。设计好原理图后一般要考虑下面IO口的接法:GCLK/GRST;这些复用的管脚一般不用作普通的IO口。而用作对应的第二功能。

原理图设计好后重点是PCB的设计,在设计前一定要反复检查原理图,是否有原理上的错误,一定注意电源电路的设计完整性。对于一般的TQFP封装的芯片要注意采用双面板我习惯把电源放在底层,滤波电容也通过过孔置于底层,在设计中当然是先布电源,时钟,最后布信号线了,其中的一些小的细节不用我啰嗦了,想必各位比我还厉害了。

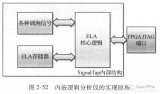

完成整个硬件电路板的设计后,接下来就是程序的设计了,这里面灵活性很大,在设计中一定要注意语法的严谨性,一个小小的“《=“都会带来无尽的麻烦,在完成程序设计后,一定要进行时序仿真,我一般是先把模块分块利用工具内部波形仿真来查看时序,接着采用SIGNAL TAP II进行内部逻辑分析,这个花了太多时间了,一个仿真就要几个小时。所以还是用TESTBENCH比较实际,注意是测试信号建立时间保持时间是否满足时序要求。

设计可靠的可编程逻辑门阵列(FPGA)对于不容故障的系统来说是一项具有挑战性的任务。本文介绍FPGA设计的复杂性,重点关注如何在提高可靠性的同时管理随之...

使用Altera Interface Planner高效设计FPGA引脚布局

Altera Interface Planner 用于探索设备的外设架构,并高效地分配接口。通过实时进行拟合和合法性检查,防止非法引脚分配。

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?

一般来说,复位信号有效后会保持比较长一段时间,确保 register 被复位完成。但是复位信号释放时,因为其和时钟是异步的关系,我们不知道它会在什么时刻被释放。

浅析FPGA的调试-内嵌逻辑分析仪(SignalTap)原理及实例

对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下进行仿真和调试,开发板类型EP4CE15F17。

高云EDA FPGA设计已通过ISO 26262和IEC 61508功能安全标准认证

GOWIN中密度和低密度FPGA的高安全性和高可靠性促使汽车OEM将其设计用于视频桥接、显示驱动和图像信号处理等应用中。

AMD Vivado Design Suite 2023.2的优势

由于市场环境日益复杂、产品竞争日趋激烈,为了加快推出新型自适应 SoC 和 FPGA 设计,硬件设计人员和系统架构师需要探索更为高效的全新工作方式。AM...

fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据?

fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据...

安全当前已成为各垂直市场所有设计的当务之急。今天,有进一步证据向系统架构师和设计人员证明,使用Microchip Technology Inc.(美国微...

业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设...

这是笔者去年某个时间节点的感悟,由于工作繁忙,写完后搁置一边了。而对于“设计最优化”这个议题,笔者也一直深感功力不够,不敢多做阐释。但是,不管怎样,...

虹科干货 | 如何测试与验证复杂的FPGA设计(3)——硬件测试

仿真和验证是开发任何高质量的基于FPGA的RTL编码过程的基础。在前文中,我们介绍了面向实体/块的仿真,并介绍了如何在虹科的IP核中执行面向全局的仿真。...

2022-06-18 标签:FPGA设计 1478 0

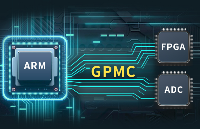

为何TI的GPMC并口,更常被用于连接FPGA、ADC?我给出3个理由

1GPMC并口简介GPMC(GeneralPurposeMemoryController)是TI处理器特有的通用存储器控制器接口,是AM335x、AM4...

热分析的最终目标是要使得整个系统能够稳定地运行,特别是保证芯片的结温不能超过安全阈值。如果无法保证这一点,那么FPGA芯片在性能指标、可靠性、使用寿命等...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |