完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > D触发器

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种。

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种。

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态取决于CP的脉冲上升沿到来之前D端的状态,即次态=D。因此,它具有置0、置1两种功能。由于在

CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

1. 结构

D触发器(data flip-flop或delay flip-flop)由6个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

2. 工作原理

SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:

1)CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5非=D非。

2)当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D非,Q4=Q6非=D。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

3)触发器翻转后,在CP=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的

状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在1状态和阻止触发器变为0状态的作用,故该反馈线称为置1维持线,置0阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出端至G6反馈线起到使触发器维持在0状态的作用,称作置0维持线;Q4输出至G3输入的反馈线起到阻止触发器置1的作用,称为置1阻塞线。因此,该触发器常称为维持-阻塞触发器。总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。 /span》。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

D触发器逻辑图和逻辑符号

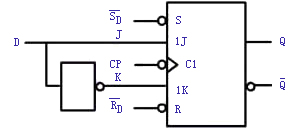

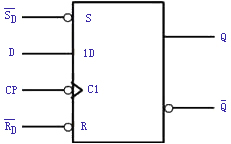

可以将JK触发器转换为D触发器,其逻辑图和逻辑符号如图1(a)和(b)所示。当D=1,即![]() ,

,![]() 时,在CP的下降沿触发器翻转为(或保持)1态;当

时,在CP的下降沿触发器翻转为(或保持)1态;当![]() ,即

,即![]() ,

,![]() 时,在CP的下降沿触发器翻转为(或保持)0态。

时,在CP的下降沿触发器翻转为(或保持)0态。

(a)逻辑图(b)逻辑符号

图1D触发器

由以上可知,某个时钟脉冲来到之后输出端Q的状态和该脉冲来到之前输入端D的状态一致,即

![]()

D触发器的逻辑状态表见表1。

表1 D触发器的逻辑状态表

D![]()

![]() 功能

功能

00![]() 置0

置0

1

10![]() 置1

置1

1

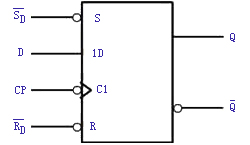

国内生产的D触发器主要是维持阻塞型(不在本书中讨论),如双上升沿D触发器74LS74、四上升沿D触发器74LS175等,它们在时钟脉冲的上升沿触发,逻辑符号如图2所示,在CP输入端不加小圆圈。

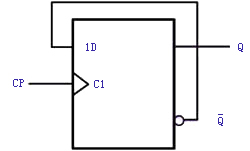

图2上升沿D触发器的逻辑符号图3 D触发器转换为T触发器

也可将D触发器转换为T触发器,如图3所示。它的逻辑功能是每来一个时钟脉冲,翻转一次,即![]() ,具有记数功能。

,具有记数功能。

74ls74双d触发器引脚图 74ls74双D触发器功能测试

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入( )、时钟输入(CP)和数据输出(Q)。 的低电平使输...

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。现代的数字电路由半导...

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |