完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > FPGA设计

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

fpga你可以理解成把一堆逻辑器件比如与门,或门,选择器等放在一个盒子里,盒子周围就是片子的引脚。通过逻辑编写,把许多的门和许多选择器等器件串联或并联引脚上。就等于把数电实验在fpga里面做。

arm的编程指的是c语言或者汇编的编程,arm一条条的读取语句,顺序实现其功能。

fpga的编程则完全不同。fpga编程本身指的就是编辑其内部的电路结构。fpga运行代码也不是一条条执行的,而是读入代码之后就生成了逻辑门结构。这些逻辑门结构是并行运作的。给输入就同时产生输出。所以fpga的编程语言叫做hdl(硬件描述语言)。hdl中的语句执行是不分先后的。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

开发

FPGA的开发相对于传统PC、单片机的开发有很大不同。FPGA以并行运算为主,以硬件描述语言来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别,也造成了FPGA开发入门较难。目前国内有专业的FPGA外协开发厂家,如[北京中科鼎桥ZKDQ-TECH]等。FPGA开发需要从顶层设计、模块分层、逻辑实现、软硬件调试等多方面着手。

FPGA怎么理解

fpga你可以理解成把一堆逻辑器件比如与门,或门,选择器等放在一个盒子里,盒子周围就是片子的引脚。通过逻辑编写,把许多的门和许多选择器等器件串联或并联引脚上。就等于把数电实验在fpga里面做。

arm的编程指的是c语言或者汇编的编程,arm一条条的读取语句,顺序实现其功能。

fpga的编程则完全不同。fpga编程本身指的就是编辑其内部的电路结构。fpga运行代码也不是一条条执行的,而是读入代码之后就生成了逻辑门结构。这些逻辑门结构是并行运作的。给输入就同时产生输出。所以fpga的编程语言叫做hdl(硬件描述语言)。hdl中的语句执行是不分先后的。

工程师谈:FPGA设计之硬件

做FPGA也有两年了,从刚开始的Verilog开始学起,到后来的最小系统,再到飓风II代开发板设计,到现在的XILINX XC2C系列CPLD开发,覆盖了硬件设计底层的一些经验。其实自己很想玩下FPGA的嵌入式,觉得很有前途的,但是后来自己也只是在学校开发板上过了下瘾。谈谈如何玩FPGA吧

要了解FPGA首先弄懂它的结构,FPGA是基于LUT结构,在器件选型的时候一般是参考它的逻辑单元的大小,然后是功耗和匹配电平的关系,IO口供电电平;内部PLL供电电平;所有的FPGA工作电压都是在3.3V,2.5V,1.2V三者之间选择,当然一定要弄清楚IO口是基于CMOS还是TTL工艺的,两者不能混淆。

选好器件后,接下来是原理图设计。在原理图设计中一般要注意去耦电容的容值大小,时钟电路,内部锁相环电路,下载电路。一般AS下载电路还要注意匹配的配置芯片的大小,在器件手册上都能查到,所以在设计前一定要通读对应的器件手册,一般的配置电路手册上都有参考,少走很多弯路。设计好原理图后一般要考虑下面IO口的接法:GCLK/GRST;这些复用的管脚一般不用作普通的IO口。而用作对应的第二功能。

原理图设计好后重点是PCB的设计,在设计前一定要反复检查原理图,是否有原理上的错误,一定注意电源电路的设计完整性。对于一般的TQFP封装的芯片要注意采用双面板我习惯把电源放在底层,滤波电容也通过过孔置于底层,在设计中当然是先布电源,时钟,最后布信号线了,其中的一些小的细节不用我啰嗦了,想必各位比我还厉害了。

完成整个硬件电路板的设计后,接下来就是程序的设计了,这里面灵活性很大,在设计中一定要注意语法的严谨性,一个小小的“《=“都会带来无尽的麻烦,在完成程序设计后,一定要进行时序仿真,我一般是先把模块分块利用工具内部波形仿真来查看时序,接着采用SIGNAL TAP II进行内部逻辑分析,这个花了太多时间了,一个仿真就要几个小时。所以还是用TESTBENCH比较实际,注意是测试信号建立时间保持时间是否满足时序要求。

以Xilinx公司最新的Vivado FPGA集成开发环境为基础,将数字逻辑设计与硬件描述语言Verilog HDL相结合,循序渐进地介绍了基于Xili...

FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。 早期的FPGA相对比较简单,所有的功能...

流水线设计可以从某种程度上提高系统频率。。前提是:设计可以分为若干步骤进行处理,而且整个数据处理的过程是单向的,即没有反馈或者逆运算、前一个步骤的输出是...

作者:张泽小脚丫STEP 导读:FPGA(Field Programmable Gate Array)译作中文为:现场可编程门阵列,也就是设计者可以在现...

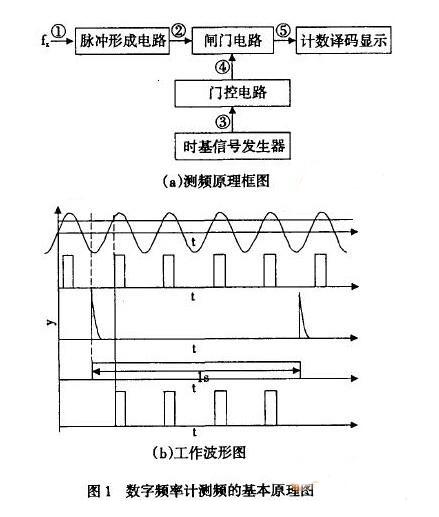

在电子工程,资源勘探,仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。频率测量也是电子测量技术中最基本最常见的测量之一。不少物理量的测量,...

2019-01-01 标签:FPGA设计 6608 0

1、硬件设计基本原则 (1)速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的...

FPGA因为具备接口,控制,功能IP,内嵌CPU等特点有条件实现一个构造简单,固化程度高,功能全面的系统产品设计将是FPGA技术应用最广大的市场,具有极...

全硬件TCP/IP协议栈学习笔记 (第八天:W5500+FPGA实现tcp连接)

经历了一个多月的调试,最终终于使用basys2将tcp模式配置成功了。 首先说一下思路吧,首先W5500的发送与接收与开发板的通信使用的是SPI协议,下...

全硬件TCP/IP协议栈学习笔记(第七天:FPGA+W5500 PING通)

在一周多的时间,从软件的协议到芯片接口最后到硬件描述,我觉得是时候试一试芯片了,看一看能不能ping通。两天时间终于完成第一次ping,也挺不容易的。 ...

把相对成熟的技术应用到某些特定领域如通讯,视频,信息处理等等开发出满足行业需要并能被行业客户接受的产品这方面主要是FPGA技术和专业技术的结合问题,另外...

本文从硬件加速的视角考察深度学习与FPGA,指出有哪些趋势和创新使得这些技术相互匹配,并激发对FPGA如何帮助深度学习领域发展的探讨。

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |