完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > MPU

MPU有两种意思,微处理器和内存保护单元。MPU是单一的一颗芯片,而芯片组则由一组芯片所构成,早期甚至多达7、8颗,但目前大多合并成2颗,一般称作北桥(North Bridge)芯片和南桥(South Bridge)芯片。

MPU有两种意思,微处理器和内存保护单元。MPU是单一的一颗芯片,而芯片组则由一组芯片所构成,早期甚至多达7、8颗,但目前大多合并成2颗,一般称作北桥(North Bridge)芯片和南桥(South Bridge)芯片。MPU是计算机的计算、判断或控制中心,有人称它为”计算机的心脏”。

MPU[1] (Microprocessor Unit)微处理器微机中的中央处理器(CPU)称为微处理器(MPU),是构成微机的核心部件,也可以说是微机的心脏。它起到控制整个微型计算机工作的作用,产生控制信号对相应的部件进行控制,并执行相应的操作。在微机中,CPU被集成在一片超大规模集成电路芯片上,称为微处理器(MPU),微处理器插在主板的cpu插槽中。通常所说的16位机、32位机是指该计算机中微处理器内部数据总线的宽度,也就是CPU可同时操作的二进制数的位数。目前常用的CPU都是64位的,即一次可传送64位二进制数。

MPU有两种意思,微处理器和内存保护单元。MPU是单一的一颗芯片,而芯片组则由一组芯片所构成,早期甚至多达7、8颗,但目前大多合并成2颗,一般称作北桥(North Bridge)芯片和南桥(South Bridge)芯片。MPU是计算机的计算、判断或控制中心,有人称它为”计算机的心脏”。

MPU[1] (Microprocessor Unit)微处理器微机中的中央处理器(CPU)称为微处理器(MPU),是构成微机的核心部件,也可以说是微机的心脏。它起到控制整个微型计算机工作的作用,产生控制信号对相应的部件进行控制,并执行相应的操作。在微机中,CPU被集成在一片超大规模集成电路芯片上,称为微处理器(MPU),微处理器插在主板的cpu插槽中。通常所说的16位机、32位机是指该计算机中微处理器内部数据总线的宽度,也就是CPU可同时操作的二进制数的位数。目前常用的CPU都是64位的,即一次可传送64位二进制数。

功能构成

微处理器的功能结构主要包括:运算器、控制器、寄存器三部分:运算器的主要功能就是进行算术运算和逻辑运算。控制器是整个微机系统的指挥中心,其主要作用是控制程序的执行。包括对指令进行译码、寄存,并按指令要求完成所规定的操作,即指令控制、时序控制和操作控制。寄存器用来存放操作数、中间数据及结果数据。

主要技术参数

CPU质量的高低直接决定了一个计算机系统的档次,而CPU的主要技术特性可以反映出CPU的基本性能。CPU的主要技术参数如下:⑴ CPU可以同时处理的二进制数据的位数,即字长;⑵ 时钟频率;⑶ 高速缓冲存储器(Cache)的容量和速率;⑷ 地址总线和数据总线的宽度;⑸ 制造工艺。

内存保护

内存保护单元(ARM体系方面)(MPU,Memory Protection Unit),MPU中一个域就是一些属性值及其对应的一片内存。这些属性包括:起始地址、长度、读写权限以及缓存等。ARM940具有不同的域来控制指令内存和数据内存。内核可以定义8对区域,分别控制8个指令和数据内存区域。域和域可以重叠并且可以设置不同的优先级。域的启始地址必须是其大小的整数倍。另外,域的大小可以4K到4G间任意一个2的指数,如4K,8K,16K.。。。。英汉计算机词汇= Main Processing Unit,主处理机; = Memory Protection Unit, 存储器保护设备; = MicroProcessing Unit, 微处理器[机]; = MicroProgrammed control Unit, 微程序控制器; = MicroProgramming Unit, 微程序设计部件; = Miniature Power Unit, 小型电源设备

MCU和MPU有什么区别

MPU有两种意思,微处理器和内存保护单元。MPU是单一的一颗芯片,而芯片组则由一组芯片所构成,早期甚至多达7、8颗,但目前大多合并成2颗,一般称作北桥(North Bridge)芯片和南桥(South Bridge)芯片。MPU是计算机的计算、判断或控制中心,有人称它为”计算机的心脏”。

中央处理器(CPU,英语:Central Processing Unit),是电子计算机的主要设备之一,电脑中的核心配件。其功能主要是解释计算机指令以及处理计算机软件中的数据。电脑中所有操作都由CPU负责读取指令,对指令译码并执行指令的核心部件。

ARM存储器之:存储保护单元MPU

存储保护单元MPU

一些嵌入式系统使用多任务的操作和控制。这些系统必须提供一种机制来保证正在运行的任务不破坏其他任务的操作。即要防止系统资源和其他一些任务不受非法访问。要达到这一目的通常有软件保护和硬件保护两种途径。这里软件保护是指仅靠软件来保护系统资源。系统中无保护硬件或硬件没启动。在多任务的系统中,通常要运行操作系统来达到任务间同步与通信。所以,这种软件的资源保护通常由操作系统来完成。但这种通过软件来协调任务运行,保护系统资源的做法有时会出现一些不可避免的问题。如当对一个通信用串口寄存器进行操作时,如果一个任务正在使用串口,则它没有办法来防止其他任务使用同一个串口。因此,若要成功使用该串口,则必须通过一个访问该串口的系统调用来协调。使用这些调用任务的非授权访问,很容易破坏经过该串口的通信。因此资源的不合理使用也许是不可避免的。

相反,受保护系统有专门的硬件来检测和限制系统资源的访问。它能保证资源的所有权,任务需要遵守一组由操作环境定义的、由硬件维护的规则,在硬件级上授予监视和控制资源程序的特殊权限。受保护系统主动防止一个任务使用其他任务的资源。因此使用硬件主动监视系统比协调加强的软件历程,提供了更好的保护。

ARM中配备的有效保护系统资源的硬件,有两种:

· MPU(Memory Protection Unit);

· MMU(Memory Management Unit)。

MMU是比MPU提供了功能更强大的内存保护机制,MPU只提供了内存区域保护,而MMU是在此基础上提供了虚拟地址映射技术,而且在操作上,MMU要比MPU负责。本节主要讨论带MPU的处理器内核,MMU将在下一节详细介绍。

15.4.1 保护域(Protection Regions)

ARM处理器中的MPU使用“域(regions)”来对内存单元进行管理。域是与存储空间相关联的属性,处理器核将这些数据保存在协处理器CP15的一些寄存器中。通常域的个数为8个,编号为从0~7。

域的大小和起始地址保存在CP15的寄存器c6中。大小可以是4KB~4GB的任何2的乘幂。域的起始地址必须是其大小的倍数。比如,一个定义为4KB的域其起始地址可以是0x12345000,而一个大小定义为8KB的域起始地址只能是0x2000的倍数。

另外,操作系统可以为这些域分配更多的属性:访问权限、cache和写缓存。存储器基于当时的处理器模式(管理模式或用户模式)可以设定这些区域的访问权限为读/写、只读和不可访问。

当处理器访问主存的一个域时,MPU比较该域的访问权限属性和当时的处理器模式。如果请求符合域的访问标准,则MPU允许内核读/写主存;如果存储器请求不符号域的访问标准,将产生一个异常信号。

异常信号被送到处理器核。处理器核执行一个异常向量,然后跳转到异常处理程序,异常处理程序判断异常类型为预取指或数据中止,然后根据异常类型,跳转到相应的服务例程。

对于ARM处理器,存储空间的某一部分可以被分配给一个以上的区域。也就是说域可以重叠。在重叠的域内,可以设置域的优先级。在分配访问权限时重叠域比非重叠域有更大的灵活性。后面一节将会详细介绍域的重叠。

内存访问顺序

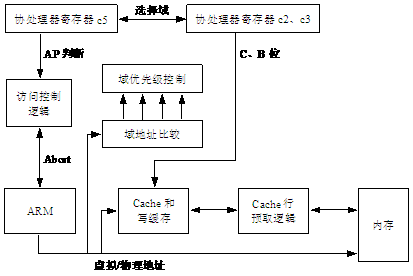

当ARM处理器产生一个内存访问信号时,内存保护单位MPU将负责检查要访问的地址是否在被定义的域中。

① 如果地址不在任何域中,存储器产生异常。如果内核预取指令则MPU产生预取中止异常;如果是存储器数据请求,则产生数据中止异常。

② 如果地址在多个域内,由MPU判断域的有效级来决定存储区域的访问属性。访问属性可以在CP15的寄存器中设定,可设定的位为C(Cache)、B(Buffer)、AP(Access Permission)。这些属性的具体定义为:

· C和B可以控制Cache和写缓存属性的Cache策略。例如,可以设置一个域使用回写(write-back)策略访问存储器,而另一个域则以无Cache和无写缓存方式访问;

· AP(access permission)决定域是否可以被访问。如果在当前处理器模式下,该域不能被访问,MPU将产生一个存储器访问异常。

图15.16显示了一个存储器访问过程。

图15.16 存储器访问过程

15.4.3 使能MPU

通过对协处理器CP15的寄存器c1中的bit[0]置1,可以使能存储器保护单元MPU。在系统上电时,默认状态是该位清零,所有保护域无效。

在使能MPU之前,至少一个域要被设定,而且该域的属性和访问权限要预先设定好。

![]() 注意在数据和指令域分离的系统中,如ARM940T,在指令和数据域中都要有一个有效域被预先设定好。

注意在数据和指令域分离的系统中,如ARM940T,在指令和数据域中都要有一个有效域被预先设定好。

另外,使能MPU的指令要设在有效的域中。如果在使能MPU之前,域的属性和访问权限没有设定,那么系统的运行结果将不可预知。

当MPU无效(将协处理器CP15寄存器r1的bit[0]置0)时,整个内存区域都被处理器视为无Cache、无写缓存、无存储保护状态。

15.4.4 重叠域

域的定义在MPU的作用下可以重叠。当重叠的域被访问时,MPU会判断域的优先权,决定使用那个域的属性来操作重叠域。

域属性优先级的排列顺序为:域7的有效级最高,其次为域6,域0的优先级最低。

【例15.3】

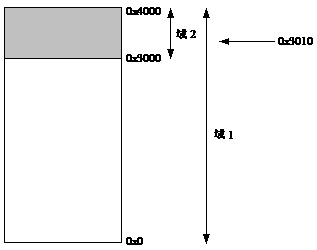

假设将一个从0x3000起始的4KB地址空间定义为域2,其访问属性AP定义为0b10(AP=0b10,特权模式读/写访问,用户模式只读)。

将起始地址为0x0的16KB地址空间定义为域1,其访问属性AP定义为0b01(AP=0b01,特权模式只读)。

系统域划分如图15.17所示。

图15.17 重叠域的访问

当处理器在用户模式下执行Load指令,从0x3010地址取数据时,0x3010地址既在域1中也在域2中,因为域2的属性优先级高于域1,所有MPU执行域2的访问属性从0x3010地址取数据。域2是用户模式可读,所以不会发生数据异常。

在分配访问权限时重叠区域比非重叠区域有更大的灵活性,它可以使内存的某个特定联系内存单位在程序中担任背景的作用,用来给一块大存储空间分配相同的属性的低优先级域。其他具有较高优先级域的区域与该背景域某些部分重叠,用来改变已定义的背景域的较小子集的属性。这样,具有较高优先级的域可以改变背景域属性的子集。背景域可以用来保护一些睡眠状态的存储空间,使其不受非法访问,而此时由另一个不同域控制下的背景域的其他部分可以处于活跃状态。

15.4.5 与MPU相关的CP15寄存器

与MPU相关的协处理器寄存器主要是c2,c3,c5及c6。另外还有寄存器c1中的1到2位。

(1)c1中的MPU相关位

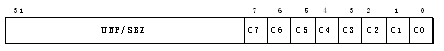

c1的编码格式如图15.18所示。

![]()

图15.18 协处理器寄存器c1编码格式

M(bit[0])控制控制MPU的使能。

· M=0:禁止MPU

· M=1:使能MPU

A(bit[1])选择是否支持内存访问地址对齐检查。

· B=0:禁止地址对齐检查

· B=1:使能地址对齐检查

(2)c2中的MPU相关位

c2的编码格式如图15.19所示。

图15.19 协处理器寄存器c2编码格式

寄存器位0~7分别对应域0~7的Cache属性。位8~31应该设置成0。

![]() 注意在数据和指令分离的系统中,通过MRC和MCR指令的第二个操作数《opcode2》来决定读写D-Cache和I-Cache属性。

注意在数据和指令分离的系统中,通过MRC和MCR指令的第二个操作数《opcode2》来决定读写D-Cache和I-Cache属性。

(3)c3中的MPU相关位

c3的编码格式如图15.20所示。

图15.20 协处理器寄存器c3编码格式

寄存器位0~7分别对应域0~7的写缓存属性。位8~31应该设置成0。

当用指令MCR/MRC对c3进行读写时,第二个操作数《opcode2》将被忽略,在指令要设置成0。

当配置数据域时,域的Cache位和写缓存区位一起决定域的访问策略。写缓存位有两个用途:使能/禁止域的写缓存和设置域的Cache写策略。域的Cache位控制写缓存位的作用。具体位分配见表15.16。

表15.16 Cache位和写缓存位的分配策略

Cache位写缓存区位域 属 性

C=0B=0禁止Cache、禁止写缓存

C=0B=1禁止Cache、使能写缓存

C=1B=0使能Cache,域使用回写策略

C=10B=1使能Cache,域使用直写策略

(4)访问权限寄存器c5

协处理器CP15的寄存器c5设置内存域的访问权限。

寄存器c5的编码格式如图15.21所示。

![]()

图15.21 寄存器c5的编码格式

读寄存器c3的bits[15:0]存放域的AP(access permission,访问权限),其中bits[2n+1:2n]对于域n的访问权限。AP编码与访问权限的对应关系如表15.17所示。

表15.17 AP编码与访问权限的对应关系

AP编码管 理 者用 户

00不可访问不可访问

01读/写不可访问

10读/写只读

11读/写读/写

对于Arm940T、Arm940T两个内核版本来说,使用MRC和MCR指令对其进行读写时,第二个协处理器寄存器《CRm》将被忽略,指令中以c0的形式出现。对于指令数据统一的域,第二操作数《opcode2》要设成0,而对于数据和指令分离的系统,如果opcode2=0,说明操作对数据域有效,如果opcode=1,说明操作对指令域有效。

![]() 注意对于Arm946E-S和Arm1026EJ-S两个内核版本,它们的访问权限机制更复杂,采用的是扩展AP,扩展组AP位域编码支持两个增强的权限域,对其进行操作的MRC和MCR指令形式更复杂,有关更详细的内容,请参加Arm公司的用户手册。

注意对于Arm946E-S和Arm1026EJ-S两个内核版本,它们的访问权限机制更复杂,采用的是扩展AP,扩展组AP位域编码支持两个增强的权限域,对其进行操作的MRC和MCR指令形式更复杂,有关更详细的内容,请参加Arm公司的用户手册。

(5)域大小控制寄存器c6

Arm系统中通过写协处理器c6来定义域的大小,通过MCR指令中第二个操作寄存器赋不同的值来指示是对哪个具体域进行操作。第二个操作寄存器取值为c0~c7,分别对应域0~域7。

每个域的起始地址必须对齐到其大小的整数倍。比如,一个域的大小位64KB,其起始地址可以是0x10000的整数倍的任何数。域的大小可以是4KB~4GB的2的任意乘幂。

寄存器c6的编码格式如图15.22所示。

图15.22 域大小控制寄存器c6编码格式

编码含义如表15.18所示

表15.18 寄存器c6编码含义

位 名 称对 应 位注 释

起始地址[31:12]保护域的第一个字节起始地址,具体见表2.18

SBZ[11:6]必须设为0

Size[5:1]设Size=N,则域尺寸为2N+1,其中11≤N≤31

E[0]域使能,E=1使能,E=0禁止

关于c6中bits[31:12],因为域的起始要是域大小的整倍数,域最小为4KB,所有域起始地址的bits[11:0]通常为0,不用设置。具体c6中起始地址的设置和c6中Size(bits[5:1])的对应关系如表15.19所示。

表15.19 域尺寸编码

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b00000~0b01010未定义-

0b010114KB无

0b011008KBbit[12]必须为0

0b0110116KBbits[13:12]必须为0

0b0111032KBbits[14:12]必须为0

0b0111164KBbits[15:12]必须为0

0b10000126KBbits[16:12]必须为0

0b10001256KBbits[17:12]必须为0

0b10010512KBbits[18:12]必须为0

0b100111MBbits[19:12]必须为0

0b101002MBbits[20:12]必须为0

0b101014MBbits[21:12]必须为0

0b101108MBbits[22:12]必须为0

0b1011116MBbits[23:12]必须为0

0b1100032MBbits[24:12]必须为0

0b1100164MBbits[25:12]必须为0

0b11010128MBbits[26:12]必须为0

0b11011256MBbits[27:12]必须为0

0b11100512MBbits[28:12]必须为0

0b111011GBbits[29:12]必须为0

续表

Size(bits[5:1])域 尺 寸起始地址(bits[31:12])

0b111102GBbits[30:12]必须为0

0b111114GBbits[31:12]必须为0

本文介绍了STM32MP157C主要特性,框图,电源方案图以及评估板STM32MP157C-EV1和STM32MP157A-EV1主要特性,硬件框图和电...

最佳处理解决方案常常是由 RISC、CISC、图形处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提...

CPU(Central Processing Unit),是一台计算机的运算核心和控制核心。CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制...

MPU是什么Cortex-M内核的MPU内存保护单元详细讲解

估计大家经常看见MCU、MPU、MMU等这类缩写词,你们了解MPU吗?

广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EE...

当为你的下一个设计方案选择正确的核心处理器件时,你应该考虑哪些因素呢?本文将对MPU和MCU做些对比分析,并以此对器件的选择给出一些指导性建议和意见。每...

MPU(Memory Protection Unit)是一种硬件保护机制,用于保护嵌入式系统中的内存安全。它是嵌入式处理器中的一种特殊模块,通常与CPU...

M1052跨界核心板普通MCU系统般简便,却拥有“不凡”性能

M1052跨界核心板板载Cortex-M7的RT1050处理器,既具备MPU的强劲处理性能,又兼顾MCU微控制器的简单易用与实时性优势!M1052集成W...

所谓零开销循环是指处理器在执行循环时,不用花时间去检查循环计数器的值、条件转移到循环的顶部、将循环计数器减1。与此相反,GPP的循环使用软件来实现:某些...

现在的问题是,MCU开始不本分了(MPU或许也有了新想法)。随着边缘人工智能应用(如语言控制设备)的兴起,过去相对较笨的MCU显得有些力不从心。但是,M...

意法半导体STM32MP157A MPU加持,米尔科技首款ST Linux开发板MYD-YA157C评测

ST公司去年推出了MPU系列芯片,MPU系列不同于以往产品,它既包含有ARM公司Cortex M 单片机核心,也包含有ARM公司Cortex A 应用处...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |