完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > RTL

RTL在电子科学中指的是寄存器转换级电路(Register Transfer Level)的缩写,也叫暂存器转移层次。

在集成电路设计中, register-transfer level(RTL)是用于描述同步数字电路操作的抽象级。

在RTL级,IC是由一组寄存器以及寄存器之间的逻辑操作构成。之所以如此,是因为绝大多数的电路可以被看成由寄存器来存储二进制数据、由寄存器之间的逻辑操作来完成数据的处理,数据处理的流程由时序状态机来控制,这些处理和控制可以用硬件描述语言来描述。

RTL级和门级简单的区别在于,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,门级则是用具体的逻辑单元(依赖厂家的库)来实现你的功能,门级最终可以在半导体厂加工成实际的硬件,一句话,RTL和门级是设计实现上的不同阶段,RTL经过逻辑综合后,就得到门级。

RTL描述是可以表示为一个有限状态机,或是一个可以在一个预定的时钟周期边界上进行寄存器传输的更一般的时序状态机,通常VHDL/verilog两种语言进行描述。

RTL在电子科学中指的是寄存器转换级电路(Register Transfer Level)的缩写,也叫暂存器转移层次。

寄存器传输级

在集成电路设计中, register-transfer level(RTL)是用于描述同步数字电路操作的抽象级。

在RTL级,IC是由一组寄存器以及寄存器之间的逻辑操作构成。之所以如此,是因为绝大多数的电路可以被看成由寄存器来存储二进制数据、由寄存器之间的逻辑操作来完成数据的处理,数据处理的流程由时序状态机来控制,这些处理和控制可以用硬件描述语言来描述。

RTL级和门级简单的区别在于,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,门级则是用具体的逻辑单元(依赖厂家的库)来实现你的功能,门级最终可以在半导体厂加工成实际的硬件,一句话,RTL和门级是设计实现上的不同阶段,RTL经过逻辑综合后,就得到门级。

RTL描述是可以表示为一个有限状态机,或是一个可以在一个预定的时钟周期边界上进行寄存器传输的更一般的时序状态机,通常VHDL/verilog两种语言进行描述。

RTL电路是最早研制成功的一种有实用价值的集成电路。有N 个门的输入端并接在DCTL电路输出端,因为DCTL电路输出端门的晶体管基极导通电压,电流曲线并不能完全一致,并联在一起,输入电流易出现分配不均匀的现象。输入电流小的负载门可能得不到足够的基极驱动电流,达不到饱和,从而输出端可能从应有的“0”态改变到“1”状态,使系统出现差错。负载输入端并接越多,产生电流分配不匀的可能性越大。这种现象叫作“抢电流”。RTL电路是每一输入级基极串接一个电阻,旨在得到改善和补偿,使基极输入电流 Ib对基极-发射极V公式 符号-Ib特性的依赖性小一些。根据 Rb的阻值即可确定RTL电路的最大负载门数。

RTL电路结构简单,元件少。RTL电路的严重缺点是基极回路有电阻存在,从而限制了电路的开关速度,抗干扰性能也差,使用时负载又不能过多。RTL电路是一种饱和型电路,只适用于低速线路,实际上已被淘汰。为了改善RTL逻辑电路的开关速度,在基极电阻上再并接一个电容,就构成了电阻-电容-晶体管逻辑电路(RCTL)。有了电容,不仅可以加快开关速度,而且还可以加大基极电阻,从而减小电路功耗。但是,大数值电阻和电容在集成电路制造工艺上要占去较大的芯片面积,而且取得同样容差值的设计也比较困难。因此,RCTL电路实际上也没有得到发展。

行为级和RTL级的区别

RTL级,registertransferlevel,指的是用寄存器这一级别的描述方式来描述电路的数据流方式;而Behavior级指的是仅仅描述电路的功能而可以采用任何verilog语法的描述方式。鉴于这个区别,RTL级描述的目标就是可综合,而行为级描述的目标就是实现特定的功能而没有可综合(可实现)的限制。

行为级是RTL的上一层,行为级是最符合人类逻辑思维方式的描述角度,一般基于算法,用C/C++来描述。从行为级到RTL级的转换,一般都是由IC设计人员手工翻译。

这个过程繁琐,工作量很大,特别是随着数字系统的复杂性提升,这样的纯手工“翻译”过程容易出错,且使得开发周期变长。一批高级综合工具应运而生。如Menter Graphics的高层次综合工具Catapult C Synthesis。能够将数字系统的行为级描述映射为RTL设计,并满足给定的目标限制。从层次由上到下,数字系统的设计过程为:

Idea-》行为级描述-》rtl描述-》门级网标-》物理版图

行为级的描述更多的是采取直接赋值的形式,只能看出结果,看不出数据流的实际处理过程。其中又大量采用算术运算,延迟等一些无法综合的语句。常常只用于验证仿真。

RTL级的描述就会更详细一些,并且从寄存器的角度,把数据的处理过程表达出来。可以容易地被综合工具综合成电路的形式。

行为级描述可是说是RTL的上层描述,比RTL更抽象。行为描述不关心电路的具体结构,只关注算法。

有行为综合工具,可以直接将行为级的描述综合为RTL级的,比如Behavioral Compiler。

在硬件设计中有一句著名的话:thinking of hardware。RTL在很大程度上是对流水线原理图的描述。哪里是组合逻辑,哪里是寄存器,设计者应该了然于胸。组合逻辑到底如何实现,取决于综合器和限制条件。

rtl级可以理解为,可以直接给综合工具生成你要的网表的代码,而行为级则不行。比如real(浮点实数?)可以用于行为级,而不能用于rtl级!

Behavior is for testbench for modelling.

RTL is for synthesis

语法块如果可以被综合到gate level,就是RTL的。否则就是behavior level的。

同样是for语句,如果循环条件是常数,就是RTL的,如果是变量,就是behavior的。

RTL级描述数据在寄存器层次的流动模型。

always属于行为级模型,是最基本的行为模型,是可以综合的。

综合与RTL或者行为级没有必然联系,虽然大多数行为模型不能综合

从网上copy

目的区别:

行为级描述目的是加快仿真速度,做法是尽量减少一个always块中要执行的语句数量,其结果不是为了综合,只关注算法。有行为综合工具,可以直接将行为级的描述综合为RTL级的,比如Behavioral Compiler。

形式区别:

RTL级描述是为了综合工具能够正确的识别而编写的代码,verilog中有一个可综合的子集,不同的综合工具支持的也有所不同,RTL级的描述就会更详细一些,并且从寄存器的角度,把数据的处理过程表达出来。可以容易地被综合工具综合成电路的形式。可以采用任何verilog语法的描述方式。鉴于这个区别,RTL级描述的目标就是可综合,

行为级的描述更多的是采取直接赋值的形式,只能看出结果,看不出数据流的实际处理过程。其中又大量采用算术运算,延迟等一些无法综合的语句。常常只用于验证仿真。

电路区别:

RTL级,register transfer level,指的是用寄存器这一级别的描述方式来描述电路的数据流方式;RTL在很大程度上是对流水线原理图的描述。哪里是组合逻辑,哪里是寄存器,设计者应该了然于胸。组合逻辑到底如何实现,取决于综合器和限制条件。RTL是晶体管传输级,描述硬件的相互联接关系,一般都可以综合;

而Behavior级指的是仅仅描述电路的功能而在硬件设计中有一句著名的话:thinking of hardware。简单说,rtl就是用寄存器和组合逻辑组成,不能再用其他construct;behavior就是指定输入和输出之间的关系。

混乱点:有时感觉RTL级是行为级与数据流级的混合应用。

乐点:同样是for语句,如果循环条件是常数,就是RTL的,如果是变量,就是behavior的。

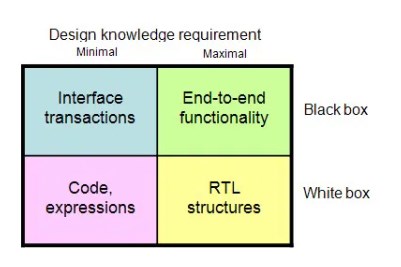

如何将SystemVerilog断言属性和覆盖属性置于在设计上?

功能覆盖、激励生成和运行管理是当今功能验证的三大相互关联的任务。其中,功能覆盖率可以说是最重要的,主要是因为覆盖率收敛是tape的主要标准。

在Windows 10上创建并运行AMD Vitis™视觉库示例

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。如果您使...

在数字设计的Implementation过程中,从RTL到GDSII的每一步都是高度计算密集型的。

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体...

AMD Versal AI Edge自适应计算加速平台之PL LED实验(3)

对于Versal来说PL(FPGA)开发是至关重要的,这也是Versal比其他ARM的有优势的地方,可以定制化很多ARM端的外设

Cadence Verisium Debug:统一调试平台,加速SoC设计

Cadence的统一调试平台Verisium Debug,为从IP到SoC级别的复杂设计提供了全面的调试解决方案。该平台集成了多种调试功能,包括RTL调...

当CPU算力趋近极限,GPU能否替代CPU满足数字芯片设计的算力需求?

就数字设计实现而言,RTL-to-GDSII流程中的每一步都涉及海量计算。在SoC级别,开发者需要评估数百个分区的各种版图规划选项,从而更大限度减少互连...

上海科学技术委员会发布2024年第一批上海市高新技术成果转化项目名单,立芯“LePlace布局及物理优化软件”项目成功通过认定。

Multi-Die系统验证很难吗?Multi-Die系统验证的三大挑战

在当今时代,摩尔定律带来的收益正在不断放缓,而Multi-Die系统提供了一种途径,通过在单个封装中集成多个异构裸片(小芯片),能够为计算密集型应用降低...

西门子发布Tessent RTL Pro加速下一代关键可测试性设计任务

西门子数字化工业软件近日推出Tessent RTL Pro 创新软件解决方案,旨在帮助集成电路(IC) 设计团队简化和加速下一代设计的关键可测试性设计(...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |