完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > Verilog HDL

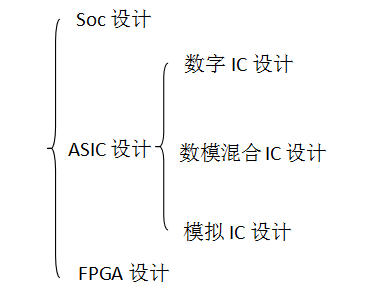

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

以模块为基础的设计

描述复杂的硬件电路,设计人员总是将复杂的功能划分为简单的功能,模块是提供每个简单功能的基本结构。设计人员可以采取“自顶向下”的思路,将复杂的功能模块划分为低层次的模块。这一步通常是由系统级的总设计师完成,而低层次的模块则由下一级的设计人员完成。自顶向下的设计方式有利于系统级别层次划分和管理,并提高了效率、降低了成本。“自底向上”方式是“自顶向下”方式的逆过程。

使用Verilog描述硬件的基本设计单元是模块(module)。构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。模块被包含在关键字module、endmodule之内。实际的电路元件。Verilog中的模块类似C语言中的函数,它能够提供输入、输出端口,可以实例调用其他模块,也可以被其他模块实例调用。模块中可以包括组合逻辑部分、过程时序部分。例如,四选一的多路选择器,就可以用模块进行描述。它具有两个位选输入信号、四个数据输入,一个输出端,在Verilog中可以表示为:

module mux (out, select, in0, in1, in2, in3);output out;input [1:0] select;input in0, in1, in2, in3;//具体的寄存器传输级代码endmodule

设计人员可以使用一个顶层模块,通过实例调用上面这个模块的方式来进行测试。这个顶层模块常被称为“测试平台(Testbench)”。为了最大程度地对电路的逻辑进行功能验证,测试代码需要尽可能多地覆盖系统所涉及的语句、分支、条件、路径、触发、状态机状态,验证人员需要在测试平台里创建足够多的输入激励,并连接到被测模块的输入端,然后检测其输出端的表现是否符合预期(诸如SystemVerilog的硬件验证语言能够提供针对验证专门优化的数据结构,以随机测试的方式进行验证,这对于高度复杂的集成电路设计验证可以起到关键作用)。实例调用模块时,需要将端口的连接情况按照这个模块声明时的顺序排列。这个顶层模块由于不需要再被外界调用,因此没有输入输出端口:

module tester;reg [1:0] SELECT;reg IN0, IN1, IN2, IN3;wire OUT;mux my_mux (OUT, SELECT, IN0, IN1, IN2, IN3); //实例调用mux模块,这个实例被命名为my_muxinitial //需要仿真的激励代码 begin endendmodule

在这个测试平台模块里,设计人员可以设定仿真时的输入信号以及信号监视程序,然后观察仿真时的输出情况是否符合要求,这样就可以了解设计是否达到了预期。

示例中的对模块进行实例引用时,按照原模块声明时的顺序罗列了输入变量。除此之外,还可以使用或者采用命名端口连接的方式。使用这种方式,端口的排列顺序可以与原模块声明时不同,甚至可以不连接某些端口:

mux my_mux (.out(OUT), .select(SELECT), .in0(IN0), .in1(IN1), .in2(IN2), .in3(IN3));//使用命名端口连接,括号外面是模块声明时的端口,括号内是实际的端口连接//括号外相当于C语言的形式参数,括号内相当于实际参数endmodule

上面所述的情况是,测试平台顶层模块的测试变量直接连接了所设计的功能模块。测试平台还可以是另一种形式,即测试平台并不直接连接所设计的功能模块,而是在这个测试平台之下,将激励模块和功能模块以相同的抽象级别,通过线网相互连接。这两种形式的测试平台都可以完成对功能模块的测试。大型的电路系统,正是由各个层次不同模块之间的连接、调用,来实现复杂的功能的。

Verilog HDL 快速入门

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),它是以文本形式来描述数字系统硬件的结构和行为的语言。 世界上最流行的两种硬件描述语言是Verilog HDL和VHDL。

注意,VerilogHDL是一种描述语言,它和常见的编程语言C有根本的不同。C语言,让计算机的CPU从上往下按顺序执行每一条指令,执行完程序就结束了。

而,VerilogHDL主要是描述了一个数字模块的结构,或者行为。有点像商业合同,合同里面也会描述产品的结构,产品的功能等等。合同的每一个条款,并不需要严格的先后顺序,只要把项目的方方面面都考虑完整,写下来就OK了。VerilogHDL也是这样。

我们用VerilogHDL描述数字模块的功能,剩下的交给编译器(如,Quartus),编译器会根据我们的要求设计重构FPGA内部硬件。对于大批懒人来说,这技术简直碉堡了。这就是EDA(Electronic Design Automation,电子设计自动化)。

好,下面就来认识一下VerilogHDL

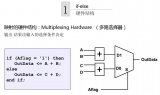

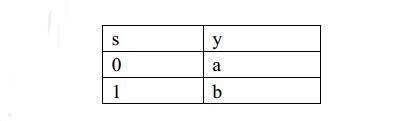

我们先设计一个“数据选择器”:

s是数据选择控制端,

a,b是输入信号,y是输出信号

代码如下:

module mux2_1(a, b, s, y); //模块名、模块接口名

input a, b, s; // 定义输入端口

output y; // 定义输出端口

/* s为0时,选择a输出;

s为1时,选择b输出。*/

assign y = (s == 0) ? a : b; //输出信号

endmodule12345678

每个Verilog文件中都有一个module 开始,endmodule 结束的代码块。

这个代码块的定义了一个名字叫 mux2_1 的模块,模块名后面紧跟的括号内写明了该模块的接口信号,相当于数字器件的引脚。

但是括号内没有说明接口的信号方向,所以紧跟着另起一行用input 和output 再说明一下。注释和C语法一样,可以用// 或 /* */ 。

assign 是Verilog的关键词,书上称为连续赋值。我一般把他视为“连线”操作,assign后面的紧跟的 y 在硬件上是一根导线(或输出引脚)。

assign y = (s == 0) ? a : b;

这句话的意思是:s如果为0,那么等号左边就是a,否则就是b。将这个表达式的输出结果接在输出引脚 y 上。

这就是一个简单的Verilog程序,不需要我们去设计与非门,直接表达你的你想要的功能就好了。然后,编译下载到FPGA,功能就实现了。

要注意的是,assign 后面永远跟着一个 =,它们是一起使用的。

即,assign xx = zz;

上面的2选1数据选择器,内部实现结构如下:

所以,上面的assign语句还可以这样写,直接使用逻辑表达式:

assign y = (a & (~ s)) | (b & s);

这个是在门级对逻辑关系进行描述,所以不属于行为描述,算是结构描述吧。下面这种描述方式,叫做门原语,算结构描述。这里的关键词wire 表示电路中的导线(信号线)。

module mux2_1(a, b, s, y);

input a, b, s;

output y;

wire ns, as, bs;

not(ns, s);//这里使用了一个非门,输出是ns,输入是s

and(as, a, ns);//使用一个与门,输出as,输入a和ns

and(bs, b, s);//使用与门,输出bs,输入b和s

or(y, as, bs);//使用或门,输出y,输入as和bs

endmodule12345678910

看,这是告诉我们电路中有什么元器件,又是怎么连接的,所以这个属于结构描述。

很明显,有时候结构描述比行为描述要费力得多,而且不太容易理解程序功能。

另外,上面的这个程序中,这4个逻辑门的顺序,可以随便写,不用管先后顺序。

这个数据选择器,还可以使用如下行为描述方法:

module mux2_1(a, b, s, y);

input a, b, s;

output y;

reg y; //reg 表示寄存器

always @(a, b, s)

begin

if(!s) y = a;

else y = b;

end

endmodule1234567891011

这里reg表示寄存器(存储器),需要提醒一下的是,assign后面只能接wire型,不能接reg型。(当然output从物理上也是wire)

为什么不能?因为寄存器的赋值除了需要输入信号,还需要触发信号(例如D触发器寄存器),assign?sorry,he can’t。

always @(a, b, s)中,括号里面的输入信号a,b,s表示敏感信号。

always @( ) 是连在一起使用的。

这句话的意思是,敏感信号列表中的任何一个信号发生变化,将会引发

begin …… end 之间的行为。

Verilog用begin和end包围代码段,相当于c语言中的大括号{ }的功能。

if(!s) y = a;

这里的“=”单独使用,叫做“阻塞赋值”。我把他理解为“串行赋值”。

比如,有这么一段代码:

b=a;

c=b;

那么最后,c的值就等于a,这个行为在描述的时候,语句的先后顺序,决定了赋值的先后。

在Verilog中,和它对应的还有一个“非阻塞赋值”,表示方法是 《=,我把这种赋值称为“并行赋值”。具体区别,请参考另一篇短文阻塞赋值和非阻塞赋值。

HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 ...

2020-08-26 标签:vhdlVerilog HDL 6.3万 0

Verilog HDL和VHDL是目前两种最常用的硬件描述语言,同时也都是IEEE标准化的HDL语言。

2020-08-25 标签:HDLvhdlVerilog HDL 9360 0

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完...

2019-11-20 标签:电路图硬件verilog hdl 5542 0

一、HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言。那么什么是硬件描述语言呢?为什...

2020-10-21 标签:fpgaIC设计Verilog HDL 4518 0

基于FPGA的SOC在嵌入式系统应用越来越广了,往往一个复杂系统使用一个单芯片基于FPGA的SOC就搞定了。比较流行的方案主要有Altera/xilin...

2020-09-01 标签:C语言Verilog HDL 4468 0

针对代码自动生成问题,对于顶层模块来说,承担的功能是自动地将底层数十个模块连接起来。对于底层模块来说,需要根据不同的功能定制需求,来自动化地生成所有功能...

2019-10-08 标签:Verilog代码Verilog HDL 4051 0

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完...

2019-11-13 标签:电路图vhdlverilog hdl 3416 0

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进...

2019-12-02 标签:fpga逻辑verilog hdl 3231 0

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完...

2023-12-07 标签:fpgaVerilogVerilog HDL 3146 0

类别:FPGA/ASIC 2016-10-10 标签:Verilog HDL

类别:可编程逻辑 2012-11-28 标签:Verilog HDLHDL语言

Verilog超详细教程-数字集成电路设计入门.pdf立即下载

类别:FPGA/ASIC 2015-02-03 标签:FPGA数字集成电路Verilog HDL

类别:可编程逻辑 2012-11-28 标签:CPU数字电路Verilog HDL

类别:FPGA/ASIC 2016-05-20 标签:Verilog HDL

类别:电子书籍 2011-09-22 标签:VHDLVerilog HDL

类别:FPGA/ASIC 2012-10-08 标签:电路数字逻辑电路Verilog HDL

Verilog HDL入门教程-Verilog HDL的基本语法立即下载

类别:FPGA/ASIC 2022-01-07 标签:Verilog HDL

类别:FPGA/ASIC 2015-02-03 标签:FPGAVerilog HDL按键消抖

类别:电子教材 2011-09-07 标签:电路华为Verilog HDL

电子发烧友网核心提示: 本例程是Verilog HDL源代码:关于基本组合逻辑功能中7段译码器的功能实现源代码。注意:程序运行在不同软件平台可能要作一些...

2012-10-15 标签:译码器Verilog HDLHDL源代码 2.3万 0

电子发烧友网核心提示: 本例程是Verilog HDL源代码:关于基本组合逻辑功能中多路选择器(MUX)的功能实现源代码。注意:程序运行在不同软件平台可...

2012-10-15 标签:Verilog HDLHDL源代码 2.3万 0

Verilog HDL verilog hdl和vhdl的区别

Verilog HDL是一种以文本形式描述数字系统硬件的结构和行为的硬件描述语言,也可描述逻辑电路图、逻辑表达式等。Verilog HDL和VHDL是目...

2021-07-23 标签:VHDLVerilog HDL 1.1万 0

基于Verilog HDL描述语言实现交通灯系统控制器的设计

EDA技术是依靠功能强大的电子计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系...

2020-07-21 标签:交通灯系统控制器Verilog HDL 8276 0

电子发烧友网核心提示: 本例程是Verilog HDL源代码:关于基本组合逻辑功能中二进制到BCD码转换的功能实现源代码。注意:程序运行在不同软件平台可...

2012-10-15 标签:Verilog HDLHDL源代码 7039 0

根据业界通用的SPI总线的标准,本文设计一种可复用的高速SPI总线。设计过程中很多变量都采用参数形式,具体应用于工程实践时根据实际需要更改参数即可,充分...

2012-09-04 标签:FPGASPI接口Verilog HDL 6650 0

电子发烧友网核心提示 :目前,硬件描述语言(HDL)可谓是百花齐放,有VHDL、Superlog、Verilog、SystemC、Cynlib C++、...

在数字信号的传输过程中,有时需要从多路输入数据中选出某一路数据,完成此功能的逻辑器件称为数据选择器,即所谓多路开关,简称MUX(Multiplexer)...

2020-07-20 标签:Verilog HDL多路选择器 4798 0

Verilog HDL 优点:类似C语言,上手容易,灵活。大小写敏感。在写激励和建模方面有优势。 缺点:很多错误在编译的时候不能被发现。 VHDL 优点...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |