台湾积体电路制造公司(简称为台积电(TSMC))最近宣布了其第四个28nm工艺进入了量产 - 28HPC Plus(即28HPC +)。台积电(TSMC)的前两项28nm工艺(聚氮氧化硅28LP和高K 金属闸28HP / 28HPL / 28HPM)已生产了数百万个生产晶片。台积电(TSMC)已利用28HPC优化了移动和消费设备在性能和成本之间的平衡需求,然后开发了28HPC +,从而进一步提高性能和降低泄漏。设计人员通过结合这些新工艺技术和专为这些工艺而设计的高质量标准单元逻辑库,可实现其性能、功耗和面积目标,同时减小设计进度风险。

本文介绍了六个方面,设计人员可以利用这些采用新工艺的最新逻辑库技术来优化其系统级芯片(SoC)的性能、功耗和面积。

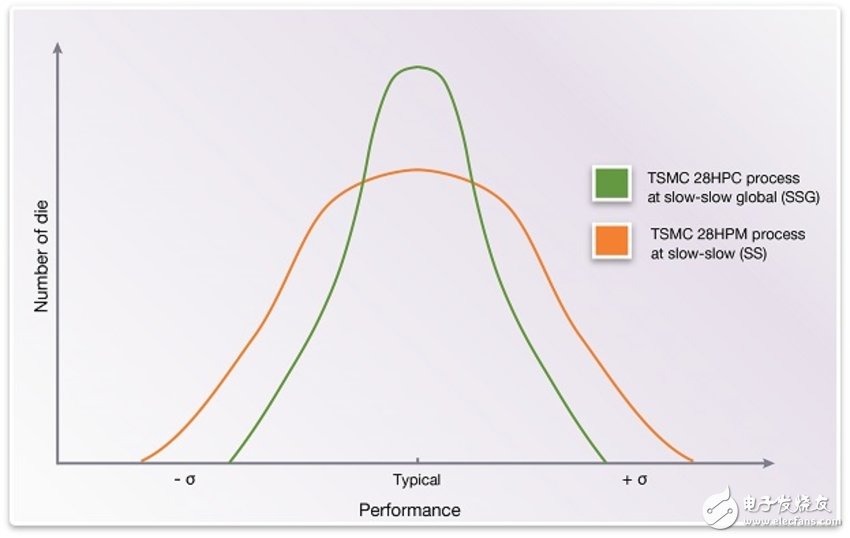

首先,台积电(TSMC)28HPC/HPC+工艺相对于28LP/HP/HPL/HPM,能更好的控制全局慢速和全局快速(SSG,FFG)工艺角,因此可以提高系统级芯片(SoC)性能。改良的性能可以使用较低驱动(较小的)逻辑单元来满足关键时序路径。

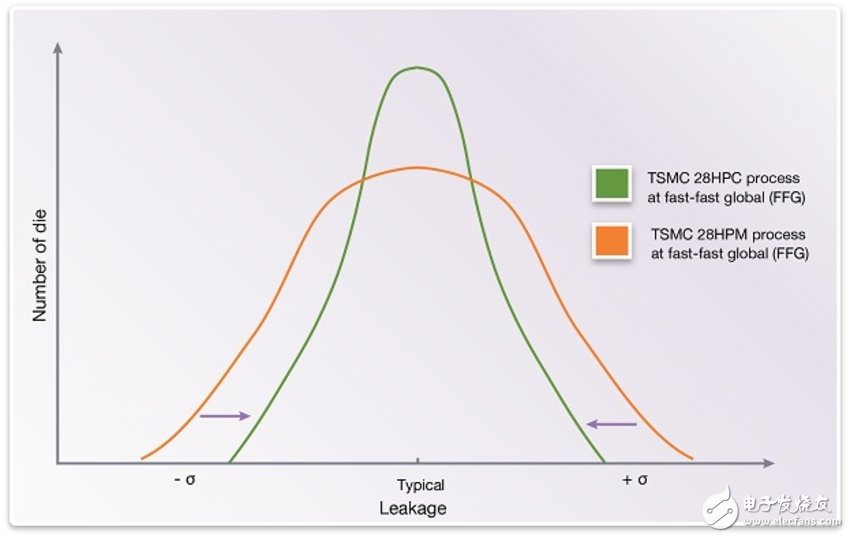

其次,台积电(TSMC)对28HPC工艺进行更严格的工艺控制,可以减少对应工艺角中的20%漏电来降低功耗。

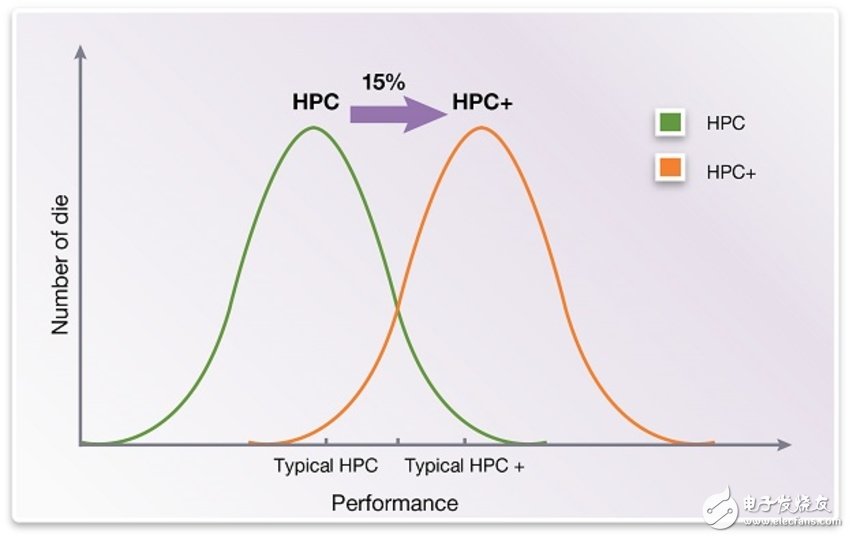

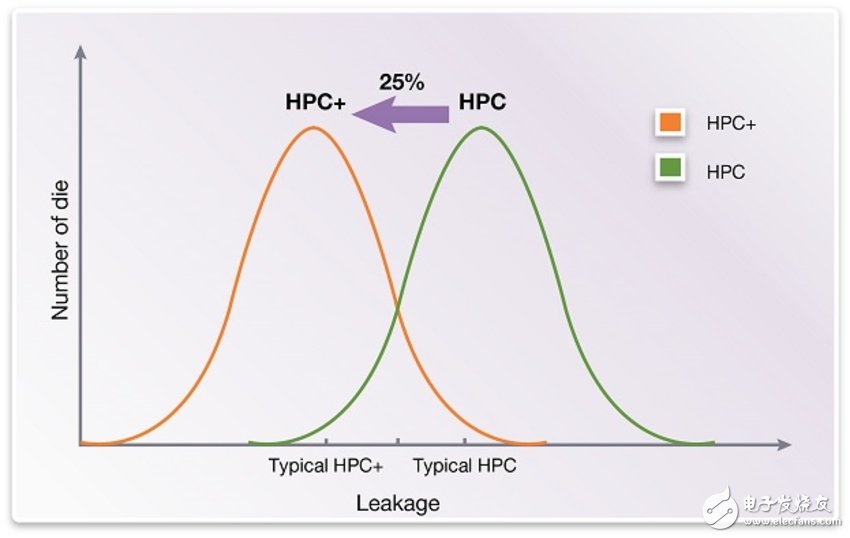

第三,28HPC +提高了15%性能,降低了25%漏电。

第四,28HPC和28HPC +都能减少面积,灵活的工艺规则,使得逻辑库设计者可以设计出更小的可布线性更好的逻辑单元。

第五,这些相同的灵活规则使得能够得到相对于28HPM工艺更长的沟道长度,从而减少最高50%的漏电,而不需要使用高成本的基于光刻的闸极偏置。

第六,在28HPC工艺引入的新的逻辑库功能,如多重延迟、多重建立时间和多位触发器(MBFF),可帮助设计人员优化处理器内核的性能和功耗。

创新工艺技术和逻辑库设计功能的结合,以及最新的EDA工具创新和流程,使系统级芯片(SoC)设计人员能够利用他们的设计技能,设计出最高性能、 最低成本、最低功耗的产品。

1.通过全局工艺角签核来提升系统级芯片(SoC)性能

传统开发的逻辑库,包括总工艺角工艺、电压、温度(PVT)模拟试验,可反映典型的P沟道和N沟道晶体管性能,统计学上性能最慢的(slow-slow或SS在3 sigma)和性能最快的(fast-fast或FF在3 sigma)。这些工艺角用于模拟典型的预期性能、最慢情况(用于触发器setup)和最快情况(用于触发器hold),且包括预期die和die之间、wafer和wafer之间以及lot和lot之间的变化,从而确保良率。

由于工艺变异性的降低,台积电(TSMC)能够提供高良率的新工艺角,称之为slow-slow global(SSG)。与之前的28HPM工艺相比提高了10-15%的性能,这需要更保守的SS 签核 (图1)。工艺变异性改进可使处理器运行速度提高10-15%,因此,28HPC逻辑库必须能够支持在更高的速度下电路的额外动态功耗和电迁移要求。

图1. 台积电(TSMC)28HPC SSG工艺角和28HPM SS 工艺角

2. 随着工艺变异性减小,闸门漏电流也减少

HPC工艺变异性的改进降低了晶体管泄漏,因此根据不同的工艺选项和条件,28HPC工艺将比28HPM减少约20%的漏电量(图2)。

图2. TSMC 28HPC FFG工艺角和28HPM FFG工艺角

3.使用28HPC +改进工艺秘诀

台积电(TSMC)利用28HPC +改善了28HPM和28HPC上使用的高K金属工艺,具有新的掺杂特性,并从高K金属闸上分离了一些原子,提高了15%的性能和降低25%的漏电流。

图3.左边的曲线显示了28HPC的性能分布,右图显示了28HPC +的性能分布。请注意,这些曲线比较了相同的SSG工艺角

图4.右侧曲线显示28HPC的漏电分布,左侧显示28HPC +处的漏电分布。请注意,这些曲线比较了相同的FFG工艺角

- 您可能感兴趣的周刊

- 讨论区

- 讨论列表 ()

- 最新周刊

-

凌华科技推出边缘视觉分析软件开发套件EVA SDK加速边缘AI视觉

0人收藏,221次浏览

-

一切面向未来!英飞凌将重磅亮相深圳国际电子展暨嵌入式系统

0人收藏,566次浏览

-

NLP中基于联合知识的任务导向型对话系统HyKnow

0人收藏,406次浏览

-

计算机视觉中如何调用OpenCV库

0人收藏,536次浏览

-

Cortex-M裸机环境下临界区保护的三种实现

0人收藏,371次浏览

- 更多周刊 >>

- 文章目录