| Abstract: This FAQ discusses answers to general communication questions as well as Maxim device-specific questions. This set of FAQs is designed to address some of the more common questions that may arise when using Maxim telecommunication devices in new or existing designs. The questions are divided into different categories based on specific information areas. Because some devices like the DS2155 have a combination of features, it is possible that questions will span multiple categories. Revision: March 13, 2009 Section 1. General Telecommunication Questions

1. General Telecommunication QuestionsQ1. In T1, what is the difference between superframe (SF)/D4 and extended superframe (ESF)?A1. While both formats contain the same number of channel time slots, the SF format is a 12-frame structure, while ESF contains 24 frames. Both use the 8th bit of each channel time slot in every 6th frame for signaling, thus providing the SF format with A/B signaling bits and the ESF format with A/B/C/D signaling bits every multiframe. Also, the ESF format uses the F bits to provide frame alignment, CRC-6 check bits, and a 4kbps data link. The SF format divides the F bits into Ft and Fs bits. The Ft bits are terminal-framing bits that identify frame boundaries, and the Fs bits are signaling-framing bits that identify signaling frames.Q2. What is the difference between T1 and E1?A2. The main differences between T1 and E1 are the operating frequency, the number of time slots, the pulse shape, the characteristic line impedance, and the signaling method. The T1 system operates at 1.544MHz with a total of 24 time slots. The T1 pulse shape contains overshoot and undershoot and is driven on a line impedance of 100Ω. Finally, digital messages to signal on/off-hook or other conditions are sent using robbed-bit signaling. The E1 system operates at 2.048MHz with a total of 32 time slots. The E1 pulse shape is a perfectly rectangular pulse shape and is driven on a line impedance of 120Ω or 75Ω. Finally, digital messages to signal on-/off-hook or other conditions are sent using channel-associated signaling.Q3. What is the difference between T1 and J1?A3. J1 commonly refers to the derivation of the North American T1 standard that is used exclusively in Japan. Differences exist between J1 and T1 in the yellow alarm generation for superframe (SF) and extended superframe (ESF) modes. Also, the CRC-6 calculation in ESF mode is different. In J1 SF mode, the yellow alarm is generated when a '1' is transmitted in the 12th F-bit, as opposed to T1 SF mode in which a '0' is transmitted in the 2nd bit of all timeslots. In J1 ESF mode, the yellow alarm is generated by transmitting 'FFFF' in the data link (DL) section of the F-bits, as opposed to T1 ESF mode in which 'FF00' is transmitted in the data link. In J1 ESF mode the CRC-6 calculation includes the frame alignment signal and data link F-bits. However, for T1, all of the F-bits are set to '1' when the CRC-6 calculation is performed.Q4. What is SLC-96 and how does it relate to T1?A4. SLC-96 (pronounced "slick 96") is used in conjunction with T1 as a digital-loop carrier system, which provides service for up to 96 subscribers over three to five separate T1 lines. SLC-96 was the first widely deployed digital-loop carrier system. SLC-96 operation consists of two terminals: a central-office terminal (COT) and a remote terminal (RT). The COT multiplexes the analog phone lines from a class 5 switch into four T1 lines with an optional fifth T1 line used for protection switching. The RT is the termination point for the T1 lines and converts them into subscriber phone lines. SLC-96 revolutionized the telecommunication industry by introducing digital electronics into the local loop as a permanent replacement for cable. The frame format of SLC-96 closely resembles that of the super-frame (SF or D4) format, except that additional data-link information is transferred in the framing bits. This allows the deployment of advanced functions such as single-party, multiparty, coin-telephone, and special-service circuits. For more information on SLC-96, please consult Telcordia specification TR-008.Q5. How are frames, channel time slots, and bits numbered in T1 and E1?A5. According to the ITU-T specification G.704, the numbering structures for T1 and E1 digital transmission systems are as follows:In T1 systems, the frames are numbered 1 to 12 in the SF/D4 format, and 1 to 24 in the ESF. The channel time slots are numbered 1 to 24. The bits are numbered 1 to 8, with the 8th bit being the least significant bit (LSB). In E1 systems, the frames are numbered 0 to 15 in the CRC-4 and CAS multiframe formats. The channel time slots are numbered 0 to 31. The bits are numbered 1 to 8, with the 8th bit being the least significant bit (LSB). Q6. What are the differences between robbed-bit signaling (RBS), channel-associated signaling (CAS),and common-channel signaling (CCS)?A6. RBS is the original signaling system used by T1 and provides either 2 or 4 signaling bits per channel depending on the multiframe format. In RBS, the LSB in every channel of every 6th frame is used as a signaling bit. Hence, in the SF format there is an A/B bit for every channel, and in the ESF format there is an A/B/C/D bit. CAS is the original signaling system used by E1 and provides 4 signaling bits for every channel. In CAS, channel 16 is reserved for signaling and the A/B/C/D bits for each channel are divided among 16 frames. Frame 0 contains the alignment signal, alarm, and spare bits. Frame 1 contains the A/B/C/D bits for channel 1 in the upper half of the channel, and the A/B/C/D bit for channel 16 in the lower half. The remaining 14 frames follow the frame 1 format accordingly. In recent years, the term RBS has been replaced by CAS, which is now used to refer to bits that are associated with a specific channel whether it is in the T1 or E1 format. CCS is used by either T1 or E1 and refers to a system that does not use a specific bit structure for signaling. Instead, all or part of a channel is used to pass messages between two systems to indicate how a channel is being used. This type of system is commonly found in ISDN, which uses a D channel to pass messages.Q7. What are the red, blue, and yellow alarms in a T1 system?A7. The three different alarms are used to indicate different problems in transmission or reception of data in the T1 system. To explain the different alarms, it is necessary to have a simple T1 system model that has a T1 signal sourced from the central office (CO) through a repeater to the customer premises equipment (CPE) and back. The red alarm is actually a CPE state resulting from the detection of an incoming signal failure (i.e., from a line break). The yellow alarm is transmitted to indicate the loss of an incoming signal. In the case where the CPE is in the red alarm state, it will transmit the yellow alarm to the repeater. The blue alarm is transmitted upon loss of the originating signal or when a signal is actively disrupted. In the case where the repeater receives the yellow alarm, it will transmit the blue alarm back to the CO. Upon receiving a blue alarm, the CO will transmit a yellow alarm to the repeater to indicate the loss of incoming signal. It may seem confusing as to whether a piece of equipment should transmit a yellow or blue alarm. Generally, any piece of equipment on the endpoint (i.e., a CPE or a CO) will transmit the yellow alarm to indicate the loss of signal, while equipment in the middle of the path (i.e., a repeater) will transmit the blue alarm.Q8. What are the alarm indication signal (AIS), remote alarm indication (RAI), and distant multiframe alarm (DMA) in an E1 system?A8. The AIS and RAI are essentially the same as the T1 blue and yellow alarm, respectively. The AIS is transmitted upon loss of the originating signal or when the incoming signal is actively disrupted. The RAI is transmitted to indicate the loss of an incoming signal. The DMA is specific to CAS signaling and is transmitted when the correct CAS multiframe alignment signal is not found.Q9. What is the difference between AMI, B8ZS, and HDB3?A9. AMI, B8ZS, and HDB3 are different types of line coding used in T1 and E1 communications systems. AMI (alternate mark inversion) is used in both T1 and T1 systems. B8ZS (bipolar with 8 zeros substitution) is used in T1 systems. HDB3 (high-density bipolar 3) is used in E1 systems.AMI is the most basic encoding scheme, in which ones are represented by voltage pulses and zeros are represented by the lack of a voltage pulse. In AMI, the polarity of each pulse is the opposite of the previous pulse. The problem with using AMI is that if not enough voltage pulses are sent down the line, the receiver will not correctly decode the data stream. To solve this problem, two different encoding schemes were developed to replace a sequence of zeros with a special code word of voltage pulses. The B8ZS encoding scheme replaces each sequence of 8 zeros with the code of 000VB0VB, where the V pulse (bipolar violation) has the same polarity as the previously pulse and the B pulse (correct bipolar pulse) has the opposite polarity as the previous pulse. HDB3 encoding is slightly more complicated because, unlike the B8ZS encoding that has a balance of positive and negative voltage pulses, the HDB3 encoding must select a code word to maintain the balance. In HDB3, each sequence of 4 zeros is replaced by 000V or B00V. The decision of which code word to use is made so that the number of B pulses between consecutive V pulses is odd. This maintains the balance of positive and negative pulses when using HDB3 encoding. The table below shows examples of the different encoding types.  *The previous V bit is directly before the beginning of the data sequence. Q10. What are the names of the regulatory bodies that govern the requirements for network interface line protection?A10. There are many different regulatory bodies that govern how the T1 and E1 line interfaces must operate under surge and power cross conditions. The list below contains the commonly referenced regulatory bodies and the specifications that apply in each case.FCC Part 68: Effective July 23, 2001, the Administrative Council for Terminal Attachments (ACTA) assumed operational responsibility for Part 68. ACTA is the newly-formed industry council for Part 68 certification requirements and administration. This followed the FCC's decision to privatize its Part 68 responsibilities and select TIA and ATIS to serve as joint sponsors of the Council. Because of this, FCC Part 68 has been renamed to be TIA/EIA-IS-968. Old Part 68 URL: www.fcc.gov/wcb/iatd/part_68.html New Part 68 URL: www.part68.org UL 1950: Underwriter Laboratories has made changes to the naming of the over-voltage specifications known as UL 1950, 3rd edition. This specification is now referred to as UL 60950, 3rd edition. Old UL1950 URL: www.ul.com/pag1950 New UL60950 URL: data.ul.com/pagos Q11. What is the difference between jitter and wander?A11. Jitter is defined as the magnitude of phase variation (with respect to a reference clock or data signal) whose frequency of variation is greater than 10Hz. Jitter is measured in unit intervals (UI), where 1 UI is equal to one data bit-width. For an E1 signal, 1 UI is equal to 488ns, and for a DS1 signal, 1 UI is equal to 648ns. However, if the rate of change in phase is less than 10Hz, then this phenomenon is known as wander and is measured in nanoseconds.Q12. What standards bodies govern telecommunications equipment compliance?A12. The following is a list of the largest telecommunications standards bodies:

Q13. When the boundary scan is not used, what will be the pin conditions for the JTAG test access pins?A13. For the boundary scan, each device uses five pins. These are the JTCLK, JTDI, JTMS, JTRST, and JTDO pins. When the boundary scan is not used, these pins must have a steady value. For JTCLK, it should be pulled high. JTDI and JTMS should be unconnected or high, because they both have an internal 10kΩ pullup resistor. JTRST also has a 10kΩ pullup resistor, and it asynchronously resets the test access port when the pin is toggled from low to high. It needs to be held high or low when the boundary scan is not used. JTDO should be left unconnected.Q14. For a universal T1/E1 interface on the customer side, do T1/E1 service providers expect customer equipment to provide a connection between the Tx and Rx pairs through the transformer center taps? Or, can the T1/E1 service provider ignore this connection and leave it out of the design?A14. The need for transformer center tap connection between the Tx and Rx pairs depends on the design and, most of the time, it is recommended that this connection is ignored. Most T1 service providers do not expect there to be a connection between the transformer center taps of Rx and Tx pairs.Please refer to application note 324, "T1/E1 Network Interface Design," for more information regarding design of a telecommunications network interface circuit using Maxim line interface units (LIUs) or single-chip transceivers (SCTs). For an E1 network, hardware board designers cannot connect the center taps of Rx and Tx at any time. For a T1 network, the designers need to make sure that they are using 5V parts if they want to connect the center taps of Rx and Tx sides of the transformer. With 3.3V parts, however, they cannot connect the center taps. If the customer is planning to create a new design with DS2155/DS2156, then it is recommended to refer to Figures 4 and 5 of application note 324. However, if the customer is using the DS2151 or DS2153, then it is recommended to refer to Figures 2 and 3 instead. Q15. What is the difference between channelized and unchannelized T1?A15. Channelized T1 splits into 24 voice-grade channels, with each running at 64kbps. If you have a need for numerous local phones, it is much cheaper to get them delivered on T1 channels than as individual phone lines. Channelized T1 is developed and optimized for uncompressed voice communications. The channelized approach is required for access to the tradition PSTN.Unchannelized T1 provides you with 1.536Mbps (minus a framing bit), which you can split up anyway you choose. It is ideal for most data-communications applications, as well as compressed voice, video, and IP telephony. For example, you can split a leased T1 into 12 voice-grade channels to support 12 voice conversations, and then use the remaining 768kbps for either reasonably high-speed access to the Internet or for videoconferencing with your distant office. You can also compress voice to run at speeds of perhaps 8kbps or less by using IP telephone techniques and, therefore, put many more voice calls over a single T1 pipe. Q16. Can I modify the codes of Maxim telecommunication drivers?A16. No. Maxim has the license of the driver that allows us to provide the driver code to the customers, but it does not change the ownership of the driver nor put it under the GNU licensing schemes. The customer can extend the driver through the macros or other recommended function commands.2. General Device Operation QuestionsQ1. What are the standard register settings for a Maxim telecommunication device?A1. Because there are many different ways that a T1, J1, E1, T3, or E3 device can communicate, there are no standard register settings. After initialization, there are three register types that control all major device operations. These are the receive control registers (RCRx), the transmit control registers (TCRx), and the common control registers (CCRx).Q2. What software is available for use with Maxim telecommunication devices?A2. Software drivers are available for the following T1/E1 devices:DS2152, DS2154, DS21(Q)352, DS21(Q)552, DS21(Q)354, DS21(Q)554, DS21(Q)55, DS21455, and DS21458. Software drivers are available for the following T3/E3 devices: DS3112, DS3141, DS3142, DS3143, DS3144, DS3151, DS3152, DS3153, and DS3154. The drivers are written in C and supplied by Ncomm®. The drivers may be obtained by submitting an email request to telecom.support@maxim-ic.com. Please note that company contact information must be provided before the request can be processed. Q3. Can you provide an example design using various processors?A3. There are several example designs using processors by various manufacturers located in the Communication Circuits section of our online application notes.Q4. Can you provide a reference design for the network interface?A4. Application note 324, "T1/E1 Network Interface Design," provides all the information required to implement the network interface.Q5. What is the meaning of the markings on Maxim devices?A5. Example markings for the DS2149 28-pin PLCC package:MAXIM DS2149 - Device YYWWRR - Date code ###XX - Lot code Date Code: YY - Last two digits of the year of assembly WW - Week within the year of assembly RR - Revision Lot Code: ### - Last three digits of the lot number XX - Up to two alpha characters that are behind those digits Q6. What is the difference between the device identification register (IDR) value and the device revision markings on Maxim devices?A6. The device revision, printed on the top of the package, consists of an alphanumeric combination that is two characters in length. The alpha character denotes the current level of an all-layer die revision, with the first die being denoted with the letter 'A'. The numeric character denotes the current level of a metal layer die revision, with the first die being denoted with the number '1'. If only the metal layers of the die are revised, then the numeric portion is increased by one. When all the layers of the die are revised, then the alpha portion is increased by one letter and the numeric portion is returned to the number '1'. Further changes follow the same standard.For all Maxim T1/E1 devices with an 8-bit data bus, the device identification register (IDR) is eight bits in length. The upper four bits are used to identify the device family (e.g., the DS2155, DS21354, DS21552, etc.) The lower four bits are used to identify the specific revision of the die. Because the lower four bits cannot denote the same alphanumeric combination as printed on the device, the binary value is simply increased by one when any revision is made to the die with the value of '0000' indicating the 'A1' revision. It should be noted that some Maxim telecommunication devices have a 16-bit data bus and follow a different identification register model, which is detailed in the specific device's data sheet. Q7. What do the suffixes after Maxim telecommunication device names indicate?A7. Maxim creates new part numbers with different suffixes, such as DSxxxxL and DSxxxxLB, to separate the package type, revision, and device type in inventory.For example, The "L" in DS2155L indicates that the DS2155 is packaged in an LQFP, commercial type. Commercial type devices have a temperature range of 0°C to +70°C. The "G" in DS2155G indicates that the DS2155 is packaged in a CSBGA, commercial type. The "LN" in DS2155LN indicates that the DS2155 is packaged in an LQFP, industrial type. Industrial type devices have a temperature range of -40°C to +85°C. The suffix may also represent a different package outline drawing or materials analysis. Q8. What kind of operating system is needed for Maxim telecommunication drivers?A8. Maxim telecommunication device drivers are written in C and supplied by NComm. The software is designed to be operating system independent and portable across different operating systems/platforms, such as Windows®, Linux®, and VxWorks®. The user can integrate the driver with their application that is not directly functional on the operating system. The user needs only to create code that makes the driver to work within its environment.The Maxim telecommunication device drivers can be obtained by submitting an email request to telecom.support@maxim-ic.com. Please note that company contact information must be provided before the request can be processed. 3. Framer/Single-Chip Transceiver QuestionsQ1. How are the DS21x5y, DS215y, or other telecommunication devices initialized?A1. Some devices like the DS2155 T1/E1 SCT or DS2148 LIU, offer a power-on reset and a hardware reset pin that clears out all the registers. Other devices require software to write a 0x00 to address space 0x00 to 0xFF, regardless of register type or documented presence. This ensures that all of the registers are cleared and the device is in normal operation mode.Q2. Do Maxim telecommunication devices support unframed or transparent-mode operation?A2. Yes. A description of how to configure a device for unframed or transparent-mode operation is provided in application note 336, "Transparent Operation on T1, E1 Framers and Transceivers."Q3. Is it necessary to repeat the same data on the TSIG pin for an entire multiframe when using hardware-based signaling?A3. Yes. The chip is designed to expect signaling data during the least significant nibble throughout all timeslots and all frames of a multiframe. Failure to do so causes unstable results.Q4. How are JTAG functions implemented on SCT multichip modules such as the DS21Q352/DS21Q55?A4. A multichip module is any device that contains multiple die or devices housed in the same package. The DS21Q352, DS21Q354, DS21Q552, DS21Q554, and DS21Q55 are all examples of quad-port, SCT multichip modules. Each of these multichip modules has four single-port devices with daisy-chained JTAG functionality. This is necessary because each single-port device contains a JTAG test access-port controller, and because the BSDL language lacks the ability to define multiple test access-port controllers. In the module, some pins such as address and data buses are tied together. The JTAG pins are either tied in parallel or daisy-chained, as appropriate. More detail can be found in the device's data sheets. To create the proper JTAG scan chain, four copies of the single-port version of the device need to be placed in the JTAG chain. For example, if a DS21Q55 were placed on the board, the proper BSDL file would be the DS2155.When using multichip modules in the JTAG chain, the design may need to be modified slightly to reflect the internal connections present in the module. The amount of modification depends on whether the module is being used on a physical tester or in conjunction with a simulation program. If the module is being used on a physical board, then the implementation will only require that four copies of the single-port BSDL file to be placed sequentially in the JTAG test chain. However, if the module is being used in a simulation, the implementation may be slightly more complex. The first way to create a useful simulation model is to create a hierarchy in the design. The quad-port module is considered to be a separate board made of four single-port devices. The connections are then made to match those present inside of the module itself; these connections are detailed in the device data sheet. Another way is to directly alter the netlist after the design is complete. This will essentially trick the simulation into believing that the quad-port module is four separate single-port devices. BSDL files are available on the Maxim website. Q5. Is the DS2155 pin compatible with other Maxim SCTs?A5. The DS2155 is closely pin compatible with DS2152/DS2154, DS21552/DS21554, and DS21352/DS21354 SCTs. The biggest difference between the DS2152/DS2154, DS21552/DS21554, and the DS2155 or DS21352/DS21354 devices is that the former devices all operate on 5.0V, while the latter operate on 3.3V (with 5.0V I/O tolerance). The DS2152/DS2154 also do not support many of the pins/functions that the DS2155 has available. The DS21552/DS21554 and DS21352/DS21354 offer the best compatibility, but there are some pins/functions that were changed between the DS21x5y and the DS2155. The table below notes all the differences between the devices' pins.

Q6. Do the Maxim T1 devices support SLC-96?A6. Because of the complexity of the SLC-96 specification, special synchronization circuitry, data registers, and status registers were added to the T1 devices that allow the system designer to take advantage of the SLC-96 functionality. Maxim T1 devices like the DS2141A, DS2151, DS2152, DS21352, DS21552, and DS2155 are capable of SLC-96 operation in both transmit and receive directions. On the receive side, the devices are able to synchronize onto a received SLC-96 pattern and extract the message bits. On the transmit side, the devices are able to insert the SLC-96 synchronization pattern and message bits. The devices also have the option to perform SLC-96 functions externally through hardware pins or internally through software registers and interrupts.Q7. What are some common problems and solutions when using the DS2155's internal HDLCs?A7. The DS2155 SCT has the ability to transmit and receive packet data over a T1/E1 or J1 line. This device contains two high-level, data-link controllers (HDLC), each of which can be configured for use with time slots, Sa bits (E1 mode), or the FDL (T1 mode). Each controller has a 128-byte FIFO in the transmit and receive paths.The most common problems are receiving incorrect data in the packets, not receiving enough data bytes in the packets, or receiving a prematurely terminated (aborted) packet. Fortunately, for each controller, the DS2155 provides separate registers that contain information about any errors that occur when receiving data. These registers provide a basis for what action, if any, the system needs to perform for continuous normal operation. The HDLC registers provide information on the following receive packet conditions: In Progress, Packet OK, CRC Error, Abort, Overrun, and Message Too Short. The first condition, In Progress, means the HDLC is receiving a packet and no alarms have been detected. Depending on the system, certain actions such as retrieving data from the FIFO may be necessary. The second condition, Packet OK, means the HDLC received a correctly formatted packet, and the data has been checked against the transmitted CRC bytes. The third condition, CRC Error, occurs when the calculated CRC for the received data does not match the transmitted CRC bytes in the packet. The fourth condition, Abort, happens when the HDLC receives the abort signal. The fifth condition, Overrun, occurs when the receive FIFO exceeds the maximum capacity of 128 bytes. This usually indicates that the microcontroller did not read the FIFO data faster than the DS2155 writes the received data into the FIFO. The final condition, Message Too Short, indicates that 3 or fewer bytes, including the CRC bytes, were received as a message. The cause of some of the error conditions can be found by simple line testing, while others may require in-depth knowledge of the system software. There are two main causes of CRC errors: either the transmission line quality is poor, or there may be problems with the HDLC software/hardware on the transmit or receive side. Testing the line quality is accomplished by performing a bit error-rate test while in remote loopback. If the line is not the problem, further investigation into the HDLC software/hardware is required. The Abort condition is difficult to solve because the cause is most likely on the transmit side, which may not be under the designer's control. A common cause is a buffer under run condition in the transmit FIFO, which occurs when the transmit HDLC needs to send data, but the processor has not written data into the FIFO. Sometimes, a faster processor solves the problem, but changes often need to be made in the software/hardware. The DS2155 has special "watermark" registers that the processor can use as indicators of the current FIFO status. The 'watermark' registers can be serviced in either a polled mode or can be interrupt-driven to ease the processor load. The Overrun condition is caused when the processor does not read data out of the receive FIFO as fast as the receive HDLC writes data into the FIFO. Similarly, a faster processor may solve this problem, but again changes may need to be made in the software/hardware. The DS2155 has special 'receive packet bytes available' and 'watermark' registers that the processor can use as indicators of the current FIFO status. The 'receive packet bytes available' register is a simple indication of how much data is currently in the FIFO, while the 'watermark' registers can be serviced or interrupt driven as described above. The Message Too Short condition is very easy to deal with—it is used to indicate that the HDLC packet received did not contain enough data and, as such, is an illegal packet and should be ignored. Q8. Why does the external loopback on the DS26401/DS2155 not work properly, though the remote and payload loopbacks work fine?A8. The cause for this error could be that you are not using the correct source for the transmit clock (TCLK) in the DS26401. The DS26401DK was designed with three major components: a LIU, a framer, and a FPGA for specific signal multiplexing. Unfortunately, the receive clock from the LIU goes to the DS26401 and a test-point header, but not to the FPGA. Therefore, to perform an external loopback, you need a way to connect RCLK to TCLK.Solution One Manually jumper RCLK and TCLK on the DS26401DK with the test-point headers. Make sure the TCLK register in the FPGA is three-stated. This is the default value. Solution Two You can control the source on the transmit clock with TCR3 register (TCR) using Bit 4 (TCSS0) and Bit 5 (TCSS1). Set TCSS0 and TSSC1 to a logic "1". This will cause the transmit clock to be the same as RCLK from the LIU. Q9. What are the differences between the DS21455/DS21458 and the older DS21Q55?A9. The DS21Q55 is a quad-port, 27mm x 27mm multichip module consisting of four independent DS2155 transceivers. The DS21455 is a monolithic version of the DS21Q55, and is meant to be a drop-in replacement that is package, pin, and software compatible. The DS21458 contains exactly the same die as the DS21455 and is software compatible, but it is produced in a smaller, 17mm x 17mm package. Note: New designs should use the DS21455 instead of the DS21Q55.Q10. What is the functional behavior of the RCLK pin output when the signal at the network connection of RTIP/RRING is lost?A10. When the device loses the signal at the network connection of RTIP/RRING, it enters the carrier-loss state. In this state, the RCLK output will slowly drift from the recovered clock, which is no longer present, to the master clock (MCLK) input. Once the network connection is restored, the RCLK output will again lock with the signal present on RTIP/RRING.Q11. When operating T1/E1 devices in T1 mode, can the TCLK pin input frequency be 2.048MHz?A11. T1/E1 devices (such as the DS2155, DS21458, and DS26528) provide a wide range of features aimed at easing device configuration. One of these features is the ability to use a single-frequency master clock (MCLK) in either T1 or E1 mode. Unfortunately, the device still requires that the external TCLK pin input be at the actual line frequency. In T1 mode, this means the input frequency on the TCLK pin must be 1.544MHz. However, there are some ways around this limitation, using either the elastic stores for rate conversion, or using the master clock PLL to source TCLK internally at 1.544MHz.4. Line Interface QuestionsQ1. What transformers are recommended for the Maxim telecommunication devices?A1. A listing of recommended transformers is provided in application note 351, "T1/E1 and T3/E3 Transformer Selection Guide," and in the last section of the application note 324, "T1/E1 Network Interface Design."Q2. What is the function of the capacitor in the transmit path?A2. The reason that the capacitor exists is to block the flow of current between the TTIP and TRING pins, preventing unnecessary power draw. The capacitor value stated in the data sheet was chosen so that it appears as a short circuit at the transmission frequency and an open circuit at DC. Although the value is somewhat subjective, this value has been proven to work with all Maxim telecommunication devices and should not be altered. If the value must be changed, another value can be calculated by the formula f = 1/RC. R is the load as seen by the device (1/4 of the line impedance), C is the capacitor value, and f is the mean signal frequency. Remember that an all ones signal appears as 772kHz, and a lower ones density decreases the signal frequency. The capacitor must be chosen such that the signal frequency is not blocked.Q3. When using the DS2148 LIU in NRZ mode, how should the signals for the TPOS and TNEG pins be connected?A3. Connect the NRZ input to TPOS and tie TNEG to ground.Q4. What are the selection criteria for the line build-out (LBO) bits in E1 applications?A4. The criteria depend not only on the intended application for the SCT, but also to what type of system the design is interfacing. The line interface circuit can be designed many ways and the following applications explain the difference in the three major operations obtained by switching the LBO.75Ω/120Ω Normal This is used for E1 short haul, when the system will be used in a confined environment where the return loss is insignificant and there will be no exposure to lighting surges or power-line cross conditions. 75Ω/120Ω with Protection Resistors or 75Ω/120Ω with High Return Loss These two operations are used for E1 long haul, when the system will interact with the outside environment. Here, the return loss is also considered to be insignificant. In order protect the system from lighting surges and power-line cross conditions, power resistors are placed in between the RJ48 connector and the network side of the transformer. Q5. When the cable is unplugged for the network interface, why does the receive carrier loss (RCL) bit in the status register or the pin of the LIU or SCT occasionally report an incorrect status?A5. It is unlikely that the device actually reports the RCL status incorrectly. The most common cause of this problem is that a noise/signal source is coupling into the receive-side interface (the RTIP and RRING pins). The following are suggestions to verify that noise/signal coupling is the problem and what can be done to solve the problem.

Q6. What are the differences between the DS21448 and the older DS21Q48/DS21Q348?A6. The DS21Q48 and DS21Q348 are quad-port, 17mm x 17mm multichip modules that consist of four independent LIUs. The DS21Q48 operates at 5.0V and is composed of DS21Q48 devices, while the DS21Q348 operates at 3.3V and is composed of DS21348 devices. The DS21448 is a monolithic version of the DS21Q348, and is meant to be a drop-in replacement that is package, pin, and software compatible. The DS21448 only operates at 3.3V and cannot be used as a direct replacement for the DS21Q48.Q7. Why is the master clock (MCLK) signal necessary for proper device operation?A7. Because of the hybrid analog and digital nature of the line interface, the master clock signal present on the MCLK pin is necessary to operate both the clock- and data-recovery engine and the jitter attenuator. Without the master clock, the device would not be able to properly recover the clock and data signal present on the incoming line. The master clock signal is also used as an alternate recovered clock on the RCLK pin whenever the device enters a receive carrier loss state. To ensure that the device operates within specifications, the master clock should be derived from an accurate low-jitter source such as a crystal oscillator. T1/E1 devices usually use a source with a frequency tolerance rating of ±50ppm (or better) and a period jitter rating measured in picoseconds.Q8. Is the center-tap connection of the transformer secondary side necessary for better analog performance of the DS3151, DS3152, DS3153, and DS3154 devices?A8. Connecting the center tap of the transformer secondary side to the ground is optional. If used, the center tap if used would serve to reduce the common-mode noise. However, the DS315x devices are all designed to use a coaxial cable connection, which has little if any common-mode noise. In addition, if the traces between the transformer and the DS315x device pins are short in length, the effects of inductance and common-mode noise will be negligible.Q9. Is it possible to use a sine-wave oscillator instead of a square-wave oscillator to supply different frequencies at the CLAD for the DS325x?A9. Yes. It is possible to use a sine-wave oscillator to supply sinusoidal frequencies to the input of the DS325x's CLAD. The lowest voltage of the sine wave cannot go below the diode drop, and it is recommended that the voltage is a 3.0V sine wave with minimum of 0V.Q10. Does the DS26334 LIU support internal impedance-matched operation? If so, what are the steps to program the device in this mode?A10. Yes, the DS26334 does support internal impedance-matched operation for devices that are revision A2 or later. Revision A1 does not support this mode. When the DS26334 is in internal impedance-termination mode, RTIP and RRING require no external resistance components. However, for better internal resistance accuracy, a 16.5kΩ ±1% resistor is required on the RESREF pin. For external termination mode, the RESREF pin must be tied to GND. It is also important to note that, in internal impedance-termination mode, a 1:1 transformer on the receive side is required. If you are using a 1:2 transformer, a 30Ω resistor must be placed in parallel with RRTIP and RRING.5. BERT QuestionsQ1. When using the DS2155, DS2172, or DS2174 bit-error-rate tester (BERT) function with a pseudorandom bit stream (PRBS) pattern, what status bits must be checked to validate that the pattern is being correctly received?A1. Status Register 9 (SR9 in the DS2155) should be checked to ensure that the BERT is in synchronization and that the device is not receiving an all zero pattern. When properly receiving a PRBS pattern, the synchronization bit (SYNC or BSYNC in the DS2155) equals 1, and the receive-all-zeros bit (RA0 or BRA0 in the DS2155) equals 0. When receiving a PRBS pattern, it is important to verify that the receive-all-zeros bit equals 0 because the BERT uses a linear-feedback shift register (LFSR), which enters a 'dead state' when it receives all zeros. If the receive-all-zeros bit equals 1, it is possible for the BERT bit counters to begin counting received bits. This would result in the miscalculation of the bit-error rate. Therefore, the receive-all-zeros bit should be checked whenever receiving a PRBS pattern.Q2. Why do the DS2172/DS2174 BERT devices remain in synchronization when the clock signal applied to the receive-clock (RCLK) pin is removed or held in a steady state?A2. Both the DS2172 and the DS2174 can remain in synchronization when the clock signal applied to the receive-clock (RCLK) is removed. This reason for this behavior is that the state machine that controls the receive synchronization is clocked by the signal applied to the receive-clock pin. If the receive-clock signal is removed or held in a steady state, the data in the status register will no longer get updated. During this time, however, read and write operations will all continue to operate normally. The easiest method to determine if the signal present on the receive-clock pin is changing is to read the bit-count registers. If the bit count remains the same with each consecutive read, there is no signal on the receive-clock pin.Q3. How is the latch-count (LC) bit used to set the time interval for the bit and error counters of the DS21372, DS2172, and DS2174?A3. Both the bit and error counters of the BERT devices contain a second shadow register that is used to latch the current value. When the LC bit is set from 0 to 1, two events occur. First, the current value of the bit and error counters is latched in the shadow registers. Second, the bit and error counters are cleared and will resume operation. The software can then access the shadow registers to read the previous count values. To measure the bit and error counts from time T0 to T1, the following procedure is necessary:At time T0, set the LC bit from 0 to 1. This will clear the bit and error counters and latch the previous count values, which can be discarded. At time T1, set the LC bit from 0 to 1. This will clear the bit and error counters and latch the count values from time T0 to T1, which the software can access. Q4. Why do the DS21372/DS2172 receive synchronizers sometimes lock to patterns other than the transmitted pattern in repetitive-pattern mode?A4. When the DS21372 and DS2172 are used to generate repetitive patterns, the receiver only searches for a repeating pattern of the same length as the pattern being transmitted. It does not verify that the receive pattern exactly matches the transmit pattern. Once the device has received a pattern of equal length, synchronization is declared. The device will then count any deviations in the received pattern as bit errors. A received pattern of all zeros or all ones will cause the device to synchronize no matter which pattern length is being transmitted. Also, any receive pattern length that is an even divisor of the transmit pattern length will cause the device to synchronize. Consider the following examples that meet the criteria above.

After synchronization is established, the software should check the pattern-receive registers to verify that the correct pattern is being received. Also, the receive-all-zeros and receive-all-ones indicators show that the status register can be used for pattern verification. Q5. Why does the DS2174 design kit (DS2174DK) have neither a crystal nor an oscillator?A5. Because we do not know the customer's working frequency domain, no crystal or oscillator is included in the DS2174DK.The DS2174DK does have an on-board selectable oscillator and an on-board selectable analog input for TCLK. The customer can use either a signal generator or an appropriate oscillator for TCLK. 6. HDLC QuestionsQ1. What are the differences between bridge and configuration mode in the HDLC controller?A1. Configuration mode allows only the local bus to control and monitor the chip while the HDLC packet data is transferred through the PCI bus. Data cannot be passed from the local bus to the PCI bus in this mode.Bridge mode allows the host on the PCI bus to access the local bus. The PCI bus is used to control and monitor the chip and transfer the packet data. Data can be mapped from the PCI bus to the local bus. Q2. Does the DS31256 HDLC controller support 8-bit local bus mode?A2. Yes, the 8-bit local bus is available in bridge mode and has two distinct PCI functions.Function 0 Allows read and write operations to the DS31256 registers through the PCI bus using 8- or 16-bit wide access. However, this function does not allow access to the DS31256 registers, which perform read and write operations on the local bus. Function 1 Allows read and write operations from the PCI bus to the local bus. The software must configure the LBW bit in the LBBMC register to define the width of the local bus as 8 or 16 bits wide. Q3. How is the absolute address calculated in the DS31256 HDLC controller?A3. The absolute address, also known as the real address or machine address, is a fixed address in memory. The absolute address is the base address plus the actual address being used by the device. For proper operation, the absolute address must be allocated correctly when configuring the DMA controller in the device. The equation for calculating the absolute address is:Absolute Address = Base Address + Actual Address in UseFor example, consider the DS31256 HDLC envoy controller's receive done queue end address being used by the device. The actual end address is not an absolute address. If the base address is 0x10000000 and the receive done queue end address is 0x400, the calculation is: 0x10009000 + 0x400 * 4, and the absolute address is 0x1000A000. 7. Design Kit QuestionsQ1. How can I get the most updated definition files for the T1E1DK?A1. The definition files are available by request from the Maxim telecommunication applications support group ( telecom.support@maxim-ic.com).Q2. What software is available for Maxim telecommunication design kits?A2. The software used with the Maxim telecommunication design kits is known as ChipView. ChipView is a PC-based demonstration program that is used to interact with Maxim T/E carrier design kits. The program has been written to control all T/E carrier design kits that utilize either a serial or USB port. ChipView has three basic modes of operation: demo mode, register view, and terminal mode.Demo mode provides a high-level user interface for configuring the device registers on the daughter cards using radio buttons and menu selections. The current device status for functions such as LOS, OOF, and AIS is displayed with easy-to-read widgets. This interface is meant to make device configuration as easy as possible. Register view mode provides an intuitive user interface for reading, writing, and viewing the individual device registers on the daughter card. The device registers are displayed by name in an on-screen array, and the values can be changed using the keyboard or mouse. This interface provides complete control of every bit and function of the specific device. Terminal mode provides direct access to the design kit's processor. The list of all recognized commands is listed when the user types "help" or "?" at the command prompt. This mode is for low-level debugging of the daughter card and should be reserved for seasoned users. Q3. What telecommunication device design kits are currently available from Maxim?A3. There are two kinds of telecommunication design kits available from Maxim. The first type is a stand-alone design kit that contains computer-interface circuitry and an evaluation device. The second type is a combination motherboard and daughter card. The motherboard contains the computer-interface circuitry and the daughter card contains the evaluation device. The DK101 mother board is a low-cost version that supports a single daughter card. The DK2000 mother board is a high-performance version that supports multiple daughter cards.The following devices have stand-alone design kits available: DS2149, DS2174, DS21Q50, DS21Q58, DS21Q59, DS26303, DS26324, DS26334, DS26502, DS26503, DS26504, DS26518, DS26519, DS26521, DS26522, DS3100, DS3104, DS3150, DS3153, DS3154, DS3164, DS3174, DS3184, DS32504*, DS32506, DS32508, DS32512, DS3253, DS3254, DS33R11, DS33R41, DS33W41*, DS33X11*, DS33X162*, DS33Z11, DS33Z41, DS33Z44, DS34S104*, DS34S108*, DS34T104*, DS34T108* The following devices have daughter card design kits available: DS21352, DS21354, DS21455, DS21458, DS2148/DS21348, DS2155, DS2156, DS21Q348/DS21448, DS26401, DS26518, DS26519, DS26521, DS26522, DS26524, DS26528, DS3112/DS3150, DS3144/DS3154 Q4. When designing a board with a Maxim telecommunication device, is there any restriction on PCB trace length from the device to the transformer?A4. Application note 3410, "Guidelines for Laying Out T3 and E3 Network Interfaces," explains how to layout the network interfaces for Maxim T1/E1 and T3/E3 products. This application note provides layout considerations, trace-widths calculations, and different scenarios for ease of design. It also describes how to maintain the proper impedances when laying out a circuit board with a T1/E1 or T3/E3 networking interface.8. TDM-over-Packet (TDMoP) QuestionsQ1. What is the difference between VoIP and TDMoIPA1. Both voice-over-IP (VoIP) and TDM-over-IP (TDMoIP) protocols offer a way to transport real-time voice data over IP networks. However, VoIP and TDMoIP are quite different from each other. VoIP was designed to transport voice data as packets over IP networks instead of using the traditional public switch telephone network (PSTN), while TDMoIP was designed to emulate the PSTN over an IP network. Both solutions accomplish the same task, the transmission of voice data, but are implemented in different ways.Because the two protocols are implemented differently, each has different strengths and weaknesses. For example, VoIP uses data compression when transmitting voice data. This includes voice compression as well as silence compression. TDMoIP does not compress voice data at all. So, if you are bandwidth limited, VoIP is the superior choice for this application. Unfortunately, VoIP is a complex protocol that is difficult to integrate with legacy services or connect to legacy PSTN equipment. Upgrading legacy services to a VoIP solution is possible, but it is often costly and time consuming. This is not the case with TDMoIP, for which integration with legacy equipment is straightforward. Unlike VoIP, TDMoIP is compatible with legacy TDM services, protocols, and signaling. Q2. What is the difference between MII and RMII, and how do they relate to products like the DS34T108?A2. Media-independent interface (MII) and reduced media-independent interface (RMII) are the specifications that are used to communicate between an Ethernet PHY and a media access control (MAC) device. IEEE® 802.3 defines MII as a complete interface with 16 pins that has both data and control signals. RMII reduces the pin count from 16 to 8. However, the tradeoffs of using RMII are that the Tx and Rx clock lines are tied together, and the transmission clocks range from 25MHz to 50MHz.Figure 1 shows the connections between the DS34T108 and a generic Ethernet PHY in MII mode. Note that all 16 pins are required when operating in MII mode. The transmit and receive paths are in separate clock domains.  Figure 1. The DS34T108 is connected to an Ethernet PHY in MII mode.

Figure 2 shows the connections between the DS34T108 and a generic Ethernet PHY in RMII mode. Here, the pin count has been reduced to 8 signals with the Tx data and Rx data being transmitted synchronously with respect to a REF_CLK. In this case, the REF_CLK is CLK_TX. Please note there are only two data pins in RMII mode instead of the four data pins used in MII mode. This is done solely by doubling the CLK frequency from 25MHz to 50MHz. The two data bits at 50MHz enable RMII mode to achieve a throughput of 100Mb.  Figure 2. The DS34T108 is connected to an Ethernet PHY in RMII mode.

In RMII mode, collision detection (COL) is not performed by the PHY, while transmit error is eliminated all together. It is assumed that RMII is used only for chip-to-chip communications and you will, therefore, not have a transmit error. However, carrier sense and receive data valid (RX_DV) are multiplexed into the same signal. The DS34T108 device supports both MII and RMII modes of operation. To configure the device in MII mode, simply select bits [15:14] of the General_cfg_reg0 (0x0000000) to 00b; when selecting RMII mode, change these same bits to 01b. No other operation is required. Any other configuration for the PHY must be done externally. Q3. What is a bundle in TDMoIP products?A3. A bundle is defined as a stream of bits that have originated from the same physical interface and are transmitted from a TDMoIP source device to a TDMoIP destination device. For example, bundles may be composed of any number of 64kbps timeslots originating from a single T1/E1 or an entire T3/E3. Bundles are single-direction streams, frequently coupled with bundles in the opposite direction to enable full-duplex communications. More than one bundle can be transmitted between two TDMoIP edge devices. Sometimes, a bundle can be called a pseudowire.Q4. I am getting bit errors with the DS34T108 in E1 internal mode when I use all 8 ports. All other modes operate correctly. What is the cause of these errors, and is there a solution?A4. The A1 version of the DS34T108 does have issues when transmitting data on all 8 ports in E1 mode. The problem has to do with the internal TDM framer of the device—there is a bandwidth issue with the internal synchronizer. An oscillator that is specific to the framer is used to drive a state machine that checks each port to see if there is data ready to be processed. When using all 8 ports, this oscillator is a little slower than required in E1 mode. However, T1 does not have an issue, as its fundamental frequency is 1.544MHz, as opposed to 2.048MHz in E1 mode.Fortunately, there is a test mode that increases the frequency of the internal oscillator to a value that can handle the bandwidth for all 8 ports in E1 mode. Simply write a value of 0x71 to the register offset 0x109100 in the internal framer. This value will not need to be written to this location for subsequent revisions of the DS34T108. Q5. What kind of OAM packets are supported by TDMoP product support?A5. OAM (operations, administration, and maintenance) is a general term used to describe the processes, activities, tools, standards, etc. involved with operating, administering, and maintaining any system.Maxim TDMoP products support the following three types of OAM packets:

Q6. What is ARP and how does it work on Maxim TDMoP devices?A6. The ARP (address resolution protocol) is a protocol used by the Internet Protocol (IP), specifically IPv4, to map IP network addresses to the hardware addresses (Ethernet MAC address) used by a data link protocol. In other words, ARP provides a dynamic mapping from an IP address to the corresponding hardware address.

Hardware Type: Specifies a hardware interface type (e.g., Ethernet) for which the sender requires a response. Protocol Type: Specifies the type of network-level protocol address (e.g., IP) the sender has supplied. Hardware Size: The size in bytes of the hardware address. For Ethernet, it is 6. Protocol Size: The size in bytes of the protocol address. For IP, it is 4. Operation: What kind of operation is the message for? ARP request: 1, ARP reply: 2. Sender Hardware Address: The size in bytes of the sender's hardware address. For Ethernet, it is 6. Sender IP: The size in bytes of the sender's IP address. It is 4. Target Hardware Address: The size in bytes of the target's hardware address. For Ethernet, it is 6. Target IP: The size in bytes of the target's IP address. It is 4. In Maxim TDMoP devices, for an ARP request, all the fields are filled in except the target hardware address. When a system receives an ARP request, it fills in its hardware address, swaps the two sender addresses with the two target addresses, sets the 'operation' field to 2, and sends the reply. Q7. What are the ground considerations when using an Ethernet PHY interface?A7. With any electrical system, choosing the appropriate grounding scheme is crucial for proper operation. There are three main types of electrical grounds: earth ground, signal ground, and chassis ground. Although similar in function, each of the grounds is used differently. Secondly, the grounds may also be at a different electrical potential with respect to each other.There are several reasons why a designer may choose to have more than one ground in a particular design. The main reasons deal with noise reduction and signal isolation. When using an Ethernet PHY, it is important to isolate the signals from the CAT-5 Ethernet cable to the reset of the system. This is done by using specialized Ethernet magnetics with each side of the transformer referenced to the appropriate ground. Please notice the two separate grounds in Figure 3.  Figure 3. Typical Ethernet PHY connection. Q8. Can you define the Stratum levels for TDMoP devices?A8. A Stratum 1 clock is defined as a completely autonomous source of timing, which has no other input other than, perhaps, a yearly calibration. It has an accuracy of 1.0 × 10-11. A Stratum 1 clock may control Stratum 2, 3E, 3, 4E, or 4 clocks. A Stratum 2 clock may drive Stratum 2, 3E, 3, 4E, or 4 clocks. A Stratum 3E clock may drive Stratum 3E, 3, 4E, or 4 clocks.Stratum 2 tracks an input under normal operating conditions, and holds to the last best estimate of the input reference frequency during impaired operating conditions. It has an accuracy of 1.6 × 10-8. Stratum 3 is defined as a clock system that tracks an input as in Stratum 2, but over a wider range. It has an accuracy of 4.6 × 10-6. A Stratum 3 clock may drive Stratum 3 or 4 clocks. A Stratum 4 clock is not recommended as a source of timing for any other clock system. Stratum 3E is a relative new standard created as a result of SONET equipment requirements. It has an accuracy of 1.0 × 10-6. Stratum 4 is defined as a clock system that tracks an input as in Stratum 2 or 3. It has an accuracy of 3.2 × 10-5. Q9. What is the difference between TIE and MTIE?A9. TIE, short for time interval error, is defined as the phase difference between a measured clock edge and the ideal clock edge locations. These values are typically measured in nanoseconds. When plotted over a given amount of time, the TIE values can show how a given signal can shift in both phase and frequency to an ideal reference, as shown in Figures 4 and 5. Figure 4. TIE measurement against an ideal source.  Figure 5. Typical TIE plotted over time. MTIE stands for maximum time interval error. This is a positive number that shows a maximum value of wander for a particular signal over a given amount of time. This value is useful when graphed, and may be plotted on a logarithmic scale over time. The plot in Figure 6 can provide insight as to how a particular signal will behave. MTIE plots often have to fit in a specific mask to meet certain specifications, depending on the application.  Figure 6. Typical MTIE graph with an MTIE mask. Q10. How can the user send OAM packets using the DS34T108?A10. OAM (operations, administration, and maintenance) is a general term used to describe the processes, activities, tools, standards, etc. involved with operation, administration, and maintenance of any system.PING and ARP are two examples of OAM packets. The main CPU is responsible for building the OAM packets and then passing them to the DS34T108. The DS34T108 will subsequently send these OAM packets to the Ethernet interface. The HAL driver for the DS34T108 provides an API interface to send OAM packets. The method for this API in 'AsicHal' class is: SendPacket(byte * i_PktHandle, byte *i_PktBuffer, word i_PktLen, byte *i_SendParams)where: i_PktHandle 0 i_PktBuffer A pointer to the OAM packet that needs to be built before a call is made to this method i_PktLen Size in bytes of the OAM packet i_SendParams Miscellaneous parameters that also needed to be filled beforePlease see the SendArpReq method in 'OampTask' class for some examples. Q11. How do you find the correct jitter buffer index for a bundle in Maxim TDMoP devices?A11. The jitter buffer index is the concatenation of the TDM interface number (3 MSB, 0 to 7) and the number of the lowest timeslot in the bundle. The lowest timeslot can be found in the bits[4:0] of bank 1 or 2 per the timeslot assignment map (offset 0x18000 or 0x18200).For example, if the bundle consists of timeslots (base 0) 10, 14, and 17 on the port 4, then the Jitter_buffer_index is 100_01010[bin], i.e., 0x8A. So, the correct Status_and_level registers of the jitter buffer controller with an offset set at 0x30000 will be: 0x30000 + (0x8A * 8) = 0x30450The reason for multiplying by 8 is because every timeslot takes two 4-byte registers (Status_and_level register and Min_and_max_levels register). IEEE is a registered service mark of the Institute of Electrical and Electronics Engineers. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Maxim® Telecommunications

相关推荐

MAXIM芯片的小功率电源解析

本帖最后由 wangka 于 2011-9-22 16:02 编辑

资料里提到了3款MAXIM的芯片,很详细的教你计算电路参数,讲解电路原理。这个我喜欢,拿来和大家分享一下。

2011-09-22 16:01:46

Maxim Deep cover NFC产品的SHA-256算法是什么?

物联网技术从最开始的概念性技术,如今已经在日常生活中被广泛应用,如电表预付费、智能门禁管理等。Maxim对加密产品的研究拥有超过20年的历史经验,本文主要介绍了Maxim Deep cover NFC产品的加密算法、安全器件认证和产品应用案例等。

2019-08-28 07:57:22

Maxim Integrated 2012新品牌全球发布 宣告模拟整合时代到来

【10月9日消息】高集成度模拟与混合信号半导体厂商Maxim Integrated Products,Inc.(NASDAQ)在京召开2012新品牌新闻发布会,正式发布Maxim新品牌形象及相关

2013-07-11 15:46:55

Maxim Integrated 2012新品牌全球发布 宣告模拟整合时代到来

【10月9日消息】高集成度模拟与混合信号半导体厂商Maxim Integrated Products,Inc.(NASDAQ)在京召开2012新品牌新闻发布会,正式发布Maxim新品牌形象及相关策略

2013-07-11 11:18:45

Maxim TD-SCDMA参考设计

This application note presents Maxim's TD-SCDMA reference design V1.0. TDSCDMAis the Chinese Third

2009-10-19 15:27:34

Maxim公司的SPICE在哪?

正在做毕业设计,但是发现需要Maxim公司的MAX652和MAX1771,悲剧的是Multisim里没有,所以想自己做一个,不需要封装只要仿真就好,上官网一查发现没有SPICE,我该怎么办。。。。到哪能下到啊就是那个模拟程序,求大神解惑啊{:4:}

2014-01-21 15:14:19

Maxim安全RFID方案,内置13.56MHz接口,支持全球范围的门禁控制

Maxim安全RFID方案,内置13.56MHz接口,支持全球范围的门禁控制、e-cash和ID卡应用。 Maxim Integrated Products, Inc.(NASDAQ:MXIM

2011-09-22 15:48:13

Maxim推出环境光传感器

Maxim Integrated Products, Inc.推出Santa Cruz (MAXREFDES23#)环境光传感器(ALS),能够在工厂快速配置和监测多路红、绿、蓝(RGB)可见光和红外(IR)信号环境光传感器,适用于需要高精度检测的工业应用。

2020-05-06 06:55:04

AD5504为什么无法正确写入DAC input reg?

根据AD5504的数据手册,要向其寄存器写入数据应按照以下4种流程进行:

1、写control reg --> nop写

2、写control reg --> 写

2023-12-20 08:10:51

AD5504无法正确写入DAC input reg

根据AD5504的数据手册,要向其寄存器写入数据应按照以下4种流程进行:1、写control reg --> nop写2、写control reg --> 写DAC input reg

2019-02-28 12:21:44

ADI,NS,MAXIM,TI销售问题

为啥我的销售额上不去呢,求高手赐教。我公司现货原装销售ADI,NS,MAXIM,TI等品牌的IC销售,货源不错,价格库存不错,为啥我的销售额就不行呢。求赐教,有需求也可以联系我。Q:2431493867

2012-04-28 14:16:21

DMA filterblock控制reg问题

( FILT_DONE_DMA_LO_TD[0], LO16((uint32)Filter_1_HOLDA_PTR), LO16((uint32)CTRL_REG

2019-05-31 14:13:59

EFUSE_RD_REPEAT_ERR4_REG的正确地址是什么?

好像是不同ESP-*芯片的EFUSE_RD_REPEAT_ERR4_REG地址有些不一致。例如,对于 ESP32-S3,TRM 将 EFUSE_RD_REPEAT_ERR4_REG 列为寄存器摘要表

2023-04-11 06:55:26

FPGA实战演练逻辑篇53:reg2reg路径的时序分析

reg2reg路径的时序分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 我们可以先重点研究一下

2015-07-24 12:03:37

FilmDoctor®材料表面仿真软件

FilmDoctor®材料表面仿真软件,可用于结构表面的物理特性描述、工程分析和优化设计。 FilmDoctor®的显著特点l通过物理建模和仿真对材料表面进行工程分析

2011-07-21 11:51:30

wire 与 reg 区别

- 如果要综合寄存器,需要同时满足俩个条件:1。定义为reg,2. 在always @posedge(negedge) block中赋值- 如果要综合组合逻辑,可以(任意)a. 定义为wire, 用

2014-02-20 10:51:18

【技巧分享】在设计文件中,如何确定信号是reg型还是wire型?

当我们使用Verilog时,对于信号定义为reg型还是wire型比较混乱,那么今天我们就来讲一讲如何快速的进行信号定义。在Verilog中,wire永远是wire,就是相当于一条连线,用来连接

2020-03-01 23:58:14

为什么STM32F103 LL库清除某个标志位都是使用WRITE_REG(REG, VAL)呢?

大佬们,最近看LL库比较贴合寄存器编程,但是LL库清除某个标志位都是通过WRITE_REG(REG, VAL)这个来写整个寄存器,不应该通过CLEAR_BIT(REG, BIT)来实现清除某个位么,比如这个

2024-03-18 06:10:51

为什么STM32F103 LL库清除某个标志位都是通过WRITE_REG(REG, VAL)来实现的?

大佬们,最近看LL库比较贴合寄存器编程,但是LL库清除某个标志位都是通过WRITE_REG(REG, VAL)这个来写整个寄存器,不应该通过CLEAR_BIT(REG, BIT)来实现清除某个位么,比如这个

2023-08-07 07:59:57

为什么我不能使用reg变量来指示总线位?

我有一个设计,我想使用一个reg变量控制另一个总线位如:reg [2:0] a; reg [7:0] b; reg c; reg [2:0] d; case 1:c案例2:d似乎案例1是可行的但

2019-03-15 13:23:10

单片机里面的reg51和reg52的区别是什么

单片机里面的reg51、reg52区别为:获取变量地址不同、寄存器地址不同、扩展不同。一、获取变量地址不同1、reg51:reg51声明变量后,不能用取地址运算符&获取其地址, 编译无法通过

2021-12-02 07:06:09

如何实现Reg istered SDRAM接口电路的设计?

如何实现Reg istered SDRAM接口电路的设计?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口电路的原理设计与布局布线规则是什么?

2021-04-12 07:10:21

如何识别美信maxim假货

精密的,像把SIPEX的打成MAXIM的MARK,就很难检测出来。现在很大打磨过的表面,他们又加了一层涂料,看起来就没有打磨的痕迹了,而且有原装IC表面的浮点。但是这样的货用小刀刮一下就掉出来了。有

2011-09-22 15:07:08

怎么结合两个8bit reg

Hai,在这个代码中,我想组合两个8位reg并形成一个16位结果无符号char data1,data2,data3,d0,d1;uint16_t a0,a1,x,y,d2,d3,z;d0=data1;//Mo.data reg data1=data2;我的代码有错误吗?让我知道…

2020-03-30 07:06:18

请问Proteus仿真时出现一个没有 MAXIM.DLL,是什么情况?

本帖最后由 一只耳朵怪 于 2018-5-25 09:09 编辑

Proteus仿真时出现一个没有 MAXIM.DLL,是什么情况?

2018-05-24 21:37:06

(好东西)Maxim热管理手册

Maxim的热管理手册介绍了温度检测和风扇控制的基本概念,以及相关电路的设计和应用。探讨了热敏电阻、热电偶、RTD和各种温度传感器IC (本地温度传感器、远端温度传感器、模拟温度传感器、数字温度

2011-09-22 14:14:36

REG71050 pdf datasheet (降压/升压充

The REG710 is a switched capacitor voltage converterthat produces a regulated, low-ripple output

2008-08-08 00:12:45 19

19

19

19基于1-Wire®的PnP设备识别

文章讨论了一种“即插即用”(PnP)设备的识别方法。该方法采用1-Wire® 器件作为存储器存储识别信息,并已在Dallas公司的TINI®板得到了实际的应用。目前,“即插即用”

2009-08-17 11:27:08 10

10

10

10DLP® Pico Projector Develo

DLP® Pico Projector Development Kit V2 :

1 Purpose 11 About This Manual 12 Related Documentation From Texas Instruments 2 T

2010-06-01 09:18:55 18

18

18

18Polycom® Communicator C10

非常感谢您选择Polycom® Communicator C100S。

将Polycom® Communicator C100S连接到您的计算机上的USB端口后,您可以使用自己的Skype™帐户通过因特网进行全双工、双向通话。

2010-06-29 16:14:22 39

39

39

39车用DirectFET®2 功率MOSFET

国际整流器公司针对开关应用,推出两款具有低栅级电荷的车用 DirectFET®2 功率 MOSFET ,这些开关应用包括开关电源 (SMPS) 、D 类音频系统、高强度气体放电灯 (HID) 照明,以及其

2010-09-09 10:36:50 19

19

19

19REG71055,pdf(60mA, 5.0V, Buck/

The REG710 is a switched capacitor voltage converterthat produces a regulated, low-ripple output

2010-10-06 19:58:02 4

4

4

4REG710-5,pdf(60mA, 5.0V, Buck/

The REG710 is a switched capacitor voltage converterthat produces a regulated, low-ripple output

2010-10-06 20:02:57 9

9

9

9REG710-3,pdf(60mA, 5.0V, Buck/

The REG710 is a switched capacitor voltage converterthat produces a regulated, low-ripple output

2010-10-06 20:13:56 17

17

17

17REG711-5,REG711-3,pdf(50mA Swi

The REG711 is a switched capacitor voltage converter, which produces a regulated, low ripple output

2010-10-06 21:15:14 14

14

14

14REG711-33,REG711-27,REG711-25,

The REG711 is a switched capacitor voltage converter, which produces a regulated, low ripple output

2010-10-06 21:16:16 16

16

16

16REG71055-Q1,pdf(30-mA 5-V Buck

The REG71055 is a switched capacitor voltage converter that produces a regulated, low-ripple output

2010-10-06 21:20:44 21

21

21

21REG1118,pdf(800mA Low Dropout

The REG1118-2.85 is a three-terminal voltage regula-tors capable of sourcing up to 800mA

2010-10-19 20:20:49 17

17

17

17PresencePLUS®视觉传感器

基本套装包含传感器和匹配的支架。完整套装还有镜头、光源、QD线缆和可选配的监视器。

PresencePLUS®P4GEO套装型号说明

2010-12-29 21:34:24 13

13

13

13安全的用户认证与网络微控制器-Secure User Aut

and explains its use in secure user-authentication applications. It introduces the NTLM library available for use with the Maxim®; network microco

2009-04-23 17:47:09 717

717

717

717Maxim USB库

摘要:Maxim USB库是使用ARM7™处理器并基于MAX3421E/MAX3420E提供的软件例程。本应用笔记对系统及其软件运行进行了说明,在同一ARM® C语言代码中同时实现了USB主机和外设功能。这

2009-04-24 17:32:59 1184

1184

1184

1184

Maxim Digital Monetary Certifi

in iButton® data carriers (tokens). The document defines a digital certificate called a "Maxim Digital Monetary Certificate" (a.k.a., "eCertific

2009-05-08 11:33:10 853

853

853

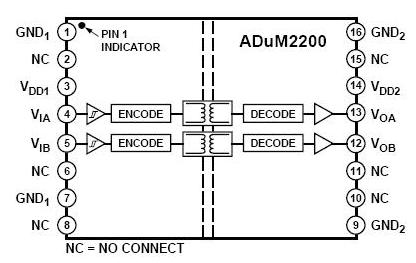

853ADuM220x ADI公司iCoupler®技术的

ADuM220x ADI公司iCoupler®技术的双通道数位隔离器

ADuM220x 是ADI公司iCoupler®

2009-07-01 08:38:06 848

848

848

848

OneWireViewer和iButton®快速使用

OneWireViewer和iButton®快速使用指南

Abstract: This application note is a Quick Start Guide.

2009-07-25 21:09:46 1663

1663

1663

1663

Understanding the ATE SPI (Ser

Understanding the ATE SPI (Serial Peripheral Interface)

Abstract: Most Maxim®; ATE

2009-10-02 21:45:49 1370

1370

1370

1370

理解ATE SPI (串行外设接口)

理解ATE SPI (串行外设接口)

大多数Maxim®; ATE设计都采用了一个串行接口,以便从外部控制器件。这种串行接口正在成为一种重要且非常有用的功能

2010-01-26 16:34:59 2382

2382

2382

2382

Maxim推出带失效保护的PROFIBUS-DP/RS-48

Maxim推出带失效保护的PROFIBUS-DP/RS-485收发器

Maxim推出PROFIBUS-DP®/RS-485收发器MAX14770E。该器件采用Maxim的下一代BiCMOS工艺,能够实现较快的(20Mbps)数据传输速度,并且在

2010-02-11 10:17:12 670

670

670

670Bluetooth to 1-Wire communicat

how to enable communication between a Bluetooth® serial and Maxim®; 1-Wire adapters. Topics discussed are: selectin

2010-02-27 17:29:51 1177

1177

1177

1177

全新英特尔® 至强® 处理器为主流用户带来关

全新英特尔® 至强® 处理器为主流用户带来关键任务应用平台

英特尔最快的企业级和高性能计算用处理器提供平均高达3倍的性能提升,集成

2010-04-01 09:28:28 477

477

477

477REG711-5 50mA 开关电容 DC/DC 转换器

电子发烧友网为你提供TI(ti)REG711-5相关产品参数、数据手册,更有REG711-5的引脚图、接线图、封装手册、中文资料、英文资料,REG711-5真值表,REG711-5管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 16:31:48

REG711-25 50mA 开关电容 DC/DC 转换器

电子发烧友网为你提供TI(ti)REG711-25相关产品参数、数据手册,更有REG711-25的引脚图、接线图、封装手册、中文资料、英文资料,REG711-25真值表,REG711-25管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 16:31:48

REG711-33 50mA 开关电容 DC/DC 转换器

电子发烧友网为你提供TI(ti)REG711-33相关产品参数、数据手册,更有REG711-33的引脚图、接线图、封装手册、中文资料、英文资料,REG711-33真值表,REG711-33管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 16:31:48

REG711-3 50mA 开关电容 DC/DC 转换器

电子发烧友网为你提供TI(ti)REG711-3相关产品参数、数据手册,更有REG711-3的引脚图、接线图、封装手册、中文资料、英文资料,REG711-3真值表,REG711-3管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 16:31:48

单片机C语言编程的头文件reg51.h和reg52.h的详细资料解析

我们在用c语言编程是往往第一行就是reg51.h或者其他的自定义头文件,我们怎么样来理解呢?

2019-07-24 17:37:00 2

2

2

2比较Verilog中Wire和Reg的不同之处

wire 和reg是Verilog程序里的常见的两种变量类型,他们都是构成verilog程序逻辑最基本的元素。正确掌握两者的使用方法是写好verilog程序的前提。

2020-03-08 17:18:00 11418

11418

11418

11418不同情况下,在Verilog中什么时候用wire,什么时候用reg

在Verilog中何时用wire,何时用reg? Verilog HDL中的变量可以定义为wire型和reg型,这两种类型的变量在定义时要设置位宽,缺省为1位,变量的每一位可以取0、1、x、z,其中

2020-09-28 11:26:13 12197

12197

12197

12197

单片机里面的reg51、reg52区别

单片机里面的reg51、reg52区别为:获取变量地址不同、寄存器地址不同、扩展不同。一、获取变量地址不同1、reg51:reg51声明变量后,不能用取地址运算符&获取其地址, 编译

2021-11-23 17:06:37 13

13

13

13reg与wire的区别

1,reg与wire的区别: 相同点: 都能表示一种类型类型。 不同点: wire 连线型数据,线网类型; 表示元件间的物理连线,不能保存数据; 线网是被驱动的,可以用连续赋值语句或把元件的输出连接

2022-07-03 10:00:28 10937

10937

10937

10937FPGA跨异步时钟ASYNC_REG和XPM_CDC处理

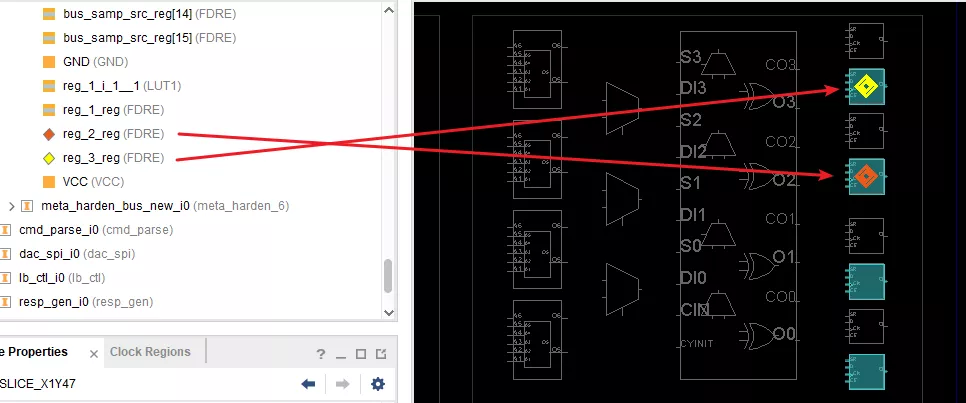

reg_2和reg_3应该放到同一个Slice中,但综合工具并不是那么智能,有时并不会综合到同一个Slice中,这时就需要我们添加ASYNC_REG的属性。

2022-08-02 08:59:41 2211

2211

2211

2211

ERM和LRA触觉参考设计 具有Bluetooth reg低能耗远程

电子发烧友网站提供《ERM和LRA触觉参考设计 具有Bluetooth reg低能耗远程.zip》资料免费下载

2022-09-08 10:26:21 1

1

1

1UART至Bluetooth reg低能耗(BLE)桥参考设计

电子发烧友网站提供《UART至Bluetooth reg低能耗(BLE)桥参考设计.zip》资料免费下载

2022-09-08 10:15:57 2

2

2

2systemverilog:logic比reg更有优势?

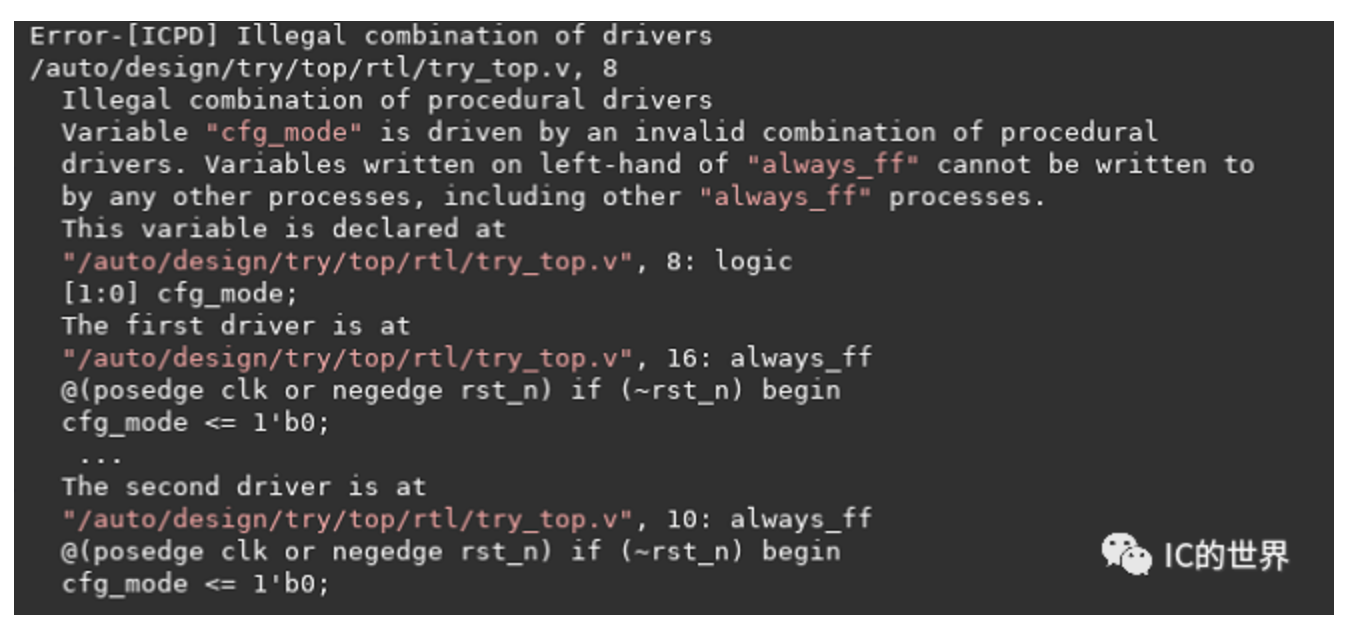

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-09-28 17:34:37 1928

1928

1928

1928

systemverilog:logic比reg更有优势

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-10-26 09:32:24 325

325

325

325

电子发烧友App

电子发烧友App

评论