摘要:本应用笔记对两种模拟IC中常用的串行、数字接口(SPI™或3线、I²C或2线)进行了比较,每种接口在不同的设计中都表现出其优点和缺点,具体取决于数据速率、可提供的设计空间以及噪声环境等。本应用笔记给出了两种接口的区别,并举例详细说明了这些观点。

3线接口可以以更高的时钟频率工作,并且不需要上拉电阻。SPI/QSPI和MICROWIRE接口都可以工作在全双工模式(数据可以在同一时间发送和接收),一般在嘈杂环境下工作不成问题。3线接口是边沿触发,不是电平触发,因此具有更强的抗干扰能力。

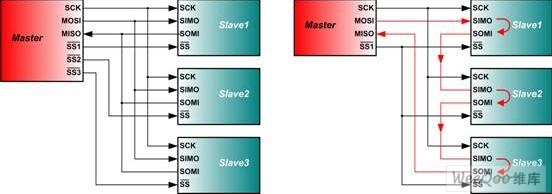

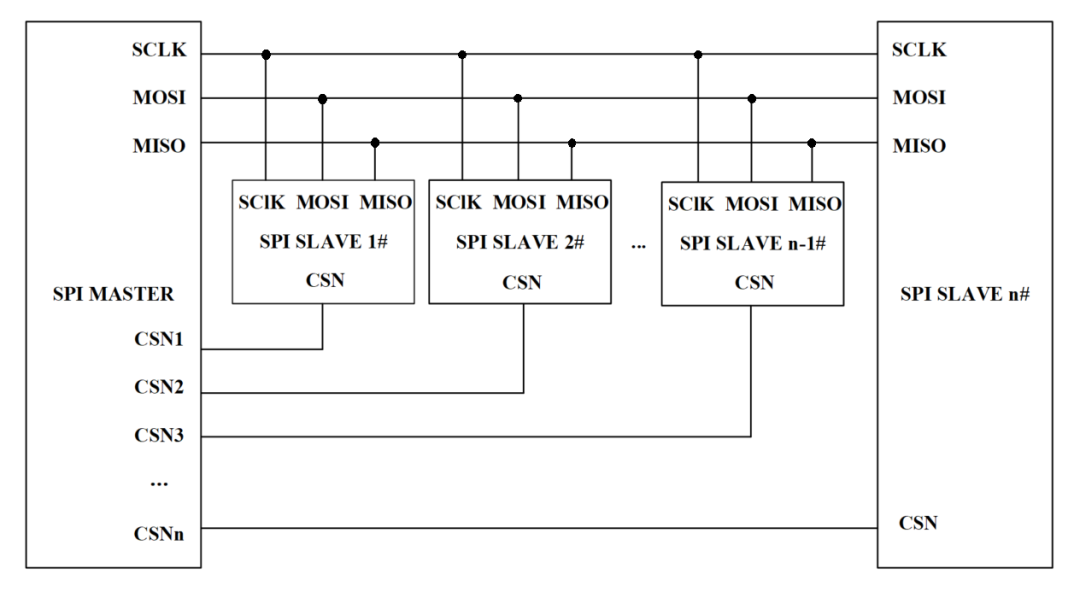

3线接口的主要缺点是它要为每一个从机提供一条低电平有效的CS线,除非将从机用菊链形式连接,如图1所示(后续章节将详细讨论菊链方式)。另外一个缺点是3线接口没有应答机制去判断数据的收发是否正确。从软件设计看,在单主机/单从机应用中,3线接口比2线接口简单,效率更高。

图1. 利用数据输入、数据输出、时钟和片选信号进行通信的3线接口。

表1. 3/2线接口优缺点的对比

主机和从机经由多条总线通过串行接口进行通讯。在写周期,主机使用自己产生的时钟和数据将数据传至从机。在读周期,从机传输数据至主机。

大多数的SPI接口有两位配置位,时钟极性(CPOL)和时钟相位(CPHA)用于设定从机何时采集数据。CPOL决定SCLK为高时总线空闲(CPOL = 1)还是SCLK为低时总线空闲(CPOL = 0)。CPHA决定在SCLK的哪一个边沿将数据移入、移出。当CPOL = 0时,将CPHA设为0,表示在SCLK的上升沿将数据移入从机;将CPHA设为1,表示在SCLK的下降沿将数据移入从机。CPOL和CPHA的两个状态允许四种时钟极性和相位的不同组合。每一种都与其它三种不兼容。为了实现主、从机间的通讯,主、从机的CPOL和CPHA必须有相同的设置。

在SPI接口的大多数应用中,SPI接口一次传送8位数据(一个字节),有一些微处理器一次传送两个或多个字节。例如,MAXQ2000微处理器可一次传送8位或16位数据。当CPOL = 0、CPHA = 0,低电平有效CS由高跳变为低,开始一个主机到从机的传输过程。在SCLK信号高低变化的八个周期内,低电平有效CS信号必须保持为低。DIN数据锁定在SCLK信号的上升沿。在同样的8位周期内,DOUT线上的从机输出数据在SCLK的每个下降沿有效。图2a给出了CPHA = 1时的详细时序;图2b给出了CPHA = 0时的详细时序。

图2a. 3线接口时序(CPHA = 1),CPHA = 1、CPOL = 1时,3线接口在时钟的上升沿将数据移入外设,在时钟的下降沿将数据移出外设。

图2b. 3线接口时序(CPHA = 0),CHPA = 0、CPOL = 1时,3线接口在时钟的下降沿将数据移入外设,在时钟的上升沿将数据移出外设。

因为总线上的每一个IC需要专属的片选线,所以低电平有效CS被用做每个从机的使能信号。如果一条总线上有四个从机,则需要四条片选线。如果从机的低电平有效CS为高电平(禁止),该从机就忽略SCLK线上的数据,将DOUT置为高阻。

部分3线接口设备可以链接成菊链的方式,而不需要为每个从机提供低电平有效的CS线,菊链方式能够用一条低电平有效的CS线和一条数据线控制多个串联从机。在菊链结构中3线接口必须包含DOUT线,如图1所示,从机#1的DOUT连接到从机#2的DIN,如此反复。

SPI标准中没有定义最大数据速率。外部设备定义了自己的最大数据速率,通常为MHz量级。微处理器可以适应很宽范围的SPI数据速率。在利用SPI接口进行通讯时,从机无法降低主机的数据速率或确定一个适当的速率。

QSPI标准和SPI标准非常相似。事实上,外设无法区分QSPI总线和SPI总线。与SPI标准中的主机不同,QSPI中的主机允许数据通过可编程的片选线传输数据。QSPI的主机甚至可以传送长度在8位和16位之间的数据,而SPI的主机只可以传送8位的数据。可以配置QSPI的设备去连续传送长度超过16字节的数据(最大为256位)。这种传输完全由QSPI设备的配置来实现,不需要MCU的操作。与SPI接口相似,QSPI接口也没有规定最大数据速率。

由National Semiconductor公司制定的老的MICROWIRE标准和SPI标准非常相似。不同的是MICROWIRE标准的时钟极性和时钟相位是固定的(CPOL = 0和CPHA = 0)。DIN的数据读取总是锁定在SCLK的上升沿。DOUT的数据输出总是在SCLK的下降沿。MICROWIRE标准没有规定最大数据速率。

图3. 利用数据输入/输出和时钟信号进行通信的2线接口。

当SCL为高,SDA从高变为低,即发出了一个开始命令,启动I²C通信。图4a所示,每个SCL时钟传输一个数据位,传输一个字节至少需要9个数据位。一个写周期包括8个数据位和一个应答位(ACK)或者非应答位(NACK)。如图4b所示,当数据在I²C总线上传输时,在SLK的上升沿写入从机,在SLK的下降沿从机输出。在SCL时钟周期为高电平的时间内,SDA线的数据不可以改变。一次传输的完成必须跟随着一个中止或重新开始的命令,既SCL为高时,SDA由低变为高。当总线空闲时,SDA和SCL都为高。

图4a. 开始条件和停止条件,2线接口采用开始、重复开始和停止命令在主机和从机之间传输数据。

图4b. I²C应答位,应答数据时,2线接口将SDA拉低。

I²C的写周期起始于开始命令,随后是7位从机地址和第8位用于标识读、写操作。将第8位置低,表示写操作;将第8位置高,表示读操作。主机在第8个时钟周期后释放总线。如果从机应答数据传输,则在第9个时钟周期将SDA拉低。如果从机不应答写命令,则释放SDA (该数据线通过上拉电阻置于高电平)。

随后,主机写入8位命令字节,然后是第二个ACK/NACK位。接下来,主机写入8位数据字节并跟随第三个ACK/NACK位。数据字节和最后的应答位完成一个读/写周期,更新外设输出,图5a是一个写周期的详细例子。

I²C读周期起始于开始命令,随后是需要写入数据的从机地址、第8位置高,表示读操作。在ACK/NACK之后,主机写入命令字节访问从机寄存器。在第二个ACK/NACK位后,主机重新写入从机地址。在第三个ACK/NACK位后,从机控制总线,一次输出8位数据到总线上。如图5b所示,当从与上次读操作相同的从机寄存器读取数据时,主机只需要在读取从机数据之前写入从机地址。

图5. 2线接口一次传输8位数据,图5a是I²C写周期的一个例子;图5b是I²C读周期的一个例子。

I²C接口支持低速(大于100kHz)、快速(大于400kHz)和高速(大于3.4MHz)三种数据速率。I²C接口的高低电平为CMOS逻辑电平(低电平为0.3x电源电压以下,高电平为0.7x电源电压以上)。

I²C接口和SMBus接口的最主要区别是最高/最低时钟速率,因为I²C总线为被动传输总线,不存在总线超时问题,速率可低至“静止”。SMBus接口则存在总线超时问题。如果时钟信号拉低之后的时间大于超时周期(最长为35ms)时,从机复位接口,认为发生总线超时。SMBus的超时周期限制了时钟的最小速率为19kHz。为了保证正常通信,SMBCLK的速率必须介于10kHz至100kHz之间,而I²C接口的主机或从机则可根据传输数据的需要将时钟保持在低电平。

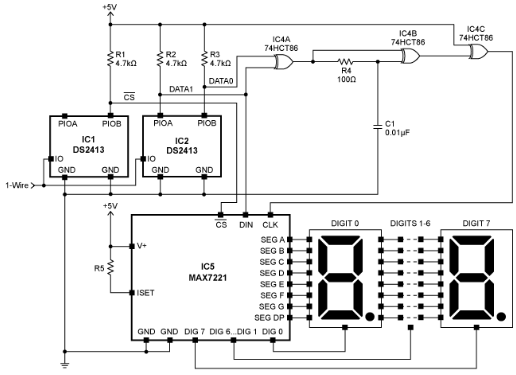

如图6所示,通过2线接口连接微处理器和8位数/模转换器(MAX5115)。因为这个DAC有四个地址选择引脚,可以产生16个唯一的从机地址,因此可以在总线上并联16个DAC,因为MAX6641有不同的从机地址,同样的2线接口也可以设置SMBus温度传感器/风扇控制器(MAX6641),风扇控制器控制MOSFET的栅极,使其打开或关闭风扇。

图6. 由于微控制器采用的是I²C接口,与外设通信时,如DAC、温度传感器,总线只需要两条连线。

3线接口需要单独的片选线实现微处理器与多个并行从机之间的通信,更简单的2线接口用一条时钟线和一条数据线与总线上的每个设备通信。可以通过设定不同的从机地址在总线上挂接多个IC。大多数I²C接口外设具备地址选择引脚,以实现从机地址的配置。外设可以使用的从地址数等于地址选择引脚数的平方。例如,若外有两个地址选择引脚,它就可以配置四个不同的地址。

新一代设计以更少的地址选择引脚提供更多的从地址。MAX7319是输入/输出扩展芯片,可以从两个地址选择引脚(AD2和AD0)扩展出16个从地址。这些引脚可以接GND、电源(VCC)、SDA或SCL。表2列出了这16个从地址的详细信息,A6、A5、A4固定为110,A3至A0可以通过AD2、AD0设置。

表2. MAX7319仅利用2个地址线(AD2和AD0)即可编译出16个不同地址

3线接口和2线接口将并存,但I²C接口似乎占有更大的市场份额,大部分微处理器支持2线接口。I²C接口的易用性及更少的连线使其增长量超过了SPI接口。

引言

虽然现实世界中的信号都是模拟信号,但是现在越来越多的模拟IC采用数字接口进行通信。串行接口的数据通信介于主机(提供串行时钟)和从机/外设之间。目前,大多数微控制器提供SPI (3线)和I²C (2线)接口,用于发送、接收数据。微处理器通过几条总线控制周边的设备,比如:模/数转换器(ADC)、数/模转换器(DAC)、智能电池、端口扩展、EEPROM以及温度传感器。与通过并口传输数据不同的是:串行接口通过2条、3条或4条数据/时钟总线连续传输数据。虽然并行接口具有传输速度快的特点,但是串行接口占用较少的控制和数据线。串行接口的基础知识

串行接口有三种:3线、2线和单线。本文主要讨论3线和2线串行接口。串行外设接口(SPI)、队列串行外设接口(QSPI™)和MICROWIRE™ (或MICROWIRE PLUS™)接口标准均采用3线接口。芯片间总线(I²C)和系统管理总线(SMBus™)均为2线接口。这些串行接口拥有各自的优点和缺点,如表1所示。3线接口

3线接口使用片选线(低电平有效CS或SS)、时钟线(SCLK)和数据输入/主机输出线(DIN或MOSI)。3线接口有时也包括一条数据输出/主机输入线(DOUT或MISO),这时也叫做4线接口。为了叙述的简便,本文将3线接口和4线接口统称为3线接口。3线接口可以以更高的时钟频率工作,并且不需要上拉电阻。SPI/QSPI和MICROWIRE接口都可以工作在全双工模式(数据可以在同一时间发送和接收),一般在嘈杂环境下工作不成问题。3线接口是边沿触发,不是电平触发,因此具有更强的抗干扰能力。

3线接口的主要缺点是它要为每一个从机提供一条低电平有效的CS线,除非将从机用菊链形式连接,如图1所示(后续章节将详细讨论菊链方式)。另外一个缺点是3线接口没有应答机制去判断数据的收发是否正确。从软件设计看,在单主机/单从机应用中,3线接口比2线接口简单,效率更高。

图1. 利用数据输入、数据输出、时钟和片选信号进行通信的3线接口。

2线接口

2线接口包括一条数据线(SDA或SMBDATA)和一条时钟线(SCL或SMBCLK)。2线接口的优点是使用更少的连线,这一点对于结构紧凑的设计尤为重要,比如:手机、光纤的应用。因为2线接口为每个从机分配唯一的地址,所以可以在一条总线连接多个从机而不需要片选信号。2线接口在成功完成一次读操作后会传输一个应答位。因为2线接口只有一条数据线,所以它只能工作在半双工模式(数据的读写不可以同时进行)。因为2线接口是电平触发,所以在嘈杂环境中如果发生数据位错误,可能造成问题。表1. 3/2线接口优缺点的对比

| Interface | Advantages | Disadvantages |

| 3-Wire: SPI, QSPI, and MICROWIRE PLUS | 1. Speed 2. No pullup resistors required 3. Full-duplex operation 4. Noise immunity |

1. Larger number of bus line connections 2. Individual chip-select lines required to communicate with more than one slave at a time 3. No acknowledgment of received data |

| 2-Wire: I²C and SMBus | 1. Fewer bus line connections 2. Multiple devices share the same bus 3. Received data is acknowledged |

1. Speed: SMBus limited to 100kHz; I²C limited to 3.4MHz 2. Half-duplex operation 3. Open-drain bus lines require pullup resistors 4. Reduced noise immunity |

主机和从机经由多条总线通过串行接口进行通讯。在写周期,主机使用自己产生的时钟和数据将数据传至从机。在读周期,从机传输数据至主机。

SPI、QSPI和MICROWIRE设计

由Motorola制定的SPI接口已被很多流行的处理器和微控制器采用,比如MAXQ2000。SPI接口需要两条控制线(低电平有效CS和SCLK)和两条数据线(DIN/SDI和DOUT/SDO)。Motorola的SPI/QSPI标准称DIN/SDI数据线为MOSI (主机出,从机入),DOUT/SDO数据线为MISO (主机入,从机出),CS线为SS(从机选择)。为了叙述的清晰,我们基于从机说明3线接口的数据线。DIN是从机的数据输入线,DOUT是从机的数据读出线。本文采用低电平有效CS、SCLK、DIN和DOUT来定义3线接口中的各条线,Maxim外设使用了这些引脚名称。大多数的SPI接口有两位配置位,时钟极性(CPOL)和时钟相位(CPHA)用于设定从机何时采集数据。CPOL决定SCLK为高时总线空闲(CPOL = 1)还是SCLK为低时总线空闲(CPOL = 0)。CPHA决定在SCLK的哪一个边沿将数据移入、移出。当CPOL = 0时,将CPHA设为0,表示在SCLK的上升沿将数据移入从机;将CPHA设为1,表示在SCLK的下降沿将数据移入从机。CPOL和CPHA的两个状态允许四种时钟极性和相位的不同组合。每一种都与其它三种不兼容。为了实现主、从机间的通讯,主、从机的CPOL和CPHA必须有相同的设置。

在SPI接口的大多数应用中,SPI接口一次传送8位数据(一个字节),有一些微处理器一次传送两个或多个字节。例如,MAXQ2000微处理器可一次传送8位或16位数据。当CPOL = 0、CPHA = 0,低电平有效CS由高跳变为低,开始一个主机到从机的传输过程。在SCLK信号高低变化的八个周期内,低电平有效CS信号必须保持为低。DIN数据锁定在SCLK信号的上升沿。在同样的8位周期内,DOUT线上的从机输出数据在SCLK的每个下降沿有效。图2a给出了CPHA = 1时的详细时序;图2b给出了CPHA = 0时的详细时序。

图2a. 3线接口时序(CPHA = 1),CPHA = 1、CPOL = 1时,3线接口在时钟的上升沿将数据移入外设,在时钟的下降沿将数据移出外设。

图2b. 3线接口时序(CPHA = 0),CHPA = 0、CPOL = 1时,3线接口在时钟的下降沿将数据移入外设,在时钟的上升沿将数据移出外设。

因为总线上的每一个IC需要专属的片选线,所以低电平有效CS被用做每个从机的使能信号。如果一条总线上有四个从机,则需要四条片选线。如果从机的低电平有效CS为高电平(禁止),该从机就忽略SCLK线上的数据,将DOUT置为高阻。

部分3线接口设备可以链接成菊链的方式,而不需要为每个从机提供低电平有效的CS线,菊链方式能够用一条低电平有效的CS线和一条数据线控制多个串联从机。在菊链结构中3线接口必须包含DOUT线,如图1所示,从机#1的DOUT连接到从机#2的DIN,如此反复。

SPI标准中没有定义最大数据速率。外部设备定义了自己的最大数据速率,通常为MHz量级。微处理器可以适应很宽范围的SPI数据速率。在利用SPI接口进行通讯时,从机无法降低主机的数据速率或确定一个适当的速率。

QSPI标准和SPI标准非常相似。事实上,外设无法区分QSPI总线和SPI总线。与SPI标准中的主机不同,QSPI中的主机允许数据通过可编程的片选线传输数据。QSPI的主机甚至可以传送长度在8位和16位之间的数据,而SPI的主机只可以传送8位的数据。可以配置QSPI的设备去连续传送长度超过16字节的数据(最大为256位)。这种传输完全由QSPI设备的配置来实现,不需要MCU的操作。与SPI接口相似,QSPI接口也没有规定最大数据速率。

由National Semiconductor公司制定的老的MICROWIRE标准和SPI标准非常相似。不同的是MICROWIRE标准的时钟极性和时钟相位是固定的(CPOL = 0和CPHA = 0)。DIN的数据读取总是锁定在SCLK的上升沿。DOUT的数据输出总是在SCLK的下降沿。MICROWIRE标准没有规定最大数据速率。

芯片间电路接口(I²C)

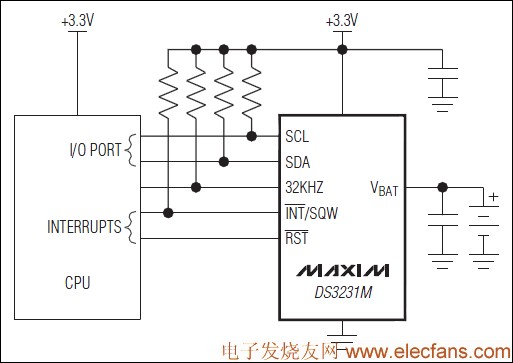

不同于全双工的3线制接口,由Philips制定的I²C接口通过一条数据线(SDA)和一条时钟线(SCL)实现半双工通信。I²C接口定义了一个简单的主/从双向通信接口。在这个体系中,MCU决定自己为主机(写模式)或为从机(接收模式)。每个从机具备专有、唯一的地址,使主机可以和多个从机通过一条总线进行通信,而不需要为每一个从机提供单独的片选线。如图3所示,从机的数目只受限于最大线上电容(400pF),I²C接口的机制基于7位或10位地址,7位的地址更为常见。在7位地址的机制中,总线上可以接127个不同的外设。SCL和SDA线为漏极开路结构,所以闲置时必须为高。当电源电压为3V时,连接一个1kΩ或更大阻值的上拉电阻;当电源电压为5V时,连接一个1.6kΩ或更大阻值的上拉电阻。

图3. 利用数据输入/输出和时钟信号进行通信的2线接口。

当SCL为高,SDA从高变为低,即发出了一个开始命令,启动I²C通信。图4a所示,每个SCL时钟传输一个数据位,传输一个字节至少需要9个数据位。一个写周期包括8个数据位和一个应答位(ACK)或者非应答位(NACK)。如图4b所示,当数据在I²C总线上传输时,在SLK的上升沿写入从机,在SLK的下降沿从机输出。在SCL时钟周期为高电平的时间内,SDA线的数据不可以改变。一次传输的完成必须跟随着一个中止或重新开始的命令,既SCL为高时,SDA由低变为高。当总线空闲时,SDA和SCL都为高。

图4a. 开始条件和停止条件,2线接口采用开始、重复开始和停止命令在主机和从机之间传输数据。

图4b. I²C应答位,应答数据时,2线接口将SDA拉低。

I²C的写周期起始于开始命令,随后是7位从机地址和第8位用于标识读、写操作。将第8位置低,表示写操作;将第8位置高,表示读操作。主机在第8个时钟周期后释放总线。如果从机应答数据传输,则在第9个时钟周期将SDA拉低。如果从机不应答写命令,则释放SDA (该数据线通过上拉电阻置于高电平)。

随后,主机写入8位命令字节,然后是第二个ACK/NACK位。接下来,主机写入8位数据字节并跟随第三个ACK/NACK位。数据字节和最后的应答位完成一个读/写周期,更新外设输出,图5a是一个写周期的详细例子。

I²C读周期起始于开始命令,随后是需要写入数据的从机地址、第8位置高,表示读操作。在ACK/NACK之后,主机写入命令字节访问从机寄存器。在第二个ACK/NACK位后,主机重新写入从机地址。在第三个ACK/NACK位后,从机控制总线,一次输出8位数据到总线上。如图5b所示,当从与上次读操作相同的从机寄存器读取数据时,主机只需要在读取从机数据之前写入从机地址。

图5. 2线接口一次传输8位数据,图5a是I²C写周期的一个例子;图5b是I²C读周期的一个例子。

I²C接口支持低速(大于100kHz)、快速(大于400kHz)和高速(大于3.4MHz)三种数据速率。I²C接口的高低电平为CMOS逻辑电平(低电平为0.3x电源电压以下,高电平为0.7x电源电压以上)。

系统管理总线(SMBus)

Intel®制定了SMBus标准用于低速通信,SMBus 2线接口与I²C接口非常相似。SMBus也使用一条数据线(SMBDATA)和一条时钟线(SMBCLK)进行通信。SMBCLK和SMBDATA也需要上拉电阻,3V供电时上拉电阻大于8.5kΩ,5V供电时上拉电阻大于14kΩ。SMBus工作电压范围在3V和5V之间,大于2.1V为高电平,低于0.8V为低电平。I²C接口和SMBus接口的最主要区别是最高/最低时钟速率,因为I²C总线为被动传输总线,不存在总线超时问题,速率可低至“静止”。SMBus接口则存在总线超时问题。如果时钟信号拉低之后的时间大于超时周期(最长为35ms)时,从机复位接口,认为发生总线超时。SMBus的超时周期限制了时钟的最小速率为19kHz。为了保证正常通信,SMBCLK的速率必须介于10kHz至100kHz之间,而I²C接口的主机或从机则可根据传输数据的需要将时钟保持在低电平。

外设举例

微处理器经常通过串行接口与外设通信,当微处理器通过2线或3线接口访问外设后,外设相应地改变其模拟或数字输出。例如,指使外设设置电池的充电的电流和电压、用温度传感器控制风扇、设置数模转换器的模拟输出等。如图6所示,通过2线接口连接微处理器和8位数/模转换器(MAX5115)。因为这个DAC有四个地址选择引脚,可以产生16个唯一的从机地址,因此可以在总线上并联16个DAC,因为MAX6641有不同的从机地址,同样的2线接口也可以设置SMBus温度传感器/风扇控制器(MAX6641),风扇控制器控制MOSFET的栅极,使其打开或关闭风扇。

图6. 由于微控制器采用的是I²C接口,与外设通信时,如DAC、温度传感器,总线只需要两条连线。

3线接口需要单独的片选线实现微处理器与多个并行从机之间的通信,更简单的2线接口用一条时钟线和一条数据线与总线上的每个设备通信。可以通过设定不同的从机地址在总线上挂接多个IC。大多数I²C接口外设具备地址选择引脚,以实现从机地址的配置。外设可以使用的从地址数等于地址选择引脚数的平方。例如,若外有两个地址选择引脚,它就可以配置四个不同的地址。

新一代设计以更少的地址选择引脚提供更多的从地址。MAX7319是输入/输出扩展芯片,可以从两个地址选择引脚(AD2和AD0)扩展出16个从地址。这些引脚可以接GND、电源(VCC)、SDA或SCL。表2列出了这16个从地址的详细信息,A6、A5、A4固定为110,A3至A0可以通过AD2、AD0设置。

表2. MAX7319仅利用2个地址线(AD2和AD0)即可编译出16个不同地址

| Pin Connection | Device Address | |||||||

| AD2 | AD0 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| SCL | GND | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| SCL | VCC | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| SCL | SCL | 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| SCL | SDA | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| SDA | GND | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| SDA | VCC | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| SDA | SCL | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| SDA | SDA | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| GND | GND | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| GND | VCC | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| GND | SCL | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| GND | SDA | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| VCC | GND | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| VCC | VCC | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| VCC | SCL | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| VCC | SDA | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

进一步改进

3线接口和2线接口有几点不同的要求,每种接口都有其特殊优势。近期内不可能用一种接口标准完全取代另一接口标准。具备I²C接口的器件发展较快,并开始融合一些SMBus接口的特点,支持诸如超时复位等功能,使接口可以根据需要关断。新的I²C从机地址长达10位,而不仅仅是7位,这给用户带来更多的灵活性。3线接口和2线接口将并存,但I²C接口似乎占有更大的市场份额,大部分微处理器支持2线接口。I²C接口的易用性及更少的连线使其增长量超过了SPI接口。

电子发烧友App

电子发烧友App

评论