摘要:随着高速信号的普及,迫切需要保证这些信号接口能够维持正确时序和保真度的措施。上升时间一般在亚纳秒级,传输延时在纳秒级。系统对时序的要求越来越严格,如果不对信号通路进行认真分析,将无法获得精确的时序。

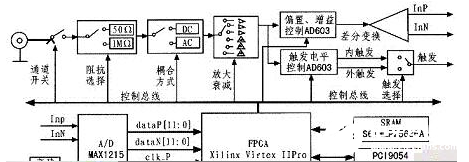

图1. 简单的高速传输线

图1所示的电路中,源和负载阻抗都是电阻。对于下面的案例研究,我们将保持其电阻性,以便简化分析。传输线的特性阻抗一般定义为ZO。在理想情况下,RS = ZO = RL。对于这些相同的案例研究,我们使用50Ω的阻抗。分析中可以采用任意阻抗,结果类似。

表1. 线路阻抗的典型特征参数

图4. 测试原理图

图4中类似的设置会产生两种反射。一是源反射系数(SRC),即RS和ZO的相互作用,二是负载反射系数(LRC),即ZO和RL的相互作用。所有这些反射系数都表示反射回来的电压,其定义如下:

以及

图4中的发生器提供幅度为1V、上升时间(tr)为500ps的阶跃脉冲。具有上述阻抗的VOUT仿真曲线如图5所示。

ticle/UploadPic/2009-5/20095583040906.gif">

ticle/UploadPic/2009-5/20095583040906.gif">

图5. RS = 0Ω,RL = ∞,ZO = 50Ω,τ = 2.5ns

这一设置的问题是在输出节点VOUT出现了满幅振荡。这一案例有些不切实际,因为我们一般不会驱动零阻抗的传输线,也不会有无穷大的负载。然而,这达到了突出问题的目的,即,如果阻抗和所采用的负载接近时,将出现这一情况。

图6. RS = 10Ω,RL = 10kΩ,ZO = 50Ω,τ = 2.5ns

图7. RS = 30Ω,RL = 500Ω,ZO = 50Ω,τ = 2.5ns

图8. RS = 50Ω,RL = 50Ω,ZO = 50Ω,τ = 2.5ns

随着频率的升高,需要投入大量的精力对整个信号通路进行建模和仿真。这样可以保证最准确、可预测的结果。

引言

本文的目的并不是推导传输线方程,解释为什么会出现以下的情况,我们的目的是说明在什么地方需要使用它以及如何使用。文章通过实际案例中的传输线理论,阐述可能出现的结果,并推荐了相应的解决方案来避免一些常见错误。典型的高速信号通路如图1所示。高速信号通路中经常出现的问题有:- 不希望的振荡

- 波形振铃

- 过冲和下冲

- 在波形上升沿和下降沿出现的边沿效应

图1. 简单的高速传输线

图1所示的电路中,源和负载阻抗都是电阻。对于下面的案例研究,我们将保持其电阻性,以便简化分析。传输线的特性阻抗一般定义为ZO。在理想情况下,RS = ZO = RL。对于这些相同的案例研究,我们使用50Ω的阻抗。分析中可以采用任意阻抗,结果类似。

基本传输线理论

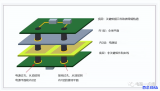

传输线有两种基本简化电路。- 无损传输线

图2所示为无损传输线。它之所以是无损的,是因为没有产生损耗的阻性元件。

图2. 无损传输线

采用四种阻抗定义无损和有损传输线。- L = 单位长度特征电感

- C = 单位长度特征电容

- R = 单位长度特征电阻

- G = 单位长度特征电导

- 有损传输线

如果R << jωL,G << jωC,那么可以忽略R和G的有损项。这是对图3的假设,由此,我们只需要参考图2。

图3. 有损传输线

- 特征阻抗(ZO),其中:

;注意:这是一个实数。

;注意:这是一个实数。

- 传输时间(τ),其中:

典型线路阻抗

表1列出了一些常见导线的典型阻抗和传输延时。表1. 线路阻抗的典型特征参数

| Type of Line | ZO (Ω) | L (nH/in) | C (pF/in) | τ (ns/ft) |

| Single wire,well above ground | 575 | 50.8 | 0.152 | 1.05 |

Micro-strip on FR4 board

|

50.71 36.09 76 |

7.17 4.71 10.45 |

2.79 4.05 1.81 |

1.65 1.65 1.65 |

| Twisted pair | 100 | 7.5 | 0.75 | 2.3 |

| Coaxial | 50 | 6.35 | 2.54 | 1.52 |

传输反射

现在,我们通过观察三个基本阻抗来研究信号通路对信号保真度的影响。- RS = 驱动源阻抗。它会随着应用而变化。某些应用中,RS为50Ω,有的应用则是75Ω;如果由具有反馈通路的缓冲器直接驱动,它可能是数十欧姆甚至更低。当输出来自CMOS缓冲器时,则可能是几千欧姆。

- ZO = 信号通路或传输线的阻抗。该信号通路也会因为我们所选择的单线、同轴电缆、微带线或带状线的不同而变化。信号通路还具有另外一个更重要的参数,即,信号通过整个通路的时间(τ)。

- RL = 负载,这是我们定义的负载。在下面的案例中它为电阻,随应用的不同而变化。

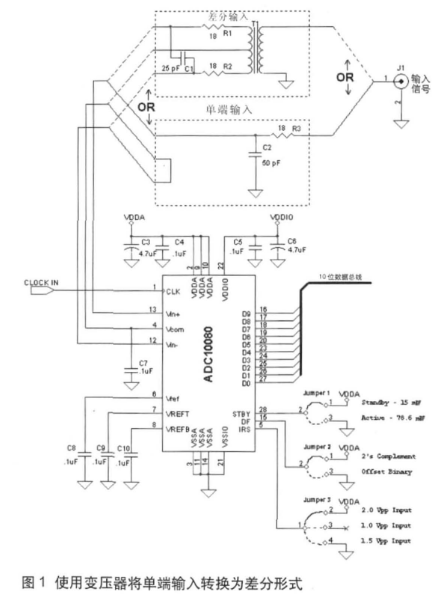

图4. 测试原理图

图4中类似的设置会产生两种反射。一是源反射系数(SRC),即RS和ZO的相互作用,二是负载反射系数(LRC),即ZO和RL的相互作用。所有这些反射系数都表示反射回来的电压,其定义如下:

以及

案例研究

下面的四个案例研究以图4中的设置为参考。唯一变化的参数是RS、ZO和RL。案例1 (RS = 0Ω,RL = ∞,ZO = 50Ω,τ = 2.5ns)

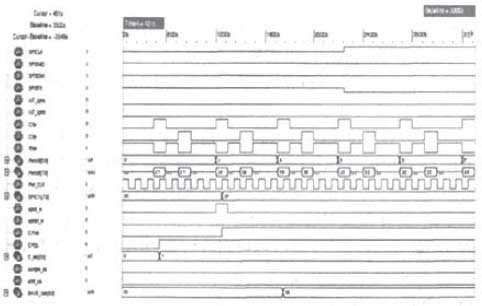

规格与其最接近的实际案例是驱动ECL输入的低阻缓冲器。图4中的发生器提供幅度为1V、上升时间(tr)为500ps的阶跃脉冲。具有上述阻抗的VOUT仿真曲线如图5所示。

图5. RS = 0Ω,RL = ∞,ZO = 50Ω,τ = 2.5ns

这一设置的问题是在输出节点VOUT出现了满幅振荡。这一案例有些不切实际,因为我们一般不会驱动零阻抗的传输线,也不会有无穷大的负载。然而,这达到了突出问题的目的,即,如果阻抗和所采用的负载接近时,将出现这一情况。

案例2 (RS = 10Ω,RL = 10kΩ,ZO = 50Ω,τ = 2.5ns)

案例2要更实际一些,它演示了使用低阻缓冲器,在这个例子中为10Ω,驱动带有高阻抗负载的50Ω传输线。结果如图6所示。在这一曲线中可以看到,在输出节点VOUT观察到了非常普遍的振铃问题;振铃最终衰减下去。

图6. RS = 10Ω,RL = 10kΩ,ZO = 50Ω,τ = 2.5ns

案例3 (RS = 30Ω,RL = 500Ω,ZO = 50Ω,τ = 2.5ns)

案例3和部分典型设置非常相似。这里,输入缓冲阻抗为30Ω,传输线是50Ω,负载为500Ω。测试设置和案例1、案例2的相同,但是振荡或者振铃大大降低了。我们在图7曲线上所看到的是VOUT节点输出波形的标准过冲和下冲。

图7. RS = 30Ω,RL = 500Ω,ZO = 50Ω,τ = 2.5ns

案例4 (RS = 50Ω,RL = 50Ω,ZO = 50Ω,τ = 2.5ns)

最后,案例4阐述了输入和传输线理想匹配以及传输线和输出相匹配的情况。图8所示为我们希望在VOUT节点出现的波形,没有振荡、振铃或过冲。

图8. RS = 50Ω,RL = 50Ω,ZO = 50Ω,τ = 2.5ns

案例结果讨论

- 这里所讨论的四个案例代表了很多可能案例的集合,这些案例出现的问题和上面看到的相似。显然,我们应该对源、传输线和负载进行匹配才能得到最佳结果。但是,实现匹配要比上面案例所建议的措施困难得多。需要仔细研究:

- 源、信号通路和负载之间没有进行仔细的匹配会导致输出产生振荡、有害的振铃效应等。图5、图6和图7非常清楚地显示了这些问题。

- 这四个案例还说明了我们能够减小甚至消除振铃问题的途径。对于这些案例,提高低阻抗源的输出阻抗就能够有效地增大输出阻抗,使其接近所需要的50Ω阻抗。对高阻抗负载进行匹配也能够有效地得到50Ω阻抗。

- 需要注意的是脉冲边沿振铃和假象会改变波形,它对系统性能的影响很大。特别是这些假象出现在比较器输入时,会导致错误的触发。假象还会增大信号通路的延时。优化信号通路有助于减小这些有害的影响。

分析并验证结果

反射图

理论上,您可以画出众所周知的“反射”图,验证上面所有案例的结果。这是非常有用方式,能够更好地理解这些信号是怎样出现在输出端的。虽然反射图很有帮助,但是需要一定的时间,如果电路比较复杂,也很难使用。最简单的方法是下面仿真一节所建议的SPICE仿真。使用SPICE仿真器之一对这四个案例进行仿真。仿真

优化信号通路最快的方法是使用SPICE型仿真器。电路如图4那样简单。记住以下几点非常重要。- 使用精确的源模型,如图4所示。只有源的输出部分需要建模。这一模型应表示出串联电阻、串联电感和并联电容。

- 图4中表示的传输线不论是PCB走线还是同轴电缆、双绞线等,都需要建立准确的模型。

- 最后,对图4中的负载也需要进行精确建模,以反映出电阻、电感和并联电容。

总结

很容易看出,如果不能仔细地匹配整个信号通路上的源、传输线和负载,将会出现信号劣化。上面讨论的四个案例对此进行了演示。如果达不到匹配,会有无法预见的误差出现。使用SPICE仿真器及其简化建模方法能够很快地找到问题所在。利用这些信息,可以迅速设计并验证解决方案。随着频率的升高,需要投入大量的精力对整个信号通路进行建模和仿真。这样可以保证最准确、可预测的结果。

电子发烧友App

电子发烧友App

评论