采用高输入频率、高速模数转换器(ADC)的系统设计是一项具挑战性的任务。ADC输入接口设计有6个主要条件:输入阻抗、输入驱动、带宽、通带平坦度、噪声和失真。看看这里罗列的这六个条件,你都了解吗?

2016-01-13 16:55:38 4864

4864

采用高输入频率、高速模数转换器(ADC)的系统设计是一项具挑战性的任务。ADC输入接口设计有6个主要条件:输入阻抗、输入驱动、带宽、通带平坦度、噪声和失真。看看这里罗列的这六个条件,你都了解吗?

2022-07-27 09:07:51 1548

1548 该应用笔记论述了如何选择适当的变压器和无源元件,并在不牺牲高速ADC动态性能的情况下获得较宽的输入频响的增益平坦度。

2023-02-09 14:21:57 1134

1134

本文详细介绍了通常应用于IF和基带的高速模数转换器(ADC)的正确布板、元件选择及元件布局。文中以高分辨率、高速数据转换器MAX12555系列为例,介绍了优化电路设计、正确高速布板、旁路和去耦技巧、热管理、元件选择及布局。

2023-02-23 14:53:19 757

757 ,它主要与二次谐波失真有关;

所需的增益和输入匹配。

较高的增益要求会提高匹配难度。此外,高增益要求会压缩ADC内部器件的裕量,从而提高非线性度,而且由于有更多功率经过外部无源器件,它们的非线性度也会

2023-12-18 06:13:51

。源电阻较高或者超过模拟前端(变压器或放大器)上满量程输入信号的一半时,目标频段中的噪声将变得难以控制,最终导致转换器性能下降。

为何如此?如果调低满量程输入,必须调高增益。在理论上,这样做

2023-12-19 06:18:48

道、250 MSPS、14 位 ADC 时的性能与输入频率之间的关系。讨论了用于共模电压、电源和接口的各种选项,这些选项经过测量,满足各种应用的要求。显示了抗混叠滤波器示例以及它们所提供的性能改进。特性高速

2015-05-11 10:33:40

描述此参考设计展示了高速放大器 THS4509 执行单端至差动转换以驱动高速模数转换器 (ADC),同时保持卓越的噪声和失真性能的能力。为交流和直流耦合应用显示了连接到 ADS4449 四通

2018-08-09 08:38:52

设计说明该子系统演示了如何在可编程增益放大器 (PGA) 配置中设置 MSPM0 内部运算放大器,动态更改增益,输出放大的信号以及使用 ADC 读取结果。该配置使用户能够使用具有高增益的小输入电压

2023-04-12 15:01:32

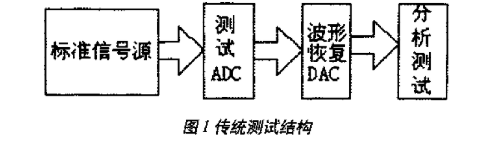

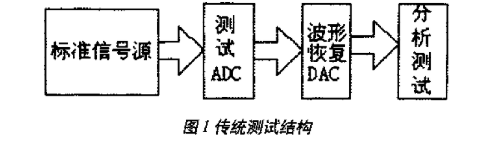

ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。因此,保证 ADC/DAC 在高速采样情况下的精度是一个很关键的问题。ADC/DAC 芯片的性能测试是由芯片

2018-04-03 10:39:35

的增益和输入匹配。 较高的增益要求会提高匹配难度。此外,高增益要求会压缩ADC内部器件的裕量,从而提高非线性度,而且由于有更多功率经过外部无源器件,它们的非线性度也会提高。这种效应一般被视为三次谐波。图

2018-09-17 15:48:29

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。

缓冲和无缓冲架构的特征

高线性度缓冲器,但需要更高的功率;

更易设计输入网络与高阻抗缓冲器接口

2023-12-18 07:42:00

来源 网络采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。 缓冲和无缓冲架构的特征 缓冲架构的基本特征 * 高线性度缓冲器,但需要更高的功率

2018-01-23 16:01:44

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。 缓冲和无缓冲架构的特征缓冲架构的基本特征高线性度缓冲器,但需要更高的功率;更易设计输入网络与高

2018-09-17 15:38:24

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。缓冲和无缓冲架构的特征缓冲架构的基本特征*高线性度缓冲器,但需要更高的功率;*更易设计输入网络与高

2018-10-18 11:23:57

如今,在设计人员面临众多电源选择的情况下,为高速ADC设计清洁电源时可能会面临巨大挑战。在利用高效开关电源而非传统LDO的场合,这尤其重要。此外,多数ADC并未给出高频电源抑制规格,这是选择正确

2018-11-21 17:14:38

而非传统LDO的场合,这尤其重要。此外,多数ADC并未给出高频电源抑制规格,这是选择正确电源的一个关键因素。本技术文章将描述用于测量转换器AC电源抑制性能的技术,由此为转换器电源噪声灵敏度确立一个基准

2018-10-15 09:49:24

正确选择输入网络元件对于高速ADC的驱动和输入网络的平衡至关重要(参考应用笔记:“正确选择输入网络,优化高速ADC的动态性能和增益平坦度”)。 在较高IF应用中,端接电阻的位置非常重要。交流耦合

2021-10-23 11:10:35

描述此参考设计展示了高速放大器 LMH6554 执行单端至差动转换以驱动高速模拟至数字转换器 (ADC),同时保持卓越的噪声和失真性能的能力。为交流和直流耦合应用显示了连接到 ADS4449 四通

2018-08-03 06:00:28

驱动器的噪声性能与ADC的ENOB作一比较。描述这一过程的例子是为采用5V电源工作的 AD9445 ADC选择和评估一款增益为2、2V 满量程输入的差分驱动器。它能处理用一个单极点滤波器限制、占用

2018-11-01 11:14:51

作为应用工程师,我们经常遇到各种有关差分输入型高速模数转换器(ADC)的驱动问题。事实上,选择正确的ADC驱动器和配置极具挑 战性。为了使鲁棒性ADC电路设计多少容易些,我们汇编了一套通用"

2018-10-17 10:52:42

。 AD745还具有卓越的直流性能,最大输入偏置电流为250帕,最大偏置电压为0.5毫伏。 AD745的内部补偿为更高的增益进行了优化,提供了更高的带宽和更快的转换速率。这使得AD745作为一个前置放大器

2020-07-10 15:51:22

。 AD745还具有卓越的直流性能,最大输入偏置电流为250帕,最大偏置电压为0.5毫伏。 AD745的内部补偿为更高的增益进行了优化,提供了更高的带宽和更快的转换速率。这使得AD745作为一个前置放大器

2020-07-13 15:33:31

AD9434BCPZ-500高速ADC芯片是ADI公司的AD9434系列单芯片采样模数转换器,该高速ADC芯片是一款专为高性能、低功耗和易用性的设备进行优化,具有出色的动态性能和适合宽带载波和宽带

2019-11-12 09:25:36

AD9481-PCB,AD9481评估板是一款8位,单芯片模数转换器(ADC),针对高速和低功耗进行了优化。该产品体积小,易于使用,转换速率为250 MSPS,在整个工作范围内具有出色的线性度和动态

2019-11-07 06:25:57

传感器的输出幅度等于ADC输入范围的一半,所以ADC驱动器的增益应设置为2。这要求Rf等于Rg,但Rf的选择有一定的灵活性。

首先来看看不同的Rf(和Rg)值对系统本底噪声和相应的预期SNR有何

2023-12-11 07:15:15

大多数高动态范围应用的理想选择。单位增益稳定性使OPA642特别适用于低增益差分放大器、跨阻放大器、+2视频线驱动器增益、宽带积分器和低失真ADC放大器。如果需要更高的增益甚至更低的谐波失真度,请考虑

2020-10-19 15:44:32

dB的小信号增益和34.5 dBm的输出三阶截取(OIP3)提供出色的性能。 该放大器在任何400 MHz带宽上具有0.5 dB的出色增益平坦度,并且CMRR为35dB。 该放大器具有通过VPD引脚

2020-03-18 16:20:27

`QPA9133是100Ω差分输入至50Ω单端输出宽带增益模块。 它非常适合作为5G m-MIMO BTS Tx路径的第一增益级,直接与收发器的DAC接口,从而无需分立的巴伦。该放大器具有出色的性能

2020-03-20 11:09:18

的性能,具有20 dB的小信号增益和35 dBm的输出三阶截取(OIP3)。 该放大器在任何400 MHz带宽上均具有0.5 dB的出色增益平坦度,并且CMRR为30dB。 该放大器具有通过VPD引脚

2020-03-20 11:15:22

近年来,随着数字信号处理技术的迅猛发展,数字信号处理技术广泛地应用于各个领域。因此对作为模拟和数字系统之间桥梁的模数转换器(ADC)的性能也提出了越来越高的要求。低电压高速ADC在许多的电子器件

2018-10-08 15:47:53

系统应用,在以下各例中,LTC6430-15 的高线性度、低噪声和宽频带性能经受住了考验。在以下第一个例子中,LTC6430-15 的差分输出与 ADC 的差分输入很相配。LTC6430-15 的输入

2018-10-18 16:03:48

使运算放大器的噪声性能与ADC相匹配在混合信号应用中,正确地选择驱动模数转换器 (ADC) 的运算放大器至关重要。设计人员必须要对一些问题进行权衡,例如:放大器噪声、带宽、设置时间、ADC 信噪比

2009-11-21 14:32:53

滤波器那样简单单调地下降。不管是哪一种情况,通常要求通带平坦度小于或等于1 dB,这对于稳定总系统增益至关重要。 输入驱动能力是由特定应用需要的系统增益决定。输入驱动能力与带宽指标密切相关,并且依赖于所选择

2018-12-14 09:27:03

正确选择输入网络元件对于高速ADC的驱动和输入网络的平衡至关重要(参考应用笔记:“正确选择输入网络,优化高速ADC的动态性能和增益平坦度”)。 在较高IF应用中,端接电阻的位置非常重要。交流耦合

2011-08-05 09:28:06

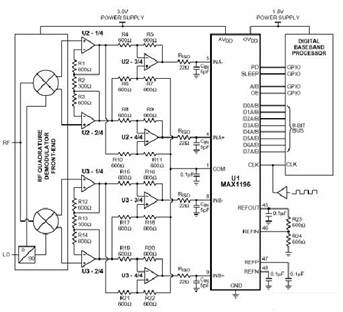

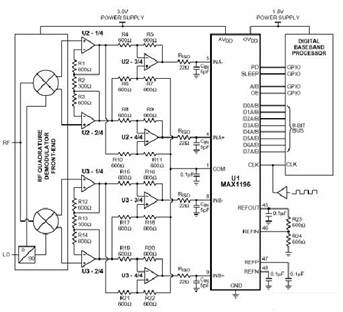

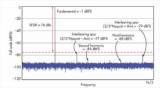

可满足高性能数字接收机动态性能要求的ADC和射频器件有哪些?

2021-05-28 06:45:13

。对于选择高速ADC时专注于其他规范的工程师来说,NSD也可能是一个完全陌生的概念。下面是一些工程师的典型问题的答案,这些答案有助于说明为什么他们应该更多地了解这种ADC性能指标:在奈奎斯特速率ADC数据

2018-11-01 11:33:13

反射到输入网络中。如果不加以衰减,它会反射回ADC且被重新采样,致使ADC的失真或交调失真性能下降。ADC的输入网络应尽可能接近50 Ω,以便最大限度地吸收此非线性电荷。使用高吸收性滤波器可抑制采样过程中产生的非线性信号音,从而改善SFDR。

2019-07-23 06:18:02

一样的——有源和无源器件均是如此,因此,无论系统最终选择了什么器件,模拟信号链中都会存在误差。 本文将描述精度、分辨率和动态范围之间的差异。本文还将揭示信号链内部的不精确性是如何累积并导致误差的。定义新设计的系统参数时,这些内容对于理解如何正确指定或选择一个ADC有着重要作用。

2021-02-25 07:19:50

如题,如何选择正确的ADC 输入端:是先滤波再放大,还是先放大再滤波呢?欢迎大家根据您的经验讨论哦

2023-11-24 06:50:39

高频应用如何才能取得最好性能所需的变频器特性?如何选择适合高频应用的高速ADC?

2021-04-13 06:45:25

本文介绍如何确定接收器增益,以及接收器增益设置太高时对接收SNR的负面影响。文章也讨论如何正确优化数字波束成形器、滤波器、检波器的动态范围以及压缩信号映射。实现上述优化后,系统将最大程度地发挥高SNR接收器的优势,大幅提高诊断性能。

2021-04-19 10:00:39

网络表是pcb自动布线的灵魂,是原理图与电路板设计的接口。只有将网络表导入后,才能进行电路板的布局布线。 单击菜单Design,选择Load nets,弹出如图19所示的导入网络表对话框。单击

2018-09-04 16:20:18

采取措施并可能在下一个数据集准备处理之前移动数据。参考选择。评估集成ADC时,一个重要标准是内部精密参考源的可用性。在某些情况下,设置多个参考电压范围的能力可确保解析ADC不同输入范围的灵活性

2019-03-18 06:45:12

目前的实时信号处理机要求ADC尽量靠近视频、中频甚至射频,以获取尽可能多的目标信息。因而,ADC的性能好坏直接影响整个系统指标的高低和性能好坏,从而使得ADC的性能测试变得十分重要。那要怎么测试高速ADC的性能?

2021-04-14 06:02:51

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

降低效率为代价。优化配电网络可以改善这些参数,同时将噪声降低到必要的水平。本文在阐述高性能信号链中电源纹波的影响的基础上进一步分析。我们将深入探讨如何优化高速数据转换器的配电网络。我们将对标准PDN

2021-07-17 07:00:01

,因此可以直接为这些电源轨供电,并且不会降低DAC动态性能。带有LC滤波器的LTM8074为2 V模拟和2 V数字电源轨供电。图11.AD9213高速ADC的优化PDN。表3比较了优化PDN与现成标准

2021-07-03 07:00:00

(ENOB)、输入带宽、无杂散动态范围(SFDR)以及微分或积分非线性度等。对于GSPS ADC,最重要的一个交流性能参数可能就是SFDR。简单而言,该参数规定了ADC以及系统从其他噪声或者任何其他杂散频率中

2018-11-01 11:31:37

请问高速ADC或DAC输入时钟占空比如果不是50%或远高于或远低于50%对ADC或DAC性能有何影响?

2018-08-16 06:09:00

请问高速ADC或DAC输入时钟占空比如果不是50%或远高于或远低于50%对ADC或DAC性能有何影响?

2023-12-13 07:28:01

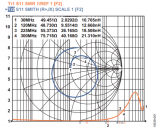

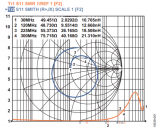

关于HMC8410的问题 贵司发布了宽带低噪声放大器HMC8410,从频响上来看,高端增益偏小(输入匹配性能大幅下降)。 看起来高频段增益降低与输入匹配恶化有关,请问这个输入匹配恶化是芯片本身输入特性决定的还是外偏置电路决定的。 通过外偏置电路可将增益平坦度调整到什么样的水平。 谢谢!

2018-08-23 18:25:22

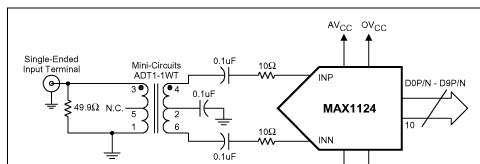

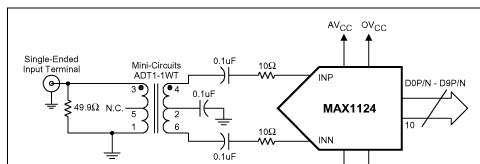

怎样将单端信号转换成差分信号呢?变压器有哪些最优匹配方法?如何改善ADC的增益平坦度并保持它的动态性能呢?

2021-04-22 06:35:25

到航空航天,这些系统在不同的应用中各有不同。。。 硅片处理技术的发展(65 nm CMOS、28 nm CMOS等)使高速 ADC 得以跨越 GSPS(每秒千兆采样)门槛,同时提供12位或14位性能

2018-11-20 10:50:51

ADC的动态性能。为了将这种影响最小化,ADC的时钟源必须具有很低的定时抖动或相位噪声。如果在选择时钟电路时没有考虑该因素,则系统的动态性能在很大程度上将不由前端模拟输入或ADC的质量决定。理想时钟

2019-05-30 05:00:04

由工程的角度系统地介绍基于CDMA20001x/EV-DO空中接口技术建立的CDMA移动通信系统无线接入网的设计与优化技术,给出了无线接入网设计与优化的详细流程和工作内容,并对网络优化

2009-06-10 14:27:42 26

26 在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能:摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(ADC)前端的信号调理。本文还阐述了如何合理选择无

2009-09-25 08:22:23 23

23

在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能

本文指导

2006-05-07 13:40:17 588

588 在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能

摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(

2008-09-11 21:04:34 755

755

副边变压器端接提升高速ADC的增益平坦度

Abstract: The following application note describes the differences between

2009-02-17 10:37:28 789

789

该应用笔记论述了如何选择适当的变压器和无源元件,并在不牺牲高速ADC动态性能的情况下获得较宽的输入频响的增益平坦度。 对于较高IF的模/数转换器(ADC),正确选

2009-04-16 16:47:50 398

398

摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(ADC)前端的信号调理。本文还阐述了如何合理选择无源元件,在较宽的输入频率范围内改善增益的平坦度,而且不会牺

2009-04-25 09:27:05 408

408

摘要:本应用笔记描述了变压器原边端接和副边端接的区别,通常用于前置高速模/数转换器(ADC)的信号调理链路。本文详细说明了在较高中频(IF)的应用中,两种端接对高速ADC增益平

2009-04-25 09:30:04 412

412

摘要:该应用笔记论述了如何选择适当的变压器和无源元件,并在不牺牲高速ADC动态性能的情况下获得较宽的输入频响的增益平坦度。 对于较高IF的模/数转换器(ADC),

2009-04-25 09:31:04 432

432

摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(ADC)前端的信号调理。本文还阐述了如何合理选择无源元件,在较宽的输入频率范围内改善增益的平坦度,而且不会牺

2009-05-01 10:45:52 501

501

摘要:本应用笔记描述了变压器原边端接和副边端接的区别,通常用于前置高速模/数转换器(ADC)的信号调理链路。本文详细说明了在较高中频(IF)的应用中,两种端接对高速ADC增益平

2009-05-01 10:50:25 490

490

摘要:该应用笔记论述了如何选择适当的变压器和无源元件,并在不牺牲高速ADC动态性能的情况下获得较宽的输入频响的增益平坦度。 对于较高IF的模/数转换器(ADC),

2009-05-01 10:51:07 805

805

摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(ADC)前端的信号调理。本文还阐述了如何合理选择无源元件,在较宽的输入频率范围内改善增益的平坦度,而且不会牺

2009-05-07 11:10:01 349

349

摘要:本应用笔记描述了变压器原边端接和副边端接的区别,通常用于前置高速模/数转换器(ADC)的信号调理链路。本文详细说明了在较高中频(IF)的应用中,两种端接对高速ADC增益平

2009-05-08 10:30:36 612

612

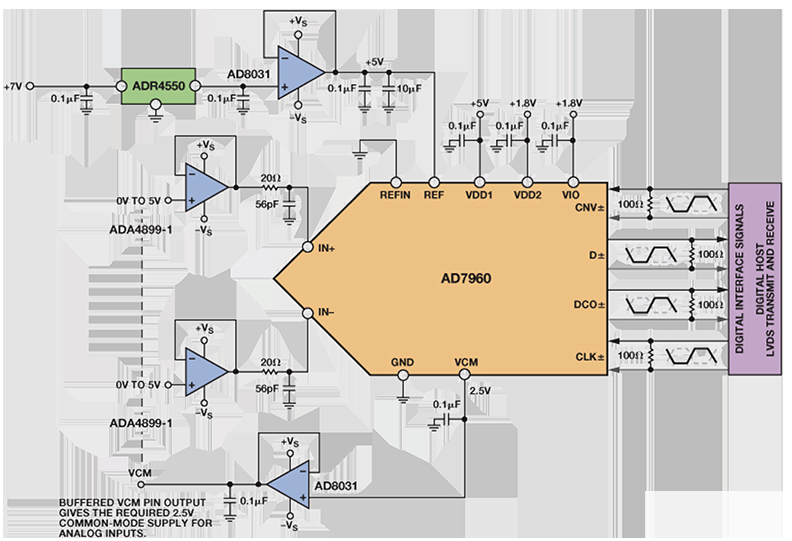

设置高速ADC的共模输入电压范围(中文)

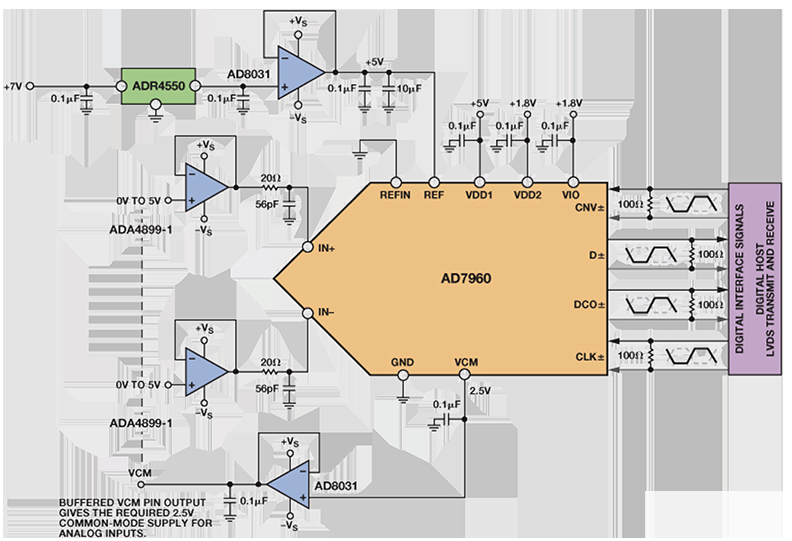

对于包含基带采样、高速ADC的通信接收机,输入共模电压范围(VCM)非常重要。特别是对于单电源供

2010-03-30 17:59:39 3883

3883

采用高输入频率、高速模数转换器(ADC)的系统设计是一项具挑战性的任务。ADC输入接口设计有6个主要条件:输入阻抗、输入驱动、带宽、通带平坦度、噪声和失真。

2013-08-22 16:13:18 24

24 在为高性能系统选择宽带模数转换器(ADC)时,需要考虑多种模拟输入参数,比如,ADC分辨率、采样速率、信噪比(SNR)、有效位数(ENOB)、输入带宽、无杂散动态范围(SFDR)以及微分或积分非线性度等。 对于GSPS ADC,最重要的一个交流性能参数可能就是SFDR。

2018-07-10 01:52:00 8762

8762

本文讨论了高频应用要取得最好性能所需的变频器特性,包括平坦的频率响应、高输入带宽、低输入满刻度电压范围以及针对多阵列系统调整参数的能力。文章还讨论了与选择高分辨率高速ADC有关的系统设计考虑因素。

2017-09-15 16:07:55 26

26 EDFA 的增益平坦化是 DWDM 系统中的关键问题,介绍了 EDFA 增益平坦滤波器的实现技术原理并对其关键技术参数进行了比较,认为啁啾光栅增益平坦滤波器是一较好的选择。试验表明,在高功率

2017-11-07 10:17:52 14

14 TIDA-01053 是一种 ADC 驱动器参考设计,用于为高动态范围仪表优化 THD、噪声和全系统 SNR。ADC 输入的高电容性质给驱动器设计和器件选择过程带来了一些独特的挑战,需要同时确保

2017-12-07 18:13:38 0

0 本应用注释讨论了如何通过设计正确的时钟电路和良好的模拟输入网络,来优化高速流水线ADC的性能,以及如何将ADC的高速不失真的数据输送到FPGA或ASIC上。

2018-05-18 10:34:32 10

10 本应用注释讨论了如何通过设计正确的时钟电路和良好的模拟输入网络,来优化高速流水线ADC的性能,以及如何将ADC的高速不失真的数据输送到FPGA或ASIC上。

2018-05-18 10:41:22 0

0 在较高IF应用中,端接电阻的位置非常重要。交流耦合输入信号可以在变压器的原边或副边端接,具体取决于系统对高速ADC增益平坦度和动态范围的要求。宽带变压器是一个常用元件,能够在较宽的频率范围内将单端信号转换成差分信号,提供了一种快速、便捷的解决方案。

2020-07-31 17:56:42 1554

1554

高速ADC是信号处理机的不可欠缺的组成部分,其性能的好坏对信号处理系统的整体性能也至关重要。通常ADC的技术参数是由生产厂商提供,可作为设计的重要依据,但是在电路板上形成的ADC模块的性能如何,还与

2020-08-01 11:35:54 3431

3431

固定增益差分放大器简化对高速 ADC 的驱动

2021-03-21 03:06:00 10

10 电子发烧友网为你提供如何正确选择一个ADC资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:45:33 0

0 AD7329:1 MSPS,8频道,软件选择器,True双极输入,12位增益Sign Sign ADC数据Sheet

2021-05-10 08:15:59 2

2 AD7322:2频道,软件选择table,True双极输入,1 MSPS,12位增益Sign Sign ADC数据Sheet

2021-05-10 11:54:17 1

1 多通道应用中使用的精密高速数据采集系统需要最先进的性能。本模拟技巧涵盖了在选择ADC驱动器以优化信号链性能时需要考虑的关键规格。

2023-01-08 16:16:36 593

593

正确选择电路板元件是满足高中频模数转换器(ADC)苛刻的高动态性能和增益平坦度要求的重要因素。以下技术说明将提供有关输入网络的适当选择,这些输入网络旨在借助宽带变压器、端接电阻器和滤波电容器轻松进行单端到差分输入信号转换。

2023-01-10 11:29:26 734

734

以下应用笔记描述了高速模数转换器(ADC)之前信号调理电路中常用的变压器的初级侧和次级端接之间的差异。本文详细介绍了这两种端接方案对专为高中频应用设计的ADC的增益平坦度和动态性能的影响。

2023-01-13 14:49:03 538

538

模数转换器 (ADC) 代表接收器、测试设备和其他电子设备中模拟和数字世界之间的链接。如本系列文章第1部分所述,许多关键动态参数提供了给定ADC预期动态性能的精确相关性。本系列文章的第 2 部分介绍了用于测试高速 ADC 动态规格的一些设置配置、设备建议和测量程序。

2023-02-25 09:26:43 1754

1754

本文指导用户如何选择合适的变压器,通常用于高速模数转换器(ADC)之前的信号调理电路。本文还介绍了如何选择无源元件,以便在很宽的输入频率范围内实现增益平坦度,同时又不牺牲这些ADC的动态性能。最后

2023-02-27 14:33:34 583

583

作为应用工程师,我们经常遇到各种有关差分输入型高速模数转换器(ADC)的驱动问题。事实上,选择正确的ADC驱动器和配置极具挑战性。为了使鲁棒性ADC电路设计多少容易些,我们汇编了一套通用“路障”及解决方案。本文假设实际驱动ADC的电路—也被称为ADC驱动器或差分放大器—能够处理高速信号。

2023-11-27 08:31:36 2

2

电子发烧友App

电子发烧友App

评论