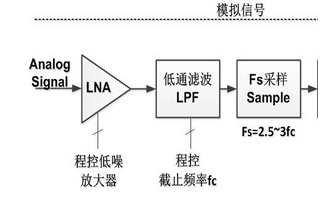

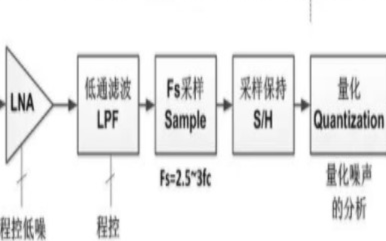

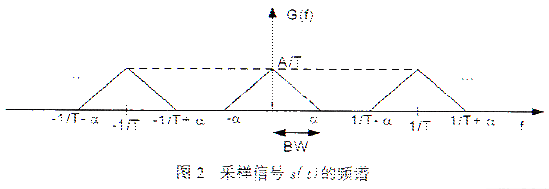

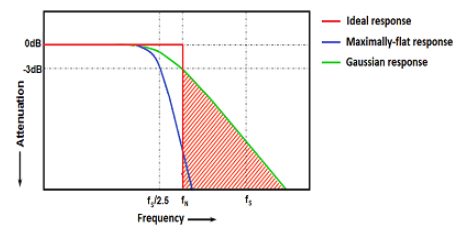

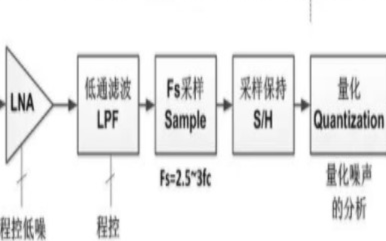

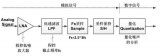

实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。

2018-02-26 09:13:00 22038

22038

RF采样转换器可捕获高频信号和大带宽信号;但是,并非每种应用都能利用需要极高速采样的信号。就带宽或输出频率不过高的情况而言,利用RF采样转换器的高采样速率能力仍存在一大优势。 采样定理规定,采样速率

2018-05-15 09:12:14 8377

8377

市面上的高带宽功率分析仪往往采样率并不高,只有带宽的二分之一或更低。这真的合理吗?能可靠采样输入信号吗?这样的采样方法能支持高精度的电参数测量吗?对比高采样率采样,这样的采样方法有什么好处?本文将解析这一现象背后的原理。

2015-08-27 10:25:42 2949

2949

实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。

2015-12-18 09:35:13 6374

6374

在信号链中运用采样保持放大器(THA),可以从根本上扩展带宽,使其远远超出 ADC 采样带宽,满足苛刻高带宽的应用的需求。本文将证明,针对 RF 市场开发的最新转换器前增加一个 THA,便可实现超过

2018-03-01 04:44:00 10311

10311

带宽有限(band-limited) 采样频率大于2倍信号最高频率后可以无失真的恢复出原始信号。

2022-08-18 09:37:50 3521

3521 有大神知道12位ADC采样保持器里面的电容量级是多少吗?因为设计电路的时候要使用抗混叠滤波器,需要考虑采样保持器电容与抗混叠滤波电容的大小关系

2023-11-02 06:27:44

信号的有效分析带宽可以深入的解释一下吗

2013-11-04 20:27:00

做一个FIR数字低通滤波器,信号源是正弦信号加均匀白噪声,显示混叠信号和经过滤波后信号波形 以及频谱分析,

2014-05-10 00:05:31

AD9684-500EBZ,AD9684评估板,双通道,14位,500 MSPS ADC。该器件具有片上缓冲器和采样保持电路,专为低功耗,小尺寸和易用性而设计。该产品设计用于采样宽带宽模拟信号

2020-03-05 06:46:33

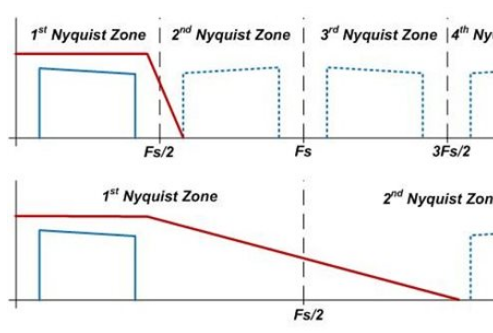

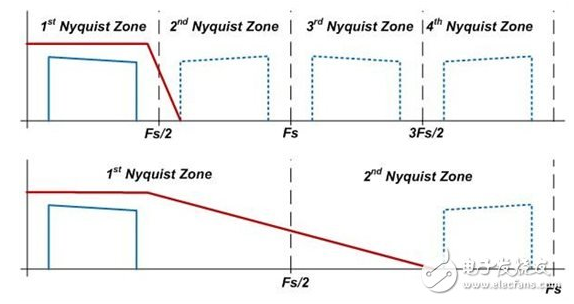

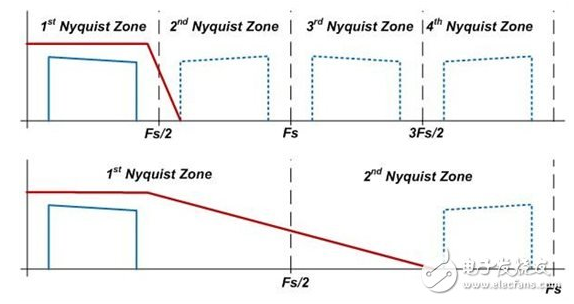

文章将会详细地探讨这个话题。)如果不满足这个条件,那么子频谱就会重叠,原始频谱就会改变,即使再强的低通滤波也不能恢复原始信号。 混叠 子频谱重叠是当我们使用低于奈奎斯特速率的采样频率时,信息被破坏而

2020-09-02 17:42:04

将突出为CTSD ADC的性能指标。主要亮点:过采样提供内在的抗混叠能力,因为谐波落在CTSD带宽之外。失真产物要混叠回通带,其高频分量必须远超Fs/2。CTSD架构使用阻性输入,其比开关电容输入更

2018-10-31 10:48:38

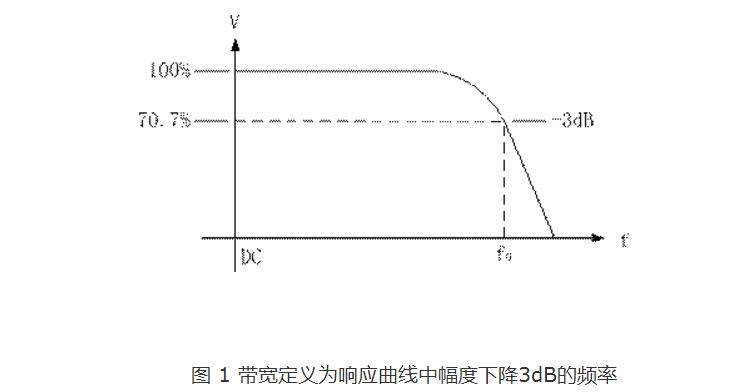

阅读手册,AD7606内部有一个抗混叠滤波器,在-5~+5V范围下的-3db带宽为15khz,在-10~10V范围内-3db带宽是22KHZ,下降沿大约在10khz左右开始。

我的回波信号

2023-12-18 06:22:57

字域内复制原始信号,ADC必须至少以输入信号最高频率分量的两倍对输入信号进行采样—否则的话,会产生混叠。所需的最小采样率被称为那奎斯特速率。或者反过来看,ADC能够准确转换的最高频信号为采样率的一半,这

2018-09-06 16:00:00

100dBFS(满量程)的神奇屏障,用户面临的真正挑战体现在为要数字化的信号设计模拟调理电路,以及相关抗混叠滤波器的设计两个方面。在过去的二十年中,采样速率和滤波技术已经有了很大的发展,现在我们可以结合

2021-08-04 07:00:00

性能, 采用三阶巴特沃斯滤波器和低噪声超宽带宽差分放大器ADL5565 设计出用于高频信号直接采样系统中的抗混叠滤波器。

为了抵消三阶巴特沃斯滤波器插入损耗, 需对流过滤波器信号放大。在本系统中使

2023-11-23 06:01:47

HiADS1675 ,内部有2种滤波器 ,delta-sigma (ΔΣ) 是用做抗混叠滤波器吗?或者还用作其他? 有没有相关的详细文章介绍?

2019-05-22 06:17:18

喜 我有几个问题。 1. Acc的顺序抗混叠滤波器是什么? 2.陀螺的顺序抗混叠滤波器是什么? 3.如果截止频率高于nyquist频率,DLPF1滤波器如何帮助我? 谢谢, 阿米尔

2018-09-11 16:41:19

DSP的ADC前端除了有抗混叠滤波器还有什么??

2012-10-14 21:02:50

我正在尝试使用我的80GSa / s示波器(DSO-X 90164A)模拟5GSa / s数字化仪采样率的混叠效应。我想知道示波器如何实现从16GHz到4GHz的模拟带宽减少?我想知道在哪里可以找到

2018-10-24 11:28:42

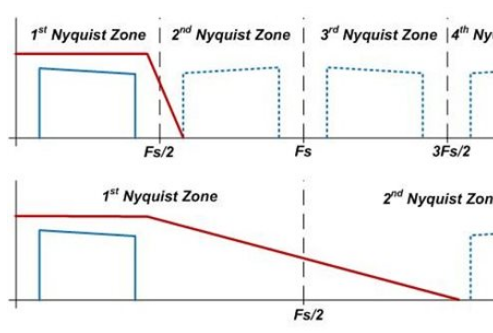

高的情况而言,利用RF采样转换器的高采样速率能力仍存在一大优势。 采样定理规定,采样速率必须至少是信号最大带宽的两倍。低于该速率的采样被称为欠采样,会引起混叠现象;笔者的上一篇博客讨论了这种方法的好处

2018-09-06 14:58:46

各位好!想请教如下问题:在资料中,看到说△-∑型ADC采用过采样技术,因此大部分情况下可以用一个简单地RC低通滤波器来进行抗混叠滤波。我想请教的是:用RC低通滤波的话,转折频率是可以满足,但是RC

2019-05-17 13:30:09

,RSP1分析带宽偏窄,因此在FFT频谱中出现混叠。如果希望匹配,方法为:在IQ输出到FFT采样输入之间增加低通滤波环节。但是不适合对风扇转速的测量。方案考虑1. 提高FFT采样速率,减少FFT分析

2016-03-17 12:33:15

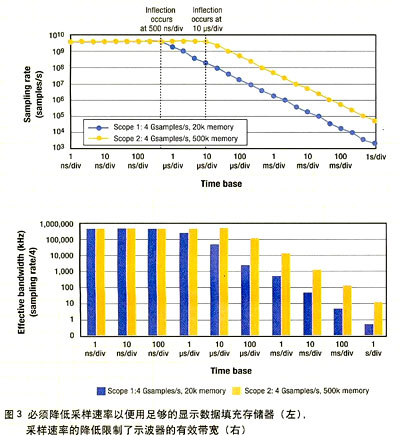

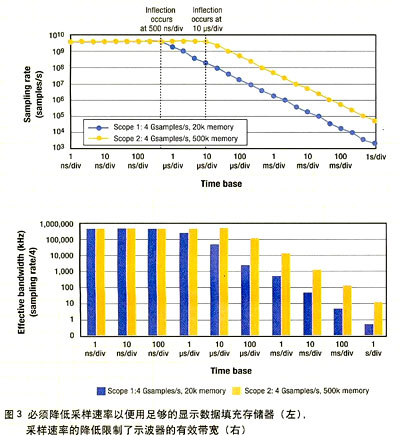

数字示波器(DSO)与模拟示波器相比有许多明显的优势。数字示波器可以采样、数字化和存储波形,帮助你测量、分析和存档信号。但采样过程随之也会带来诸多问题。混叠、同步采样和插值器错误会让你错误理解测量

2019-03-20 15:54:52

频率时,可能在输出端发生混叠。由于使用采样系统,故这是所有斩波器和斩波稳定结构的固有限制。斩波器稳定的结构得益于具有前馈路径,如图2框图的上信号路径所示,这是一种将增益带宽扩展到采样频率之外的高速信号

2020-01-08 07:00:00

你好!有没有人知道什么会对UART发送的信号产生混叠效应?

2019-09-30 06:00:58

导致混叠现象。大多数应用都要求避免混叠,混叠问题的严重程度与这些混叠频率分量的相对强度有关。 采样频率必须大于被采样信号带宽的两倍,另外一种等同的说法是奈奎斯特定律必须大于被采样信号的带宽。如果信号

2019-12-19 15:44:20

一般在ADC前端都会加抗混叠滤波器。但是,如果不加抗混叠滤波器的话,ADC采集到的信号频谱是不是由无限宽的频谱叠加得到的?比如我拿一个50MHz的ADC采集空中信号,是不是3GHz的信号也会混叠到我采集到的信号中?希望有大神能解答一下,谢谢啦~

2016-11-17 15:22:15

产生混叠的来源:这一点在奈奎斯特定理中给出了说明。奈奎斯特定理指出:时间连续信号转换成离散信号时,需要在一个周期内的采样次数多于2次。如果采样次数不够,将无法恢复丢失的信息。从图1可以更清晰地看到

2019-01-02 19:03:43

专家您好:

我使用的是DM368+TVP5158,采集4路D1,NTSC,分辨率720*576,(或720*480),采集到的静态图像正常,但是当画面有移动物体时,换面产生错误和混叠,在编码前的YUV422的数据帧就有此现象。

2018-05-31 07:58:34

LTC1569简介LTC1569的引脚功能LTC1569的工作模式利用LTC1569实现抗混叠滤波应用LTC1569设计低通滤波器的注意事项

2021-04-07 06:33:38

如何利用奈奎斯特定理去分析频率混叠现象?

2021-05-10 07:00:54

原来的信号。可见示波器采样率高低对波形构建的真实性有直接的影响。采样率低会对波形产生的影响如下:1.波形失真;2.波形混叠;3.波形漏失;通过以上图示可以看出采样率低会对测试结果影响非常大,那么如何选择

2020-02-12 14:26:05

AFAIK IIS2DH 没有模拟抗混叠滤波器。如果我使用低 ODR 设置并且输入信号频率高于 ODR/2,是否会出现混叠?因为在我们的测试中,我们经常在信号输出信号中出现尖峰。如果是这种情况,我们只能提高采样率吗?

2022-12-16 06:38:27

我想用AD9467进行射频信号的欠采样处理,如何设计前端的调理电路来保证其抗混叠和阻抗匹配呢?前端射频信号是500MHz±5MHz的信号,经过500±6MHz的带通滤波器和射频放大器对信号进行滤波

2023-12-11 06:14:17

在我的上一篇文章中,我讨论了增量-累加模数转换器 (ADC) 的2个重要特点。这2个特点简化了抗混叠滤波器的设计:一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号

2018-09-05 14:52:59

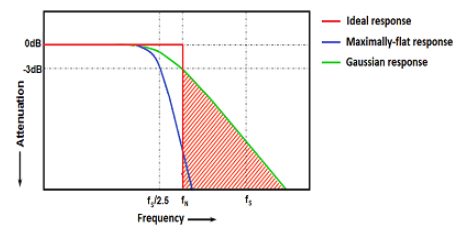

成为带宽限制。这是抗混叠滤波器的目的。通过在采样之前使信号通过低通滤波器,我们可以衰减指定频率以上的频谱内容,从而创建一个上限频率。 由于现实生活中的滤波器不会在截止频率以上产生无限的衰减,因此信号将不

2020-09-18 10:12:55

中有两种方法可以实现这一点。首先是减少采集存储器的长度。第二种是使用稀疏或抽取函数来抽取数据。降低采样率会增加数据混叠的可能性,尤其是在捕获富含谐波的信号时。为了限制混叠的可能性,可以以高速率对数据进行

2019-02-23 13:41:27

中有两种方法可以实现这一点。首先是减少采集存储器的长度。第二种是使用稀疏或抽取函数来抽取数据。降低采样率会增加数据混叠的可能性,尤其是在捕获富含谐波的信号时。为了限制混叠的可能性,可以以高速率对数据进行

2019-03-09 11:53:43

摘要:在数据采样系统中,高于二分之一采样率的频率成分“混叠”(搬移)到有用频带。大多数时间,混叠是有害的副作用,所以在模/数(AD)转换级之前,将“欠采样”的较高频率简单滤除。但有时候,特意设计利

2019-07-30 06:11:02

输入85MHZ中频,带宽20MHZ(起始频率:75MHZ;截止频率:95MHZ)的中频信号给AD9649;想设计一个无源抗混叠滤波器;请高手给予指点!

2015-04-23 15:19:28

本文对有源抗混叠滤波电路对驱动运放的要求,进行了分析,分别从高频参数单位增益带宽和高速参数建立时间,压摆率以及运放的电流驱动能力,分析了系统对驱动放大器的要求。

2021-04-07 06:09:16

高性能模式下使用 3.3kHz ODR,模拟抗混叠滤波器带宽设置为 1.5kHz,数字滤波器设置为 ODR/2。在生成的频谱图中,频率扫描信号在多次穿过 ODR/2、ODR 和 1.5*ODR 后混叠

2022-12-15 08:14:24

这一点还是很难的)。[size=1.5em][size=1.5em]低通滤波器在Nyquist采样定理中已经提过,要满足采样定理必须要求信号带宽有限,使用大于2倍的最高信号频率采样才能保证信号的不混叠

2018-09-14 14:38:47

零漂移精密运算放大器:测量和消除混叠以实现更精确的电流检测

2021-01-11 06:32:48

DN16- 用于抗混叠应用的开关电容低通滤波器

2019-07-08 09:21:14

的,那么在对信号进行采样和量化时,如果采样率是被测信号带宽的2倍以上,就可以完全重建或恢复出信号中承载的信息而不会产生混叠。如下图就是采样率不足导致的信号混叠,可以看到采集到的信号和原始信号相比,频率

2020-08-23 16:23:05

测信号的变化快很多。那么究竟要快多少呢?数字信号处理中的奈奎斯特(Nyquist)定律说, 如果被测信号带宽是有限的,那么在对信号进行采样和量化时,如果采样率是被测信号带宽的2倍以上,就可以完全重建或

2021-02-19 14:19:21

15kHz上对模拟信号进行采样,此时的频率分量高达20kHz—你将最终遇到“混叠”问题,或者将上部分量折叠进入输入信号的工作频段(请见图1)。这些混叠信号将增加到原始信号上,并且将无法把已混叠频率分量

2018-09-05 15:54:06

要求信号带宽有限,使用大于2倍的最高信号频率采样才能保证信号的不混叠。低通滤波器的一个考虑就是使信号带宽有限,以便于后期的信号采样,这个低通滤波器是硬件实现的。另一方面,实际情况中我们也只会对某个频频

2015-11-26 16:22:01

数字示波器(DSO)与模拟示波器相比有许多明显的优势。数字示波器可以采样、数字化和存储波形,帮助你测量、分析和存档信号。但采样过程随之也会带来诸多问题。混叠、同步采样和插值器错误会让你错误理解测量

2017-08-11 14:30:58

时,可能在输出端发生混叠。由于使用采样系统,故这是所有斩波器和斩波稳定结构的固有限制。 斩波器稳定的结构得益于具有前馈路径,如图2框图的上信号路径所示,这是一种将增益带宽扩展到采样频率之外的高速信号

2019-09-26 08:30:00

如何利用开关电容滤波器实现抗混叠滤波?

2021-04-23 06:12:02

再设计电路时,差分信号在介入差分ADC时,需要在AINN和AINP输入引脚前加入一阶抗混叠滤波器,滤除高频干扰,请问专家应该如何设计,或则有什么参考资料,第一次设计抗混叠滤波器!谢谢

2018-11-14 11:07:35

大家好!我看一些电能电量分析采集的文献中提到对信号进行FFT,所以要在ADC前端设计抗混叠滤波器,以避免产生延拓频率的噪声。一般采样频率为fs时,滤波器截止频率为fs/2。如果我不对信号进行频谱分析

2018-10-09 16:08:19

TI生产的pipeline型的ADC常常利用采样过程中的混叠现象,用较低的采样率来把中频处的信号搬移到基带在进行处理,这样可以降低对高速ADC的速度要求,这时在采样前需要对模拟信号进行带通滤波,保证

2019-02-26 08:59:33

15kHz上对模拟信号进行采样,此时的频率分量高达20kHz—你将最终遇到“混叠”问题,或者将上部分量折叠进入输入信号的工作频段(请见图1)。这些混叠信号将增加到原始信号上,并且将无法把已混叠频率分量与原始

2022-11-18 07:48:54

原文地址:降采样,过采样,欠采样,子采样,下采样作者:bluepig111111降采样:2048HZ对信号来说是过采样了,事实上只要信号不混叠就好(满足尼奎斯特采样定理),所以可以对过采样的信号作

2021-08-09 08:14:52

降采样:2048HZ对信号来说是过采样了,事实上只要信号不混叠就好(满足尼奎斯特采样定理),所以可以对过采样的信号作抽取,即是所谓的“降采样”。“采样频率从2048HZ到32HZ每隔64个样本

2021-08-17 06:10:37

高带宽功率分析仪采样率不高,能靠采样输入信号吗?这样的采样方法能支持高精度的电参数测量吗?对比高采样率采样,这样的采样方法有什么好处?

2021-04-29 06:18:29

高精度SAR模数转换器的抗混叠滤波考虑因素

2021-01-11 07:53:43

采样率对示波器带宽的影响

在针对某个测量需求而选择示波器时,我们首先考虑的第一件事就是需要多大的带宽才能精确地重建我们的信号。毕竟

2009-08-25 00:04:44 1925

1925

射频采样架构为传统超级外差架构提供了替代方案。射频采样模数转换器(ADC)以高采样率工作,将射频(RF)信号直接转换为数字信号,由于高采样率,射频采样架构支持很宽的信号带宽。更高的信号带宽可扩大

2017-05-03 16:15:45 23

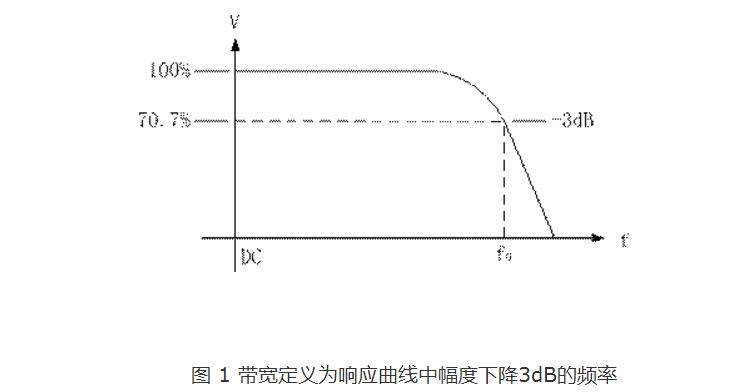

23 本文开始介绍了带宽的定义以及示波器带宽的含义,其次阐述了采样率及采样定理,最后阐述了示波器的带宽与采样率两者之间的联系。

2018-04-09 11:18:00 66858

66858

实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。

2019-10-23 15:54:11 1765

1765 实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。

2019-11-05 15:25:18 2496

2496 RF采样转换器可捕获高频信号和大带宽信号;但是,并非每种应用都能利用需要极高速采样的信号。

2019-12-18 16:39:47 726

726 RF采样转换器可捕获高频信号和大带宽信号;但是,并非每种应用都能利用需要极高速采样的信号。

2020-02-27 15:30:29 758

758

由于有限的输入带宽,除非您将采样率设置得非常低,否则ADC的带宽通常小于奈奎斯特频率。

2021-01-14 14:35:45 19331

19331

若想分析5G NR和其他未来无线标准宽带信号,高分析带宽至关重要。为了能以有限的预算满足这种测试需求,罗德与施瓦茨公司(Rohde & Schwarz)为中端信号和频谱分析仪R&S FSVA3000新增优异的1 GHz内部分析带宽。

2020-11-19 11:47:44 1914

1914 带宽有限(band-limited) 采样频率大于2倍信号最高频率后可以无失真的恢复出原始信号。

2022-02-11 14:08:07 2793

2793

射频接收系统通常使用数字信号处理算法进行信号解调和分析,因此需要使用ADC对信号进行采样。根据采样频率的不同,可以分为射频直接采样、中频采样、IQ采样。射频采样和中频采样只需要一路ADC,采样结果

2022-07-28 09:05:47 2628

2628 Nyquist采样定理 尽管大家都知道,但还是提一提大牛奥本海姆的《信号与系统》,来捋一捋几个点: 带宽有限(band-limited) 采样频率大于2倍信号最高频率后可以无失真的恢复出原始信号

2023-06-04 10:55:02 347

347

使用ADC时需要重点关注的参数。采样率和带宽之间的关系是非常重要的,下面将详细分析采样率和带宽之间的关系。 一、 ADC采样率和带宽的定义 首先,我们需要了解ADC采样率和带宽的定义。采样率是指ADC每秒钟可以采集并转换模拟信号的次数。例如,如果ADC的采样率为10kHz,则每秒可以将模

2023-09-12 10:51:12 6012

6012

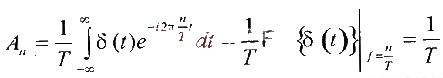

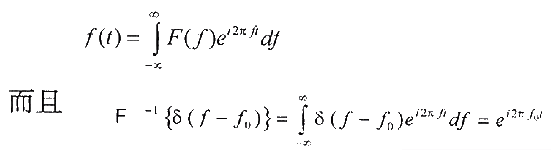

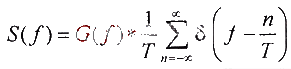

根据以上结果,再重新考虑被采样的基频信号,它的傅立叶变换为:

根据以上结果,再重新考虑被采样的基频信号,它的傅立叶变换为:

则S(f)可改写为:

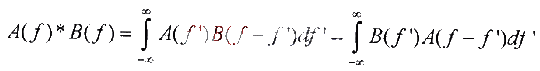

则S(f)可改写为:  上式就是我们常说的采样定律。它表明在时域里按周期T采样得到的信号会以1/T 的频率重复原始信号的频谱,如图2所示。

上式就是我们常说的采样定律。它表明在时域里按周期T采样得到的信号会以1/T 的频率重复原始信号的频谱,如图2所示。  为保留所有原始信号的信息,必须保证每一个重复频谱之间不发生混叠。否则,就不可能从采样信号中恢复出原始信号。混叠意味着高频段掩盖了低频段信号,如图3所示。为避免混叠,必须满足以下条件:1/T≥2α或1/T≥2BW。也可用采样频率表示为: fSAMPLING≥2BW 以上表明不会产生混叠的最小采样频率是2BW。这就是奈奎斯特采样定律。

为保留所有原始信号的信息,必须保证每一个重复频谱之间不发生混叠。否则,就不可能从采样信号中恢复出原始信号。混叠意味着高频段掩盖了低频段信号,如图3所示。为避免混叠,必须满足以下条件:1/T≥2α或1/T≥2BW。也可用采样频率表示为: fSAMPLING≥2BW 以上表明不会产生混叠的最小采样频率是2BW。这就是奈奎斯特采样定律。

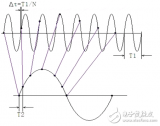

还要注意的是对有限带宽信号的假设。从数学上分析,一个信号不可能是真正有限带宽的。傅立叶变换定律告诉我们,如果一个信号在时域是有限的,则它的频谱就会扩展到无穷大,如果它的带宽是有限的,则它在时域上就是无限的。很显然,我们找不到一个具有无穷大周期的时域信号,所以也不可能有真正的有限带宽信号。不过绝大部分实际信号的频谱能量都集中在有限带宽中,因此前面的分析对这些信号仍然有效。采样正弦信号可以非常简单和方便地检测出采样频率是否偏低,因为混叠现象是采样频率偏低所特有的现象。正弦信号的频谱里的(冲激串函数)尖峰只在相应的频率点出现,出现混叠时,尖峰会移到另一个频率点,这一点对应着混叠信号。 以下测试结果是用Maxim公司最新推出的125Msps、12位ADC:MAX19541测试得出的。图6是它的输出信号频谱,对应的输入信号频率fIN=11.5284MHz。很明显,最高的尖峰恰好出现在该频率点上。频谱图里还有其他一些较小的尖峰,它们是由ADC的非线性引起的谐波造成的,和本文的讨论主题无关。由于采样频率fSAMPLE = 125MHz,远远大于奈奎斯特定律要求的输入信号频率的2倍,因此没有混叠现象。如果将输入频率提高到fIN = 183.4856MHz,大于fSAMPLE/2,此时应该会有混叠出现。图7是fIN>fSAMPLE/2时的输出频谱图,主尖峰落在58.48MHz处,这就是混叠信号。也就是说,在58.48MHz出现了一个原始信号不包含的信号。在图6和图7中都只给出了奈奎斯特频率以下的频谱,因为频谱是周期性的,图中的显示部分已经包含了所有必要信息。 图6和图7

还要注意的是对有限带宽信号的假设。从数学上分析,一个信号不可能是真正有限带宽的。傅立叶变换定律告诉我们,如果一个信号在时域是有限的,则它的频谱就会扩展到无穷大,如果它的带宽是有限的,则它在时域上就是无限的。很显然,我们找不到一个具有无穷大周期的时域信号,所以也不可能有真正的有限带宽信号。不过绝大部分实际信号的频谱能量都集中在有限带宽中,因此前面的分析对这些信号仍然有效。采样正弦信号可以非常简单和方便地检测出采样频率是否偏低,因为混叠现象是采样频率偏低所特有的现象。正弦信号的频谱里的(冲激串函数)尖峰只在相应的频率点出现,出现混叠时,尖峰会移到另一个频率点,这一点对应着混叠信号。 以下测试结果是用Maxim公司最新推出的125Msps、12位ADC:MAX19541测试得出的。图6是它的输出信号频谱,对应的输入信号频率fIN=11.5284MHz。很明显,最高的尖峰恰好出现在该频率点上。频谱图里还有其他一些较小的尖峰,它们是由ADC的非线性引起的谐波造成的,和本文的讨论主题无关。由于采样频率fSAMPLE = 125MHz,远远大于奈奎斯特定律要求的输入信号频率的2倍,因此没有混叠现象。如果将输入频率提高到fIN = 183.4856MHz,大于fSAMPLE/2,此时应该会有混叠出现。图7是fIN>fSAMPLE/2时的输出频谱图,主尖峰落在58.48MHz处,这就是混叠信号。也就是说,在58.48MHz出现了一个原始信号不包含的信号。在图6和图7中都只给出了奈奎斯特频率以下的频谱,因为频谱是周期性的,图中的显示部分已经包含了所有必要信息。 图6和图7 电子发烧友App

电子发烧友App

评论