Gigabit以太网络收发器引爆连接端口成长风潮

以太网络已成为全球应用最广泛的企业通讯标准,随着多数企业开始将传统信息系统转移到网络上,企业网络的频宽使用量每年都出现大幅成长;除此之外,桌上型会议、网络虚拟会议、和群组导向的生产力应用等新技术也让今日的网络永远处于尖峰使用状态。

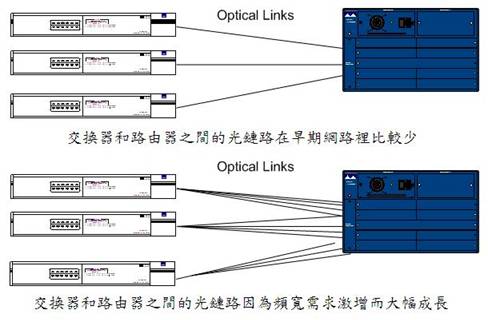

随着频宽需求飞快增加,交换路由器 (switch router) 设备制造商也开始发展能够延展扩充的系统,以便满足市场对于传输频宽的无止境要求。这个结果就反映在交换路由器的连接埠数目上,典型交换路由器的埠数在短时间内就从每套系统8个连接端口激增为72个连接埠。

交换路由器设计人员现正面临增加连接端口密度、降低成本、减少功耗、以及缩小系统体积等重要考验。多端口千兆位以太网络 (Multi-port Gigabit Ethernet) 收发器便是针对这些问题而推出的一项重要进展,本文将深入探讨这类收发器在以太网络交换路由器设计中所扮演的重要角色。

图1:Gigabit以太网络讯号链

Gigabit以太网络可分为两大类,第一类收发器统称为1000BaseT收发器 (与IEEE802.3ab兼容的Gigabit以太网络铜线实体层组件),第二类收发器则是用来驱动SFP (Small Form Factor Pluggable) 以及GBIC (Gigabit Interface Converter) 等光模块的电路收发器组件,这些收发器通常称为Gigabit以太网络收发器,或Serdes (符合IEEE803.z标准)。本文将针对第二类收发器,及其对于现有系统设计的成本、功耗、和体积产生的重大影响做讨论。

设计人员必须了解,随着企业网络的10/100/1000BaseT连接埠数目不断加,Gigabit以太网络上行端口 (uplink port) 将成为路由器的主要技术瓶颈。交换路由器不仅需要更多个Gigabit以太网络上行端口,网络集线箱与数据中心也需要更大型的Gigabit以太网络交换器。

图2:光网连接埠的演进

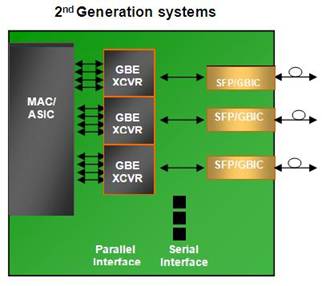

过去十年里,专门驱动光学上行端口的Gigabit以太网络收发器已从单端口组件演变成复杂的多端口系统单芯片。图3为Gigabit以太网络收发器在过去十年的演进过程。

图3:系统演进

图4可做为参考,它是Gigabit以太网络光纤连接端口的成长情形以及未来的成长预测。

图4:Gigabit以太网络光学连接端口数目的预测

从图4的图表看出,由于10/100/1000BaseT埠数不断增加,Gigabit以太网络交换路由器设计人员必须继续发展新技术来增加Gigabit以太网络的上行端口数目。

随着产品设计世代交替,交换路由器设计人员已开始处理或解决功耗、成本、和电路板面积等重要问题;这些问题会回过头来影响产品价格、扩充性、使用性、和服务能力等重要客户要求。

图5:重要的设计问题与要求

本文接下来的重点将放在如何选择Gigabit以太网络收发器以实现系统目标,并同时解决所有Gigabit以太网络交换路由器设计人员所面临的重要挑战。

选择正确的收发器

为应用选择Gigabit以太网络收发器时,由于发展多连接端口产品可能遇到庞大电源需求、功耗、以及有限的电路板面积等问题,因此交换路由器研发人员必须考虑许多因素。选择Gigabit以太网络收发器时,设计人员必须考虑界面 (并列和串行)、功耗、封装、和成本等四个关键领域。本文将针对此四领域逐一讨论。

一.界面

1.1 并列界面

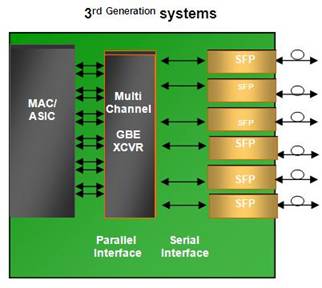

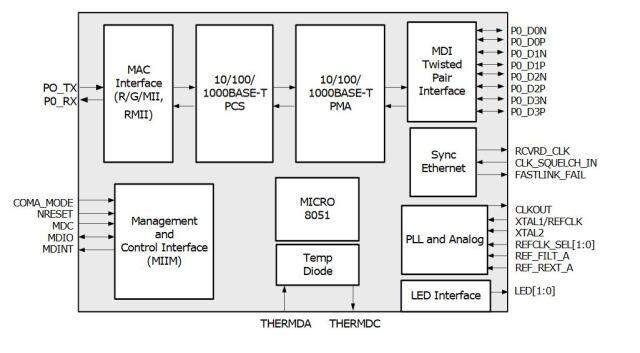

Gigabit以太网络收发器有许多需要设计人员深入考虑和选择的界面,包括并列数据界面、高速串行界面、和控制界面。Gigabit以太网络收发器的并列界面近来发展相当快速。过去许多年里,由于10位并列界面的设计和实作都很简单,因此成为Gigabit以太网络收发器的主要界面。10位界面 (Ten-Bit Interface,TBI) 是从Gigabit Media Independent Interface (GMII) 演变而来,而GMII则是由负责管理以太网络规格的标准机构所制定。

TBI/GMII界面采用LVTTL讯号位准,数据则由参考频率的上升边缘所控制。GMII界面与TBI界面的主要区别在于,GMII界面包含Physical Coding Sub-layer (PCS) 功能,而支持TBI界面的组件通常不会提供这些功能。选择TBI或GMII界面的关键在于所使用的媒体存取控制器 (MAC),以及这些媒体存取控制器是否内建所需的PCS功能,或者需要由收发器提供这些功能。

这些年来,TBI/GMII界面已逐渐被精简位界面 (reduced bit interface) 取代,这些界面会减少接脚总数和芯片面积,并同时提高连接端口密度。这项改变的主因在于设计人员需增加系统的连接端口数目,同时将相关的ASIC和MAC组件成本降至最低。Reduced Ten Bit Interface (RTBI) 以及 Reduced Gigabit Media Independent Interface (RGMII) 是目前应用最广泛的精简位界面。RTBI是传统10位界面的精简版本,它将原始并列位的宽度从8/10位减少至4/5位 (根据芯片是否执行8b/10b编码/译码来决定为8/10或4/5位);讯号位准则从LVTTL和SSTL2改变为HSTL。这些4/5位会以参考频率的上升和下降边缘做为控制,也就是说精简位界面只需要一半接脚,就能达到与传统10位界面相同的实际数据速率。接脚数目减半对于拥有24或48个Gigabit以太网络连接端口的系统有极大好处。

图6:精简位界面

RGMII主要用来担任TBI/GMII和RTBI的替代选项。它会在参考频率的上升和下降边缘利用四个控制讯号将数据多任务化,使I/O接脚的最大数目从23只 (TBI界面的并列端) 减少到12只 (包括控制接脚)。

设计人员为其应用选择界面时,必须仔细规划和了解讯号链;在做Gigabit以太网络收发器界面的MAC/ASIC设计时,更须如此。若设计人员的目标是尽可能增加Gigabit以太网络的连接端口数目,并维持系统体积不变,就应考虑采用某种精简位界面 (RTBI/RGMII)。

图7:精简位界面的接脚说明

讯号名称 RTBI RGMII 说明

TXC MAC MAC 随着速度不同,传送参考频率为125 MHz、25 MHz、或是2.5 MHz ± 50 ppm

TD[3:0] PCS MAC 在RTBI模式下,它在TXC上升边缘时包含位3:0,下降边缘时包含位8:5。在RGMII模式下,它在TXC上升边缘时包含位3:0,下降边缘时包含位7:4

TX_CTL PHY PHY 在RTBI模式下,它在TXC上升边缘时包含位5,下降边缘时包含位10。在RGMII模式下,它在TXC上升边缘时包含TXEN,下降边缘时包含TXEN和TXERR的逻辑微分值 (logical derivative)

RXC PHY PHY 连续性接收参考频率为125 MHz、25 MHz或2.5 MHz ± 50 ppm,并从其接收的数据串流产生

RD[3:0] PHY PHY 在RTBI模式下,它在RXC上升边缘时包含位3:0,下降边缘时包含位8:5。在RGMII模式下,它在RXC上升边缘时包含位3:0,下降边缘时包含位7:4

RX_CTL PHY PHY 在RTBI模式下,它在RXC上升边缘时包含位5,下降边缘时包含位10。在RGMII模式下,它在RXC上升边缘时包含RXDV,下降边缘时包含RXDV和RXERR的微分值

1.2 串行界面

Gigabit以太网络收发器目前所提供的高速串行界面可分为LVPECL (Low Voltage Pseudo Emitter Coupled Logic)、CML (Current Mode Logic) 以及VML (Voltage Mode Logic) 等三种讯号位准 (逻辑位准的比较请参考图8)。串行界面的选择过去是由收发器所连接的光模块种类来决定;现今设计则使用交流耦合的SFP光模块,这项考虑已不如I/O电力供应能力或终端匹配等因素来得重要。举例来说,德州仪器 (TI) 的新型收发器就采用内建终端匹配功能的VML技术。VML驱动器只要采用交流耦合方式,就能与LVPECL讯号完全兼容。

VML驱动组件采用CMOS制程技术,其优点在于不需要外接提升电阻,因为它们所采用的NMOS 和PMOS晶体管架构可同时驱动下降/上升讯号边缘。

不同逻辑位准的额定电压参数

参数 LVPECL CML VML LVDS

VOH 2.4 V 1.9 V 1.65 V 1.4 V

VOL 1.6 V 1.1 V 0.85 V 1 V

输出电压 (单端) 800 mV 800 mV 800 mV 400 mV

共模电压 2 V 1.5 V 1.25 V 1.2 V

图8:串行I/O的逻辑位准

选择正确串行界面所应考虑的主要因素:

- 对于功耗的整体冲击

- 对于实作的整体冲击

- 与光模块和电路模块的互用性

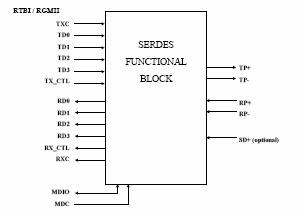

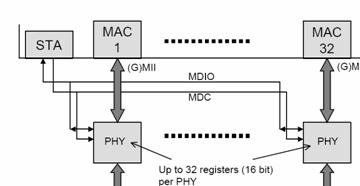

1.3 控制界面

随着芯片的连接端口不断增加,控制界面也开始从各埠独立的I/O接脚,演变成可靠的串行通讯总线。以太网络的串行通讯总线又称为Management Data Input Output (MDIO),它是由IEEE根据以太网络标准IEEE802.3的多项内容所定义 (第22条款)。MDIO为简单的双线式串行界面,它会将如微处理器的管理组件,连接到支持管理功能的收发器 (例如多端口Gigabit以太网络收发器或是10GbE XAUI收发器),以便控制接收器及搜集收发器传来的状态信息。MDIO能够搜集的信息包括:

- 链路状态

- 速度能力和选择

- 关机

- 省电休眠状态

- TX/RX模式选择

- 自动协商控制

- 回路模式控制

- 其它功能

除了IEEE要求的功能之外,收发器制造商还可自行增加其它的信息搜集功能。

图9:MDIO应用范例

设计人员在选择Gigabit以太网络收发器时,最好选择内建MDIO的组件,不要考虑未提供这个强大控制界面的产品。

二.功耗

功耗是选择Gigabit以太网络收发器的另一项重要考虑,几乎所有现代电子装置都很重视功耗。对于以太网络交换器和路由器来说,它更成为许多连接埠密集设计的主要考虑因素。虽然Gigabit以太网络连接端口密度持续增加,只要产品体积不变,其功率预算通常也会保持固定。基本上,设计人员必须把更多个连接埠挤进单一机壳内,并确保总功耗不变,或仅微幅增加。新型Gigabit以太网络收发器已能帮助设计人员解决这方面的部份困扰。在过去五年里,Gigabit以太网络收发器所采用的芯片制程已从BiCMOS/BiPolar转移到低功耗CMOS技术,使得每个埠的功耗从1 W减少到200 mW以下。

图10:功耗下降曲线

选择Gigabit以太网络收发器时,一个有用的经验规则是选择CMOS制程产品;这类组件的个别信道功耗约从200 mW到300 mW。制程技术进步使得组件所需电压降低,目前多数组件都能使用2.5 V或是1.8 V电源。

三‧封装

目前大部份的多通道收发器都采用大型PBGA封装,其接脚间距从1厘米到0.8厘米。图11为多信道和单信道组件之间的区别。

图11:多信道与单信道组件的面积比较

封装对设计所能提供的连接埠数目有极大影响。在Gigabit以太网络收发器的例子里,设计人员必须采用支持DDR并列信道模式的大型BGA封装 (如前所述) 才能达成设计目标。封装的选择应与电路板设计限制和整体系统架构一并考虑;比方说,BGA封装虽能缩小组件体积,但当其缩小到某个程度时,实作成本就会远超过增加连接埠所带来的好处。随着信道数目增加,组件也要采用更复杂麻烦的界面模式,因此今日的Gigabit以太网络收发器会在这些因素之间做出适当取舍。

选择今日的多信道Gigabit以太网络收发器时,最好选择300只接脚以下 (视组件所支持的连接端口数目而定)、接脚间距约为1厘米、以及组件面积小于20 × 20厘米的BGA封装。

四‧成本

每埠成本是设计人员在比较不同厂商所提供的Gigabit以太网络收发器时,所关心的重要因素。新型Gigabit以太网络收发器大都是以针对成本最佳化的CMOS制程技术发展而成。除此之外,封装技术的进步、以及封装代工市场的激烈竞争,也为市场带来更具成本竞争力的解决方案。今天,Gigabit以太网络收发器的每端口量产成本约从2.50美元到1.50美元。

其它直接影响成本的因素还包括实作成本 (外部零件)、电源管理需求、和散热管理需求 (散热片和风扇等)。除此之外,收发器的选择通常也会将ASIC/FPGA/MAC的发展目标列入考虑。因此工程师不应仅考虑Gigabit以太网络收发器成本,而要将整个设计 (ASIC和收发器) 的成本当成决策因素。

选择Gigabit以太网络收发器时,设计人员必须将整个讯号链纳入考虑,同时将主要设计目标当成零件选择的重要参考。

选择检查表:

1. 界面

- ASIC/FPGA的选择和研发

- 时序零件的选择和实作

- 控制机制

2. 电源:

- 电源层 (power plane) 设计

- 散热管理

3. 封装:

- 电路板设计

- 电路板布局

4. 成本:

- 系统整体可行性

- 实作成本

- 电路板总成本

就效能而言,所有Gigabit以太网络收发器都须达到IEEE要求,才能成为合格的Gigabit以太网络 (IEEE802.3z) 收发器。但只有效能达到标准,仍不足以在今日的市场上竞争;设计人员必须找出对其设计影响最大的其它区隔要素,例如功耗、体积、和成本等。

设计人员可以分析需要多个Gigabit以太网络连接端口的应用,以藉此了解在设计中采用新型多信道Gigabit以太网络收发器会产生的冲击。在此我们以24端口Gigabit以太网络交换路由器为例,然后比较单信道Gigabit以太网络收发器和多信道组件所造成的影响。

TI量产中的TLK2208A,与样品供应中的TLK2226是多信道Gigabit以太网络收发器的两个最佳范例。这两颗收发器组件的重要参数如下表所示:

|

|

TLK2208B

|

TLK2226

|

|

通道數目

|

8

|

6

|

|

並列界面

|

DDR-TBI

|

RTBI/RGMII

|

|

串列

|

VML

|

VML

|

|

接腳數

|

289

|

196

|

|

封裝

|

BGA

|

BGA

|

|

封裝大小

|

19 × 19釐米

|

15 × 15釐米

|

|

總功耗

|

1.2 W

|

1 W

|

图12:组件重要参数

在这个交换路由器的例子中,我们选择TLK2208B做为目标设计的收发器;其主要考虑在于节省电路板面积和降低功耗,并将ASIC界面的接脚数目减至最少。为了实作24埠解决方案,我们使用三颗TLK2208B来支持所有24个连接埠;相形之下,此设计若采用以前的单信道Gigabit以太网络收发器组件,整个解决方案就需要24颗收发器。从下图可看出,利用多信道Gigabit以太网络收发器实作这套解决方案,确实能省下可观的电路板面积。

图13:电路板使用面积比较

在这个例子中若使用八通道TLK2208B收发器,就能节省高达1,300平方厘米的电路板面积。除此之外,单通道解决方案可能还需要较大的组件间距和绕线面积,这将使其占用的总电路板面积增加。

大型多信道组件多半采用新型CMOS制程技术,其架构的工作效率也高于先前产品,因此新型Gigabit以太网络收发器设计在功耗方面自然占有优势。例如TLK2208B的每个通道功耗约为165 mW,传统单信道组件则从250 mW到600 mW (视技术而定);这表示相较于传统单通道收发器,TLK2208B之类的组件可将功耗减少35%到75%。

由于TLK2208B采用以上升边缘和下降边缘做为频率的精简位界面、共享式MDIO控制总线、和单一参考频率输入,因此它与MAC/ASIC的界面就比单通道解决方案更简洁、成本也更低。若产品发展包括设计新的ASIC组件,那么选择TLK2208B之类的组件就可能是唯一符合成本效益的ASIC实作解决方案。图14是利用单信道和多信道组件进行实作的接脚数比较。

|

使用元件

|

解決方案的接腳數目

|

|

3顆TLK2208B

|

867隻接腳

|

|

24顆64隻接腳的單通道收發器

|

1536隻接腳

|

图 14:接脚数比较

从图14可以看出,只要使用今日的多信道Gigabit以太网络收发器,设计人员就能发展更多连接端口的系统,并满足功耗更少、成本更低、和体积更小等需求。在许多情形下,多信道组件的节省幅度确实相当可观。

根据前述的各种范例,我们可以清楚看出,今日的多端口Gigabit以太网络交换器和路由器的设计并不容易。成功的数据通讯产品尤其如此,因为它们有众多变量需要考虑;其中之一就是驱动Gigabit以太网络光链路的Gigabit以太网络收发器。只要选择TI的TLK2208B和TLK2226等新型多信道Gigabit以太网络收发器组件,设计人员就可以:

- 减少系统总功耗

- 减少总电路板面积

- 减少I/O接脚数

- 减少ASIC界面复杂性

- 减少整体的实作风险

系统厂商可以利用这些优点,发展出更可靠和更具成本竞争优势的设计,以确保其产品获得更广泛接受,并在市场上创下更辉煌的成功记录。随着半导体技术不断进步,系统的连接端口数目不断增加, Gigabit以太网络收发器组件将成为设计工程师推动Gigabit以太网络连接端口快速成长的重要帮手。

电子发烧友App

电子发烧友App

评论