;两个全双工同步串行端口(运动型);四个定时器/计数器,三个支持脉宽调制;16个双向可编程标志I/O引脚;看门狗定时器;实时时钟;带1到31倍频器的片内锁相环。一般说明ADSP-BF535处理器

2020-10-15 17:59:27

82C54含三个独立的16位定时器,将T1和T2级联使用时,将T1的out接到T2的CLK,使用方式2计数,但是问题在于当t1由2变的的clk时钟下降沿时,out就输出触发T2减1,但是中断触发此时的数值,将会产生FFFF的差值,有什么好的解决办法吗

2015-06-08 14:47:25

定时器级联-频率 脉冲可控,驱动步进电机

2019-07-16 11:17:00

时钟系统概述定义时钟系统,它是由振荡器(信号源)、定时唤醒器、分频器等组成的电路。常用的信号源有晶体振荡器和RC振荡器。功能时钟是嵌入式系统的脉搏,处理器内核在时钟驱动下完成指令执行,状态变换等动作

2021-08-02 08:32:49

1、STM32时钟系统概述1.1 时钟系统的概念与意义概念时钟系统是由振荡器(信号源)、定时唤醒器、分频器等组成的电路。常用的信号源有晶体振荡器和RC振荡器。意义时钟是嵌入式系统的脉搏,处理器内核在

2021-08-12 07:16:57

采样,样片都必须在其速率的倍数下进行处理,而且要相位一致。这就需要一个“主”时钟,其可用来衍生系统中的所有其它时钟。您可使用温度补偿晶体振荡器 (TCXO) 和低相位噪声 PLL 实现这一点,可将主时钟

2018-09-13 14:18:06

AD9957工作在PLL模式下,PLL_LOCK为高。在单音模式下,设置FTW值输出30M,测试系统时钟频率为理论值436M,单音输出30M;设置FTW值输出100M,测试系统时钟频率为468M,单音输出107M。为什么,我刚改FTW的值,会影响到系统时钟呢?

2018-09-11 10:42:34

0000。 4. ARM启动代码设计 ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。启动代码一般包括: 中断向量表 初始化存储器系统 初始化堆栈初始化有特殊要求的端口

2020-11-17 16:13:49

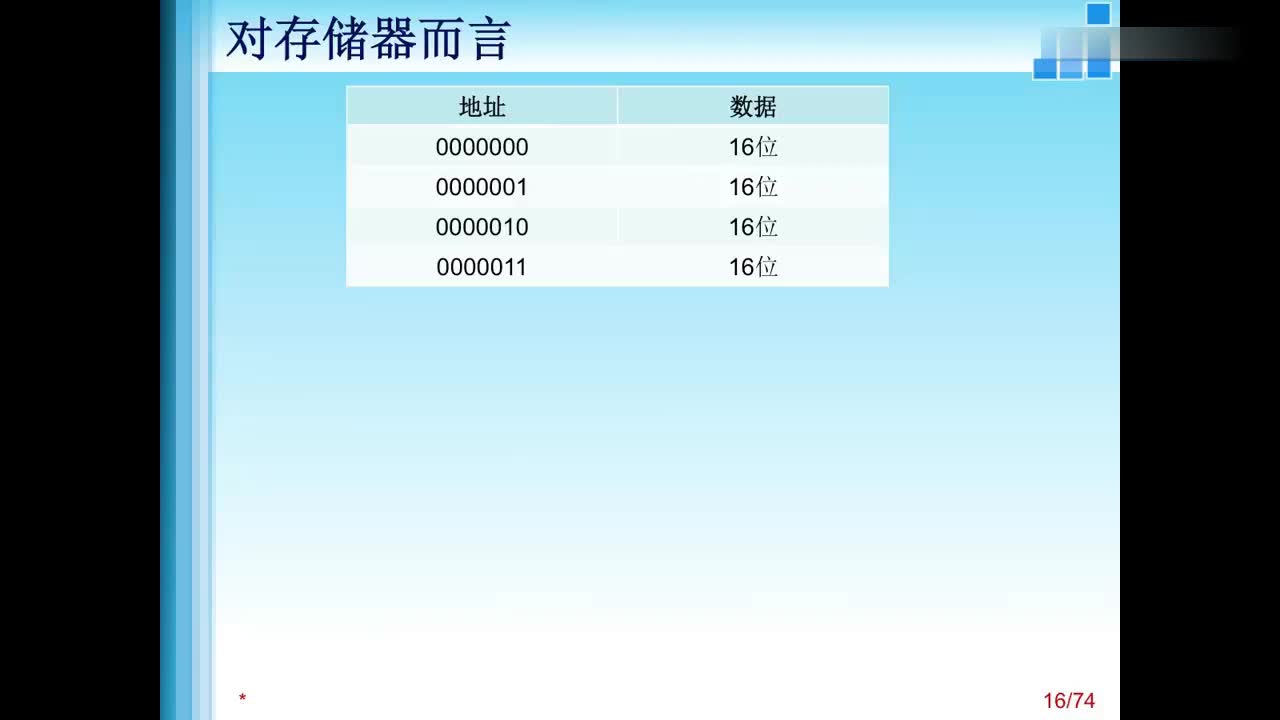

2.ARM微处理器的指令系统ARM微处理器的指令集是加载/存储型的,即指令集仅能处理寄存器中的数据,而且处理结果都要放回寄存器中,而对系统存储器的访问则需要通过专门的加载/存储指令来完成。ARM

2021-12-20 06:54:28

ATK-STM32F103ZE最小系统板 DEVB_50×80MM 5V

2023-03-28 13:05:53

所有使用Arm处理器的系统中都会包含一个标准化的通用定时器(Generic Timer)框架。这个通用定时器系统提供了一个系统计数器(System Counter)和一组定时器(Timer)。其结构

2022-04-22 10:23:43

噪声条件或软件错误而停止运行。如果配置为生成硬件重置,看门狗计时器将重置核心和处理器外围设备。复位后,软件可以通过询问看门狗定时器控制寄存器中的状态位来确定看门狗是否是硬件复位的源。计时器由系统时钟

2020-10-09 17:03:34

你好,我使用的芯片是C6747,定时器采用32位非链式模式实现定时功能。请问,定时器选择内部时钟源时,这个内部时钟源具体指的是PLL产生的哪一个系统时钟?这个内部时钟源指的是CPU时钟吗?谢谢

2018-08-01 09:39:51

成就更好的自己在吉林省电赛A题中用到了步进电机的控制,由于需要对步进电机的转速和转动角度都进行控制,因此博主想到了一种比较新奇的方法。目录方法简介与分析方法简介优劣性CubeMX的定时器级联配置内部级联

2022-01-06 07:00:16

怎样根据某些条件选择DSP处理器的类型?比如:要求数据输出时间间隔为1ms,速度数据类型为1个浮点型类型数据。急求大神指导!谢谢了!我对DSP处理器不太了解,暂时会用到这个技术。求指导!

2013-06-08 23:33:51

输出功能FLASH存储器通信类模块定时器模块最小系统参考设计文末彩蛋最小系统参考设计注意事项晶体可以同时使用高速XTH和低速XTL,不使用时晶体端口可用做GPIO或其他复用功能;BOOT0上电时为高电平

2021-09-22 10:48:49

输出功能FLASH存储器通信类模块定时器模块最小系统参考设计更多信息咨询请联系angel.qi:***(微信与手机号码同步)文末彩蛋最小系统参考设计注意事项晶体可以同时使用高速XTH和低速XTL,不使

2021-09-14 15:09:41

普遍认为开发多处理器系统软件的难度要大于单处理器系统。但实际情况并非总是如此。我们这个在 TRW 汽车公司下属的咨询部 TRW Conekt 工作的设计团队最近接管了一个项目,展示了如何根据手中的问题发挥硬件的功能,并通过使用许多个处理器开发出高效系统。

2019-10-23 08:00:03

只是一个很快的问题:我用Proteus VSM来模拟PIC18F2550,用MikroC编译的HEX文件。MCU用4 MHz的外部晶体操纵。处理器运行在32兆赫(96兆赫PLL / 3)。现在我

2020-03-17 07:17:56

STM32定时器级联功能怎么实现?

2021-11-24 06:40:04

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2016-06-18 09:21:59

是嵌入式系统的脉搏,处理器内核在时钟驱动下完成指令执行,状态变化等动作,外设部件 在时钟的驱动下完成各种工作,比如串口数据的发送,A/D转换,定时器计数等等。因此时钟对于计算机系统是至关重要的,通常时钟系统出现问题也是致命的,比如振荡器不起振、震荡...

2021-08-12 07:16:05

STM32最小系统主要由STM32F103RCT6微处理器、时钟晶振电路、按键复位电路、电源稳压电路以及BOOT电路等部分构成,该最小系统所使用的微处理器是一款32位的处理器,该处理器基于高性能

2021-08-13 07:36:34

电路在系统设计中JTAG的主要作用是将目标文件烧录下载到处理器中。本次设计具体JTAG电路原理如图所示:系统JTAG电路原理图4.启动模式电路BOOT0、BOOT1端口电平的不同设置,可以对三种不同启动

2018-11-20 21:09:39

:HSI,HSE 和 PLL。在我们实际应用中,因为对时钟速度要求都比较高我们才会选用 STM32F4 这种级别的处理器,所以一般情况下,都是采用 PLL 作为 SYSCLK时钟源,而系统时钟配置不正确就是PPL这里出了问题。先看一下主PPL在整个时钟树中间的位置。高速系统时钟一般由PPL_P提供,一般配

2021-08-10 07:16:13

使用单个外部时钟来获得Clk和Clk / 1.001速率,但这需要一长串DCM和PLL。特别,27 MHz外部CLk- > DCM0- > DCM1- > PLL0产生74.25

2019-07-23 14:02:15

OTG模块以不同频率工作,同时使用POSC作为时钟源。为了防止缓冲区溢出和定时问题,CPU内核必须被时钟控制在最小16MHz。16Mhz应该足够,但不能用40Mhz。我猜想和谐在中断处理中增加了很多

2019-09-11 14:16:30

本文通过基于S3C44B0X处理器VxWorks嵌入式操作系统的BSP移植,详细分析了VxWorks操作系统基于ARM处理器的中断处理方法。

2021-04-27 06:28:03

我有一个设计,我使用2个时钟域,用MMCM创建(我需要一个级联来获得我需要的确切频率)。我已将'处理器系统复位'模块连接到clk_out1和clk_out2时钟输出,因此每个域都会正确复位。我(想

2019-04-22 06:10:43

我怎么知道?我想做的网格接口PLL。我是否去FordSP33 EP256MU810系列?ISDSP33 EP256MU810是浮点型处理器。

2020-04-27 06:09:07

本实例系统是一个简单的微处理器设计(你可以按照自己的需求配置处理器)。它包含以下内容:•单个Cortex-M3或Cortex-M4处理器。•内部程序存储器。•SRAM数据存储器。• Boot

2022-01-21 07:24:54

Teledyne e2v为系统设计师提供的定制方案处理器功耗的背景知识三种调整处理器系统功耗的方法

2021-01-01 06:04:09

吗?为什么PLL需要在不同的时钟区域?时钟发生器仅需要1个PLL和MMCM,不使用其他时钟资源。我应该手动限制PLL吗?这个怎么做?我在Kintex 7上有类似的设计,相同的时钟发生器我没有这个错误,我认为Kintex和Artix之间的时钟资源相似

2020-07-20 12:51:25

在图形理方面有一定的优势,但是成本极高,并且系统部分效率低下,不适合功能拓展。ScenSmart采用基于ARM处理器的纯硬件视频融合拼接系统,可有效解决这些行业痛点。目前RK3588、RK3399

2022-07-18 16:51:55

一块STM32处理器至少都有一个PLL,有的甚至有好几个PLL。比如,F4有两个PLL:F7有三个PLL:当然,每个MCU型号不同,其PLL数量,及功能也有差异,具体需要

2020-05-18 07:00:00

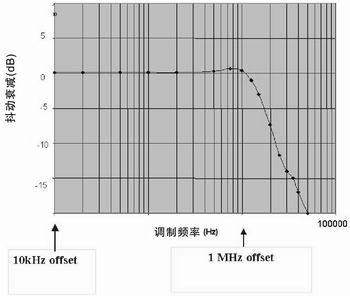

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

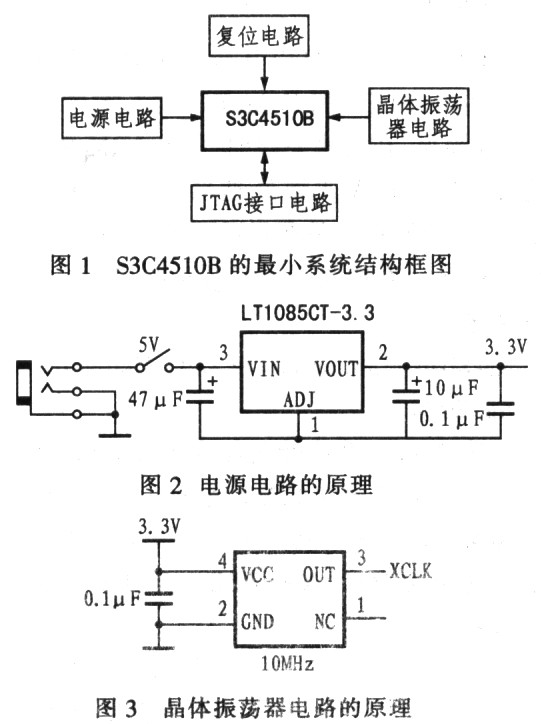

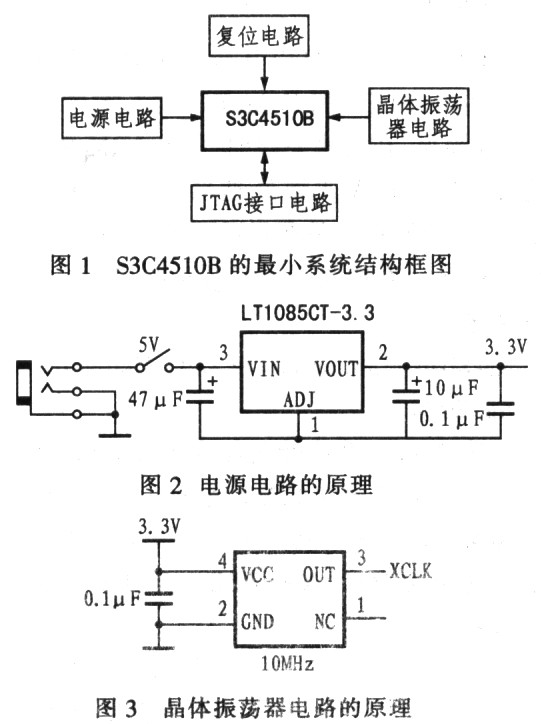

32位定时器;18个可编程I/O口;1个含有21个中断源的中断控制器和1个PLL电路。3 硬件设计3.1 最小系统设计最小系统是由保证微处理器可靠工作所必须的基本电路组成的。S3C4510B的最小系统

2011-11-25 10:03:34

基于微处理器的电池检测系统设计

2021-03-11 06:09:12

低功率模式经常被忽视而没有得到利用。有了现在的高性能嵌入式处理器,“开”或“关”不再是一个问题。新的处理器可有多个状态,如运行、打盹、小睡、睡眠以及深度睡眠模式等,每种状态下对处理器时钟、PLL以及

2019-07-15 06:40:13

的时钟生成单元会最先工作,这时候处在参考时钟ref_clk下(通常是10-100MHz),待到PLL输出稳定后,时钟生成单元会把给处理器的时钟切换到正常工作频率,并释放处理器的复位信号,通常我们称这个复位

2022-06-07 16:41:29

处理器。通过在两个执行内核之间划分任务,多核处理器可在特定的时钟周期内执行更多任务。 多核技术能够使服务器并行处理任务,多核系统更易于扩充,并且能够在更纤巧的外形中融入更强大的处理性能,这种外形所用

2019-06-20 06:47:01

的各个领域。采用INMOS公司的IMS A100级联型信号处理器为模板,以FIR滤波器设计为核心,用FPGA技术开发设计级联型信号处理器,能够应用于数字FIR滤波、高速自适应滤波、相关和卷积、离散

2019-07-30 07:22:48

十几年前,频率控制行业推出了基于锁相环(PLL)的振荡器,这是一项开拓性创新技术,采用了传统晶体振荡器(XO)所没有的多项特性。凭借内部时钟合成器IC技术,基于PLL的XO可编程来支持更宽广的频率

2019-07-31 06:49:45

针对汽车数字信号处理应用的各种处理器类型,有什么优缺点?如何选择汽车电子系统中的处理器?

2021-05-14 06:59:41

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2017-04-15 11:56:58

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2017-05-05 14:34:19

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2018-09-25 11:38:18

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2014-05-13 10:10:50

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2016-05-23 10:27:23

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2016-08-23 10:31:08

和DMA使用的HCLK时钟。②、通过8分频后送给Cortex的系统定时器时钟。③、直接送给Cortex的空闲运行时钟FCLK。④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出

2016-08-25 09:40:03

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的倍频系数配置好。整个时钟的配置流程如下所示:(1

2021-08-23 09:12:44

随着嵌入式系统在消费电子和工业设备中的广泛应用,功耗已经开始像时钟速度和系统性能一样成为微处理器的一个核心特性。为了确定各种微处理器的功耗效率,嵌入式微处理器基准协会开发了一个有力的工具

2019-08-22 07:30:54

来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。 2.2 门控时钟和可变频率时钟 如图1所示,在微处理器中,很大一部分功耗来自时钟。时钟是惟一

2016-06-29 11:28:15

基于CPLD的三相五电平变频器PWM脉冲发生器的原理是什么基于CPLD的级联型多电平变频器脉冲发生器的设计

2021-05-08 06:18:39

可编程控制处理器的最小系统应包含什么?怎样去搭建一种RK3288最小系统电路呢?

2022-03-03 08:45:18

为什么有的处理器可以跑操作系统,有的不能?(专业一点的回答)

2012-09-04 16:08:44

一种改进的级联型多电平变换器拓扑

2019-05-15 11:37:05

求大神分享一种基于FPGA的级联结构FFT处理器的优化设计

2021-05-06 07:34:53

引言 随着数字信号处理(DSP)技术的迅猛发展,以数字信号处理器及相关算法为技术的数字降噪声技术也不断出现。本文提到的JK-DP50型数字降噪声处理器就是应用数字信号处理器DSP技术及高速实时处理

2019-07-04 06:03:56

的时钟生成单元会最先工作,这时候处在参考时钟ref_clk下(通常是10-100MHz),待到PLL输出稳定后,时钟生成单元会把给处理器的时钟切换到正常工作频率,并释放处理器的复位信号,通常我们称这个复位

2022-07-19 15:00:47

。 ②通过 8 分频后送给 Cortex 的系统定时器时钟,也就是 systick 了。 ③直接送给 Cortex 的空闲运行时钟 FCLK。 ④送给 APB1 分频器。 APB1 分频器输出一路供

2018-04-28 13:12:28

STM32时钟系统是什么意思?STM32时钟系统有什么意义呢?SysTick定时器的工作原理是什么呢?如何去实现对SysTick定时器的初始化呢?

2021-11-22 07:37:04

请问,想通过FPGA的PLL倍频产生个500MHz的时钟来使用,以此时钟来做定时精密延迟,不知道PLL倍频倍数有什么要求,比如好像有的器件支持不到500MHz,有没有可推荐的器件呢

补充内容 (2017-1-4 09:26):

或者有大神用过类似能到500MHz的FPGA推荐么

2017-01-03 17:04:23

怎么设计一种级联型多电平变流器?级联型多电平变流器具有哪些特点?基于STS—SVM的三相级联型多电平变流器有什么技术特点?

2021-04-14 06:48:51

怎样设计FIR滤波器结构?怎样设计级联型信号处理器?如何对级联型信号处理器进行仿真测试?

2021-04-28 07:04:01

寄存器的200 MHz时钟,我试图使用时钟向导获得超过900 MHz的单端但没有帮助我的问题是我能从PLL,DCM或级联PLL DCM获得多大的输出频率限制? ,甚至可以从PLL或DCM获得1.2 GHz?我将衷心感谢您的帮助问候,Morlerm

2019-08-02 06:10:13

音频系统对处理器芯片有什么要求?

2021-06-03 06:03:34

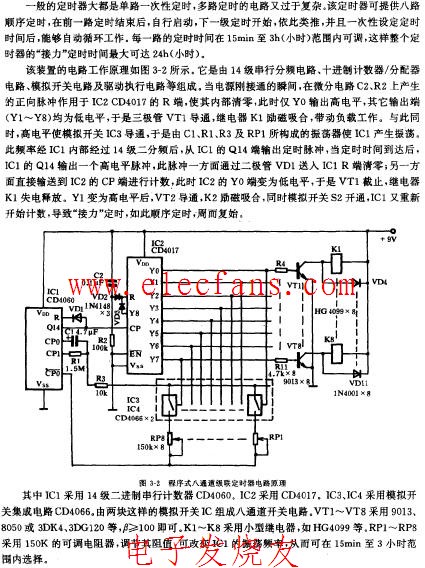

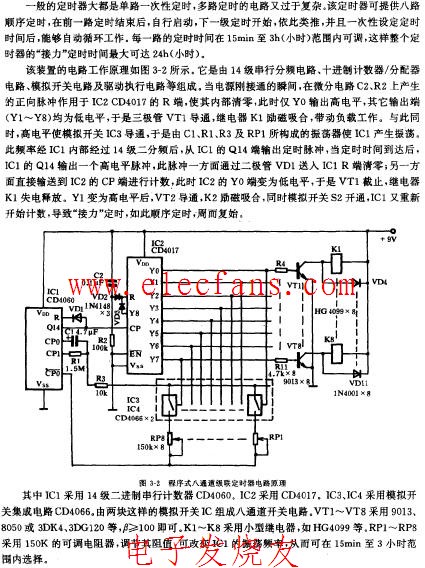

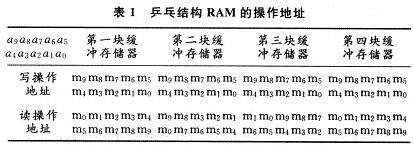

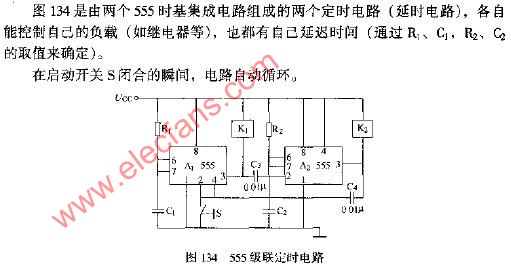

程序式八通道级联定时器

2008-08-10 23:04:10 2474

2474

基于FPGA的级联结构FFT处理器的优化设计

0 引 言

数字信号处理主要研究采用数字序列或符号序列表示信号,并用数字计算方法对这些序列进行处理,以便

2009-12-28 11:07:33 1865

1865

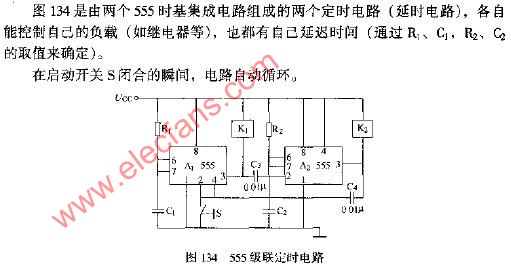

555级联定时电路图

2010-03-30 15:13:36 643

643

本文介绍S3C4510B型ARM微处理器最小系统的构建,并给出系统外围相关器件的选型。

2011-08-19 14:33:08 2778

2778

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17:00 6066

6066

你会担心STM32时钟PLL各参数配错吗?

2020-03-01 13:35:13 3031

3031 本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 设计是基于嵌入式技术作的最小系统设计,一个嵌入式处理器自己是不能独立工作的,必须给它供电、加上时钟信号、提供复位信号,如果芯片没有片内程序存储器,则还要加上存储器系统,然后嵌入式处理器芯片才可能工作。这些提供嵌入式处理器运行所必须的条件的电路与嵌入式处理器共同构成了这个嵌入式处理器的最小系统。

2020-10-28 16:54:29 16

16 EE-261:了解基于PLL的处理器的抖动要求

2021-04-23 14:39:28 10

10 EE-290:管理SHARC®处理器上的核心PLL

2021-05-20 14:49:15 2

2 PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 三款跟控制器/处理器相关的器材: 嵌入式开发系统板 TI MCU系统板 - 毕竟TI是赞助商,有一道题目中指定要用到TI的产品 微处理器最小系统板 不谈TI的MCU系统板,那还有嵌入式开发系统板和微处理器最小系统板,从纸面上理解,这二者还是有一定的差异的

2021-08-10 15:59:16 3062

3062 最小系统1,、供电电路2、复位电路3、时钟:外部晶振(2个)4、Boot启动模式选择5、下载电路(JTAG)6、后背电池时钟详解:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE

2021-11-17 15:36:02 12

12 华大HC32-(02)-系统时钟和基本定时器

2021-11-23 18:06:41 29

29 系统时钟配置错误而产生的串口定时器等问题在 STM32 中,有五个时钟源,为 HSI、HSE、LSI、LSE、PLL。从时钟频率来分可以分为高速时钟源和低速时钟源,在这 5 个中 HIS,HSE

2021-11-23 18:21:38 9

9 系统的心跳时钟。这样可以节省MCU资源,不用浪费一个定时器。比如uCOS中,分时复用,需要一个最小的时间戳,一般在STM32+UCOS系统中,都采用Systick做uCOS心跳时钟。Systick定时

2021-12-31 19:46:43 15

15 为什么使用STM32F1定时器的级联,主要是因为某些对于计时要求高的场合,而STM32F1单片机16位的定时器最多计数65535,那么很明显us级别的计时只能维持6.5535ms,有时候解算过程可能

2022-01-17 09:34:11 12

12 介绍S3C4510B型ARM微处理器和基于该处理器设计的最小系统,概述该系统外围应用电路的选型,以便使用者自行设计开发。

2023-07-23 15:17:02 495

495

景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319

电子发烧友App

电子发烧友App

评论