1 概述

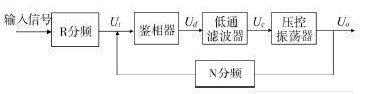

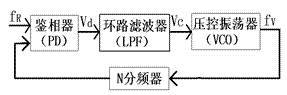

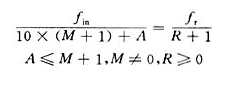

频率合成技术是近代无线电技术发展中的一门新技术,也是现代通信系统中的关键技术之一,它通常利用一块晶体或少量晶体组成标准频率源,然后通过合成方法产生各种所需的频率信号。这些频率信号与标准频率源具有相同的频率稳定度和准确度。使用该技术构成的电路在通信设备中称为频率合成器。频率合成器的种类很多,目前普遍采用的是数字式频率合成器。数字式频率合成器由晶体振荡器、固定分频器、鉴相器、滤波器和VCO等组成, 晶体振荡器输出的频率信号经固定分频器后得到标准频率,而VCO输出的频率信号经可变分频器分频后得到实际频率信号,两信号在鉴相器中经相位比较产生的环路锁定控制电压将通过滤波器加到VCO上,以对实际频率信号进行控制和校正,直到环路锁定。当所需信号频率较高时,该电路的设计、制作和调试难度较大,通常只能依靠专业厂家来完成,不仅成本高,而且生产周期长。TSA5526芯片是Philips公司推出的通用数字频率合成集成电路,它将晶体振荡器、固定分频器、鉴相器、滤波器等电路集成在一块芯片上,其主要特性参数如下:

晶体振荡器输出的频率信号经固定分频器后得到标准频率,而VCO输出的频率信号经可变分频器分频后得到实际频率信号,两信号在鉴相器中经相位比较产生的环路锁定控制电压将通过滤波器加到VCO上,以对实际频率信号进行控制和校正,直到环路锁定。当所需信号频率较高时,该电路的设计、制作和调试难度较大,通常只能依靠专业厂家来完成,不仅成本高,而且生产周期长。TSA5526芯片是Philips公司推出的通用数字频率合成集成电路,它将晶体振荡器、固定分频器、鉴相器、滤波器等电路集成在一块芯片上,其主要特性参数如下:

●输入射频信号的频率为:64~1300MHz;

●输入射频信号的电平为:-28~3dBm;

●输出误差调整电压为:4.5~33V;

●具有锁定检测功能;

●内置可编程的15bit分频器;

●通过程序控制可在512、640和1024中选择基准信号分频比,在外接4MHz晶振时,则可获得3.90625kHz、6.25kHz和7.8125kHz的频率精度;

●可选择I2C总线和3总线进行数据传输;

●采用单电源供电,电源电压为4.5~5.5V。

2 引脚功能

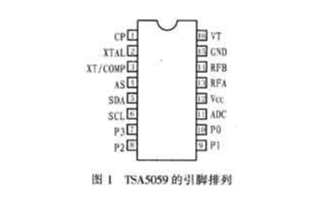

TSA5526有SSOP16和SO16两种封装,引脚排列如图1所示,各引脚功能见表1所列。

表1 TSA5526的引脚功能

| 引 脚 | 名 称 | 功 能 |

应 用 说 明 |

| 1 | RF | 射频信号RF输入 | 通常接本振输出 |

| 2 | VEE | 地 | |

| 3 | VCC1 | 电源电压1 | 芯片电源,接+5V |

| 4 | VCC2 | 电源电压2 | 开关控制电源,通常接+12V |

| 5 | BS4 | 电子开关BS4输出 | PNP三极管OC输出 |

| 6 | BS3 | 电子开关BS3输出 | PNP三极管OC输出 |

| 7 | BS2 | 电子开关BS2输出 | PNP三极管OC输出 |

| 8 | VS1 | 电子开关BS1输出 | PNP三极管OC输出 |

| 9 | CP | 环路滤波器 | 外接RC滤波网络 |

| 10 | Vtune | 误差控制电压输出 | 通过上拉电阻输出直流电压并加到VCO |

| 11 | SW | 总线选择开关 | 接地时选择I2C总线方式;悬空时选择3总线方式 |

| 12 | LOCK/ADC | 锁定标志/ADC输入 | 3总线方式时为锁定标志,低电平有效;I2C总线方式时5为电平ADC输入端 |

| 13 | SCL | 串行时钟 | 下降沿时将SDA输出的数据锁存 |

| 14 | SDA | 串行数据 | 在3总线方式时, 18bit、19bit和27bit三种数据可供选择 |

| 15 | CE | 片选信号 | 高电平有效 |

| 16 | XTAL | 基准振荡输入 | 通常外接4MHz晶体 |

表2 写状态数据格式

| 字 节 | MSB | 数据字节 | LSB | |||||

| 地址字节(ADB) | 1 | 1 | 0 | 0 | 0 | MA1 | MA0 | |

| 分频字节(DI1) | 0 | N14 | N13 | N12 | N11 | N10 | N9 | N8 |

| 分频字节2(DB2) | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0 |

| 控制字节(CB) | 1 | CP | T2 | T1 | T0 | RSA | RSB | 0S |

| 电子开字节(BB) | 空 | 空 | 空 | 空 | BS4 | BS3 | BS2 | BS1 |

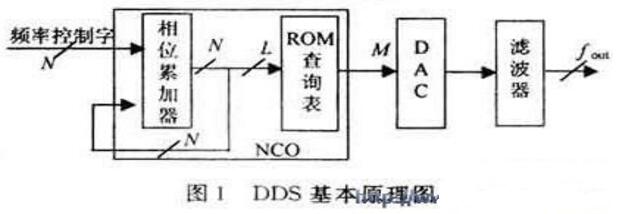

3 内部结构和工作原理

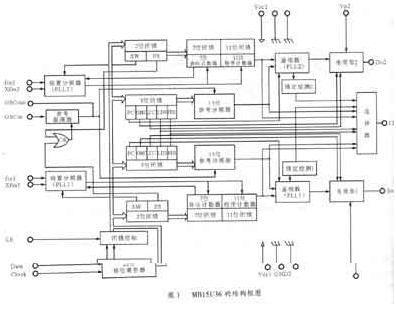

TSA5526的内部结构框图如图2所示,它包括射频信号处理单元、基准信号处理单元、相位比较和输出单元以及接口控制单元等四部分。射频信号处理单元对输入的射频小信号进行放大和8分频,再送到15bit可编程分频器,分频比的大小可根据输入射频信号的频率来确定。基准信号处理单元中的基准振荡器通过外接晶体产生基准信号,同时经基准分频器产生基准信号。基准分频器通过编程可选512、640和1024三种分频比。经过分频处理后的两路信号同时加到数字式相位比较器,然后经电荷泵、放大器和驱动三极管后得到误差控制电压输出。接口控制单元用于实现微处理器与该器件的通信,它一方面接收微处理器送来的数据并在内部处理以形成各种控制指令;另一方面将本器件的状态送往微处理器。通过SW端信号的不同连接,可选择两种串行通信方式:I2C总线方式和3总线方式。

图2

3.1 I2C总线方式

a. 写状态?R/W=0?

在写状态时,对TSA5526编程需要四个数据字节,并应在地址字节传输后将数据字节送入芯片。当地址字节?第一字节?传输后,I2C总线的收发会使地址字节和数据字节连在一起,并在一个传输过程中传输完毕。如果地址字节后的第一个数据字节为分频字节或控制字节,则芯片将被部分编程。表2是其数据字节定义。表中,MA1和MA0是可编程地址位,用于控制加到片选端的电压。N14~N0为可编程分频比,其分频比为:

N=N14×214+N13×213+…+N1×2+N0

CP为控制电荷泵电流大小位,CP为0,对应电流为60μA,CP为1时,电流为280μA?缺省值?。T2~T0代表测试位。RSA和RSB为基准分频比选择位。0S为可调放大器控制位,0S位为0时,可调放大器接通?缺省值?,0S位为1时断开。BS4~BS1是PNP电子开关控制位,其对应关系是:当BSn为0时,电子开关n接通;当BSn为1时,电子开关n断开。

表3 读状态数据格式

| 字节 | MSB | 数 据 字 节 | LSB | |||||

| 地址字节 | 1 | 1 | 0 | 0 | 0 | MA1 | MA2 | R/W=1 |

| 状态字节 | POR | FL | ACPS | 1 | 1 | A2 | A1 | A0 |

表4 3总线方式数据格式

| 数据形式 | D0D3 | D4D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 |

| 18位 | BS4BS1 | N13N0 | |||||||||

| 19位 | BS4BS1 | N14N1 | N0 | ||||||||

| 27位 | BS4BS1 | N14N1 | N0 | - | CP | T2 | T1 | T0 | RSA | RSB | 0S |

b.读状态?R/W=1?

表3所列为读状态数据格式。当辅助地址位被识别之后,将自动产生一个响应脉冲到SDA线上。SDA线上的数据在SCL时钟信号为高电平时有效,数据字节在SDA线上产生应答信号之后从器件中读出;如果没有主应答信号产生,传输过程就会结束,此时芯片将释放数据线从而使微控制器产生终止条件。当上电时,POR标志被置为1,当检测到数据结束标志时,POR标志被复位?读周期的结束。FL为进入锁存标志,用于表示何时循环建立起来。通过对FL置1或清零可对循环进行控制。ACPS为自动充电电流转换标志,当自动充电电流转换打开且循环锁定时,此标志为0,此时充电电流被强制为低。在其它条件下,ACPS为逻辑1。在I2C总线状态下,内置的A/D转换器可将自动频率微调模拟电平转换成数字量并送往微控制器。

3.2 3总线方式

在3总线方式下,该器件接收的数据有18位、19位和27位三种,参见表4。在该方式下,当片选引脚CE由低电平变为高电平时,SCL引脚输入时钟脉冲的下降沿会将SDA引脚上的数据送入数据寄存器,数据的前四位用来控制电子开关的通断,在第五个时钟脉冲的上升沿,这四位数据被送入内部电子开关控制寄存器。如果传输的是18或19位数据字,那么,在片选线上电平由高向低转换时,频率位将被送入频率寄存器。在上电复位状态下,电荷泵电流为280μA,调谐电压输出被关断;而在标准模式下,当ACPS标志为高电位时,测试位T2~T0被置为001,此时将禁止TSA5526输出。当传输的是27位数据字时,在时钟脉冲的第20个上升沿到来时,频率位将被送入频率寄存器,而控制位则在片选引脚CE从高电平向低电平转换时送入控制寄存器。在这种方式下,基准分频比由RSA和RSB位确定,测试位(T2、T1、T0)、电荷泵控制位CP、分频比选择位(RSA、RSB)以及0S位只能进行27位的传输。图3所示是3总线方式时的时序图。

表5 AT89C51内RAM中20H、21H、22H、23H的定义

| 字节地址 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 20H | BS4 | BS3 | BS2 | BS1 | N14 | N13 | N12 | N11 |

| 21H | N10 | N9 | N8 | N7 | N6 | N5 | N4 | N3 |

| 22H | N2 | N1 | N0 | 1 | 1 | 0 | 0 | 0 |

| 23H | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

4 应用

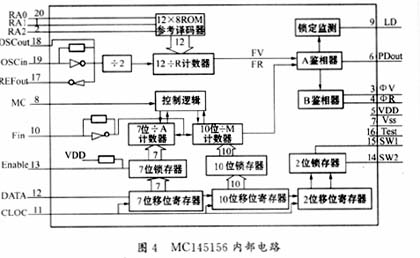

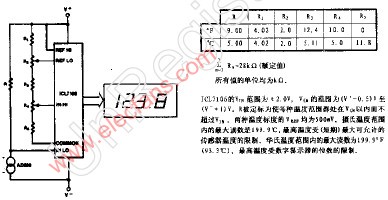

TSA5526在某航空电子设备检查仪中的应用电路如图4所示,图中,单片机与TSA5526采用3总线方式进行通信。P1.0与SCL引脚相连,用于串行时钟输出。P1.1与SDA引脚相连,用于串行数据输出。P1.2与CE引脚相连以进行片选控制;电子开关BS1~BS4用于通过VCO产生4种不同频率信号,VCO的输出将通过C6送到TSA5526的RF引脚,并经分频后与基准信号进行相位比较。Vtune输出的误差控制电压经电阻R3、电容C5加到VCO。R1、C4的数值可用于决定微调的快慢。当频率锁定后,LOCK引脚将变为低电平,并将该电平通过AT89C51的P1.3引脚送入单片机进行检测。本电路采用27位数据格式,发送的数据存放在单片机AT89C51中RAM的20H、21H、22H、23H四个单元中,各位定义见表5所列。其具体程序清单如下:

Rfegadj: CLR P1.0

SETB P1.2

MOV R0,#08H

Fregadj1: MOV A,20H

CLR C

RRC A

MOV P1.1,C

SETB P1.0

NOP

CLR P1.0

DJNZ R0,Fregadj1

MOV R0?#08H

Fregadj2: MOV A,21H

CLR C

RRC A

MOV P1.1,C

SETB P1.0

NOP

CLR P1.0

DJNZ R0,Fregadj2

MOV R0,#08H

Fregadj3:MOV A,22H

CLR C

RRC A

MOV P1.1,C

SETB P1.0

NOP

CLR P1.0

DJNZ R0,Fregadj3

MOV R0,#03H

Fregadj4: MOV A,23H

CLR C

RRC A

MOV P1.1,C

SETB P1.0

NOP

CLR P1.0

DJNZ R0,Fregadj4

RET

电子发烧友App

电子发烧友App

评论