软件无线电(SDR)在80年代后期,从先进的军事和智能应用转向卫星和蜂窝系统,并将成为消费应用的主流,这包括蜂窝无线电基站、新一代数字VHF系统、汽车用多波段AM/FM/XM卫星无线电等。

软件无线电是信号链路部分为软件的无线电。它具有如下特性:

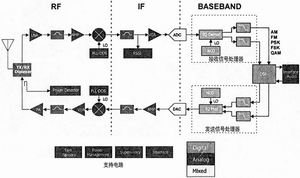

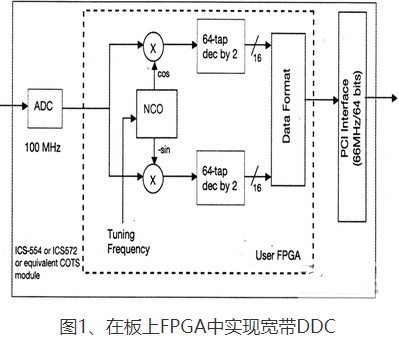

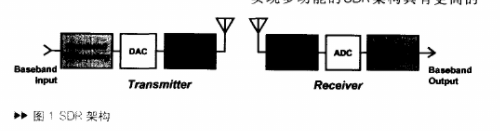

图1示出一般软件无线电框图。

可以用模拟或数字形式实现很多功能,但是要在元件的可用性、复杂性和成本问题折衷考虑选择方案。

典型的软件发送器元件包括:

软件接收器元件包括:

问题是要设计尽可能完善的线性不随时间变化的发送和接收器硬件,使系统能提供一个“干净”的输入信号到数字信号处理硬件,这样,在软件控制下一个通用信号链路可用于所有工作模式。

也就是说,接收器结构依赖于ADC的选择,ADC决定可用的动态范围。

单个ADC可过取样或欠取样被调制的信号,在处理中执行下变频并用4x取样提供I和Q输出。

然而,取样频率越高,孔经误差效应就越大,由于时钟抖动,会影响有效位数。因此,在速度和分辨率间总是存在固有的折衷考虑。

单ADC可在带数控振荡器(NCO)的数字下变频器之后实现如FPGA或接收信号处理器(专用数字芯片)的功能,在信号到达DSP解调前也可滤波和分样。

图1 软件无线电框图

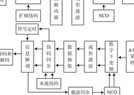

图2 建立恢复时间、相位和幅度所必须的软件

相比,用一个带模拟基带同相(I)和正交(Q)输出的模拟解调器减轻ADC上的负担并允许另外对基带的无源滤波来降低所需的动态范围。

其缺点是会导致正交不稳定性,这是由于I和Q通道中相位和幅度失配的原因。也需要两个匹配的抗混淆滤波器(可加倍做为通道滤波器)和匹配的ADC(或匹配的S/H放大器和单个ADC)。

另一个设计折衷考虑是在模拟和数字滤波之间。无源模拟滤波器具有低互调失真而且不耗电,但它有组合延迟,占有显著的板空间(特别在低频)以及要折衷考虑成本、带宽和Q值。

数字滤波器可设计成具有接近于理想的性能,但也得考虑速度—功率折衷,更多的抽头或更高的工作频率需要DSP更高的MIPS、FPGA中专用硬件或接收信号处理器(可提供下变频、分样和滤波)。

ADC的动态范围是模拟和数字滤波之间的基本折衷考虑:模拟滤波更多地降低ADC所需的动态范围,而且无源滤波器不耗电,而数字滤波器更增加ADC所需的动态范围,但数字滤波器可具有接近于理想的特性。

对于线性系统,ADC必须适应所有希望的信号加干扰加衰减容限以及自动增益控制(AGC)响应时间。确定ADC动态范围的计算必须包括:

通常,宽带接收器比窄带接收器含有更宽的ADC动态范围和较小的总增益(~35dB)和较窄的AGC范围(~10dB)。

系统设计也包括级联噪声指数和监听分析以及频率规划。频率规划是一种技巧,设计人员必须仔细选择系统时钟、中频和本地振荡器频率,使内部和外部干扰最小。

不关注系统时钟将是不完整的频率规划。系统时钟通常是编码数据帧率的倍数。往往也是信道间隔的倍数,允许使用整数N锁相环(PLL)。

一个完整的设计也包括用于最小和最大输入信号电平的总系统计算,最小输入信号的一组计算是在AGC关掉无增益降低情况下进行,最大信号电平的一组计算是在AGC完全工作在最大增益降低情况下进行。这也包括最小和最大信号电平的交互调制失真(IMD)效应。

系统设计的一个敏感点是AGC系统。在软件无线电中,AGC靠降低大信号的增益来保持系统线性度。这样设置AGC阈值:C/N增加线性度,直到达到最佳C/N为止,然后,降低增益。

所设置的AGC阈值也应使ADC有余量,这样AGC系统有时间来响应输入信号的快速变化并避免过载。AGC有两种基本实现方法:前馈和反馈。

AGC实现

典型的前馈AGC系统用对数放大器测量输入信号(通常在中频)并置下游增益来保持在AGC中的恒定信号电平。这是最快的响应系统,但需要定标,这是由于它依赖于对数放大器和可变增益放大器定标因数(dB/v)的精度。

典型的反馈AGC系统对被检测信号与基准进行比较,并用反馈来保持被检信号电平恒定。系统应具有快速起动(增益降低)和慢速(增益增大)AGC时间常数。对于稳定的环路它需要线性dB增益。信号通路等待时间可允许接收器被强信号封闭。

例如,用带峰值检测器(在IF)的模拟AGC在反馈有效前用几个周期充电AGC电容器。

用基带中的检测器并从I和Q基带值计算信号电平值,但等待时间比IF所希望AGC的值更坏,特别是在DSP中计算时更是这样。

在改变频率时也必须考虑PLL的建立时间,此时间延迟会导致经过系统的等待时间。例如,改变频率的时间必须包括PLL的建立时间、AGC响应时间、信号从天线到ADC的传播时间,ADC转换时间和DSP中信号处理时间。

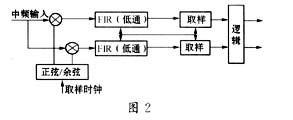

DSP中相关的解调是最复杂的结构,最好的结构形式示于图2。

匹配滤波器通常对于二进制相移键控(BPSK)和正交相移键控(QPSK)分别是最大似然检测器(MLD)或平方/正交检测器。若可以处理MLD的额外处理,则低信号跟踪性能的增益可以是6dB或更高。在很多情况下,由PLL恢复载波和时钟。

输入一般为过取样,并存储在环形缓冲器中。对此缓冲器的读标志是经NCO的时钟环路滤波器的输出。另外,可以用经过ADC的插入器或直接取样。

复合混频器(在基带)区分正和负频率。它们也不需要低通滤波来去除混频分量。混频器的输出馈入匹配滤波器单元,此单元采用一个最大的似然检测器。每个输入波形用每个可能的输入波形校正。选择最大校正做为最类似被接收的波形。

对于包含在存储器中的波形,如最小键移(MSK)、匹配滤波器单元应该用格子结构方法来达到最好误码率(BEK)性能。而选择最大相关,可用每个相关做为Viterbi算法的分支量度。

在选择逆行程长度时,为了不导致过量延迟进入恢复环路应该小心从事。对于调制需要较长逆行程来讲,恢复环路可以用比数据判定更短的逆行程。

载波相位检测器单元用最类似的基准波形计算关于输入波形相关相位的微商。这种相位检测器比传统的相移键控平方环路检测器好3dB。

环路滤波器单元的阶指示环路可以精确恢复的误差类型。

1阶环路对频率步具有稳态误差响应。2阶环路可以精确地恢复频率步,但对频率斜波具有稳态误差响应。3阶环路也用于需要精确频率斜波恢复的地方,然而,必须小心避免输入增益不稳定度问题。

类型指示环路中精确积分器数。NCO是1种积分器,而环路滤波器将包含其余部分。

根据缺席规则,1阶滤波器是在滤波器中不带积分器的I型。2阶滤波器可以是I型有“漏隙”的积分器或II型“精确”积分器。注意,2阶II型在其精确积分器中具有无限大的存储器,因此,不强迫恢复到零。因此,它必须箱位到最大和最小值。

载波NCO单元产生频率正比于输入值的正弦波,可以用内置 sin() 和cos()的C三角函数,但是耗时。可用查表替代相位数字化噪声耗费的执行速度增加。

时钟相位检测器单元的设计取决于调制类型。因为对于匹配滤波器相关的时间导数没有严格形式解,所以时钟相位检测器是与调制有关的。

BPSK和频移键控(FSK)解调器一般采用early-late gater技术。这可经过±Ts/2符号变化积分实现。

MSK和连续相位调制形式做为时钟相位检测器。这是由于波形是正弦波和时间导数正比于相比导数。

结语

以前,军事通信系统领域的软件无线电正在进入主流应用。软件无线电所带来相互适用性和能力,使得在不同应用中用软件更新可增加新的模式。与这种灵活性相伴而来的是复杂的设计问题。

电子发烧友App

电子发烧友App

评论