设计概述

1.1 设计目的

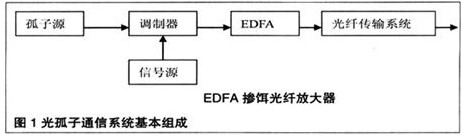

近年来,信息安全应用于生活中的各个领域。在光通信系统中,往往对速率 有着较高的追求。其中对光模块,光纤通信中的传输算法,传输的模式以及光波 段选取有密切关联。随着对带宽,速率等要求日益增加,高速通信已经成为基本 的要求。光纤通信因其具有低损耗,高抗干扰性,从而广泛得到应用。近几年由 于大量用户数据的泄露,造成了极大的损失,使得信息安全成为人们关注的焦点。 目前光纤加密的研究多采用量子加密的方法,本人在中科大量子物理实验室 下属机构问天量子实习发现,目前国内外在实际工程上存在很多漏洞,无法做到 光纤通信中的绝对安全,实现军用和民用任重道远。华为传输加密解决方案,采用 L1 层加密技术,对业务层透明,采用高强度的 AES256 算法,确保各行业的数据安全性。此方案虽然实现简单,但缺点是吞吐量小、端口少、速率低。 对于 ASE 算法的硬件实现,国内外研究学者大部分是基于 FPGA 的硬件实现。通过分析国内外 ASE 在硬件上实现的研究现状,我们想要用 FPGA 硬件实现,达到 5Gbps 的传输速率,这是完全可行的。

1.2 应用领域

本作品应用前景广泛。例如,各级市政机关之间在通信时,有些信息是需要严格加密的(如财务信息,公民户籍隐私)。利用本设计进行加密后,即 便窃密者获取到链路中的数据,也只有穷举才能破译。同时,基于本设计的实时性,可以做到全双工的突发式语音通话,帮助政务人员处理突发事件;或者运用 在军事行动中,指挥中心与前线的通信往往具有简洁,实时,突发的特点。本作品针对上述需求进行设计和验证。改进后的基于混沌序列的 AES 算法具有高复杂度,可防止 SPADPA 攻击。让指挥信息能足够保密,防止被敌人窃取。

1.3 主要技术特点

FPGA 设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低, 可重配,可靠性高以及移植性好等优点。 系统链路部分采用 Aurora 协议,该协议是一款轻量级的光纤链路协议,具有冗余少,可定制度高,链路速率快等特点。

系统组成及功能说明

2.1 系统介绍

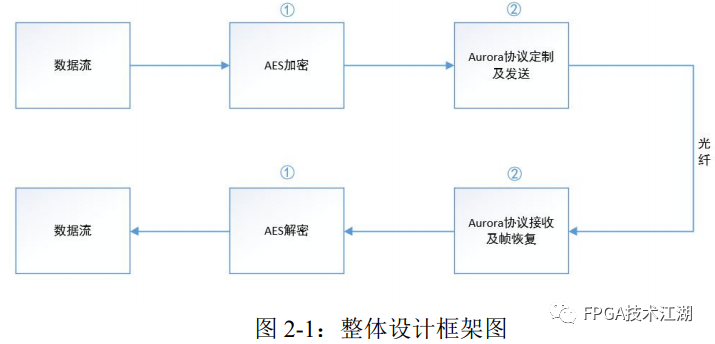

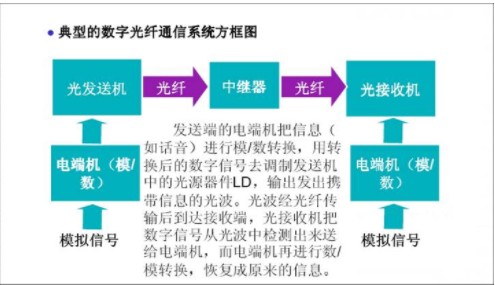

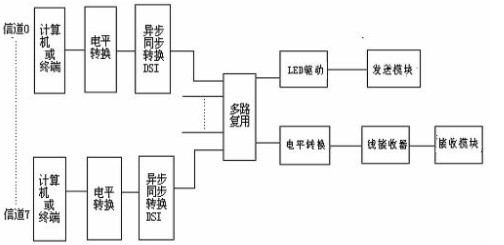

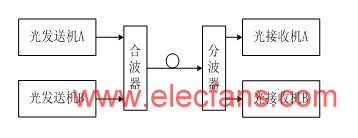

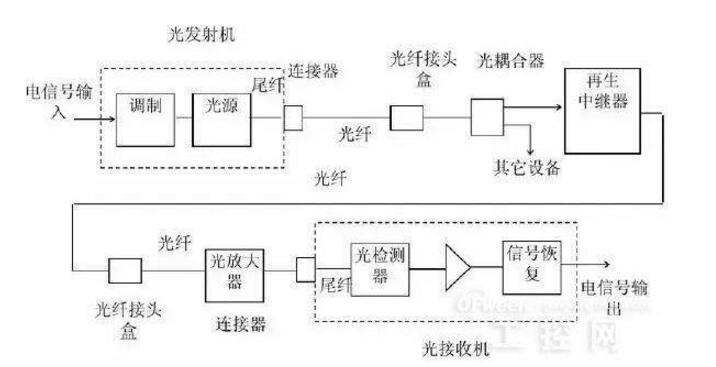

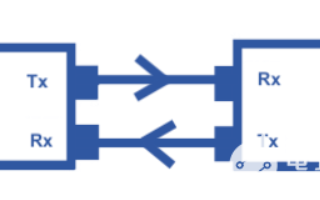

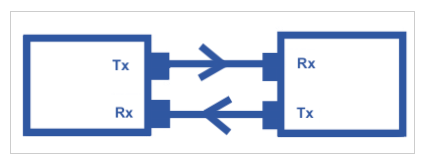

设计了一套完整的光纤通信加密系统(如图 2-1)。系统链路部分采用 Aurora 协议,该协议是一款轻量级的光纤链路协议,具有冗余少,可定制度高,链路速率快等特点。加密协议采用目前 AES256 加密算法,该算法为目前国际最标准化加密算法之一,可抵抗所有已知的攻击,并可在多个平台上拥有速度快,编码紧凑等特点。

2.2 各模块介绍

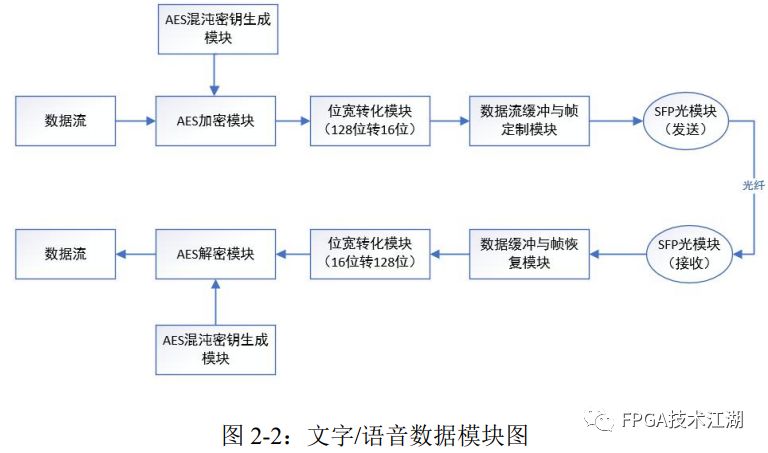

针对以上的框架,我们进行了模块化设计,我们针对视频流数据及语音/文字 数据设计了两套不同的方案。 视频流数据由于其需要高实时性,故我们摒弃了具有较高冗余度的帧结构传 输方式,并对其采用外流水线设计进行传输(如图 2-2);而语音/文字数据由于其数据流较少,往往对其安全性及正确性有更高的要求,故我们采用特定的帧结构, 针对该 AES 算法定制了其链路结构(如图 2-3)。 每一个模块都对其进行了 modelsim 仿真及论证。FPGA 与光模块通信的速率与数据校验,我们通过 vivado 的 IBERT ip 核进行验证;对光纤通信中的信号完整 性,我们通过眼图进行观察。

2.3 硬件电路设计

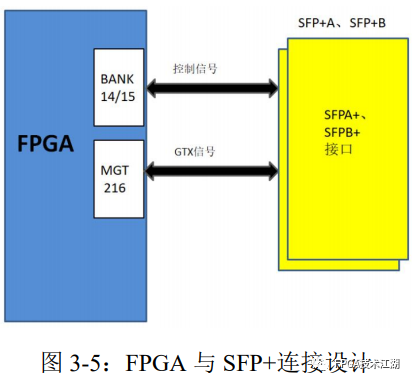

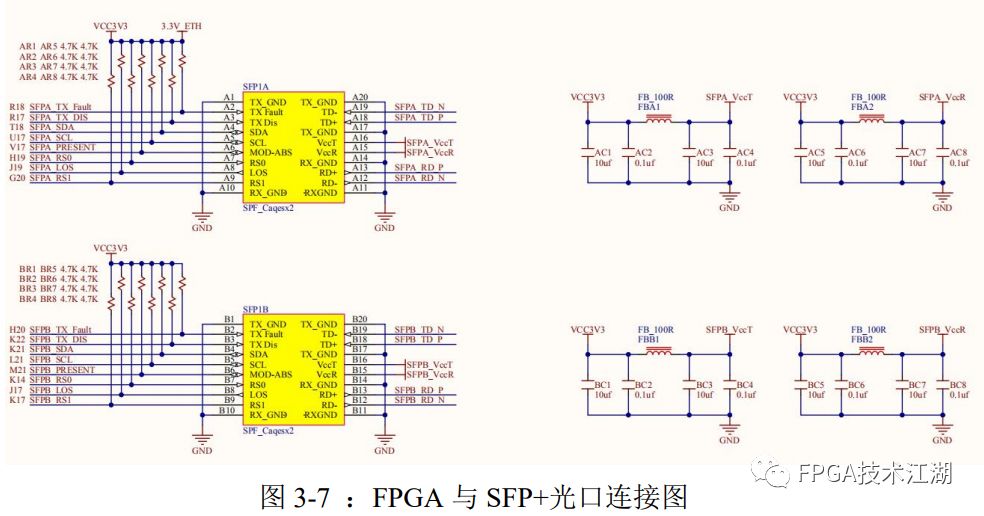

我们硬件电路设计主要体现在 SFP+光口与 FPGA 板卡之间的设计。如图 3-5 所示。

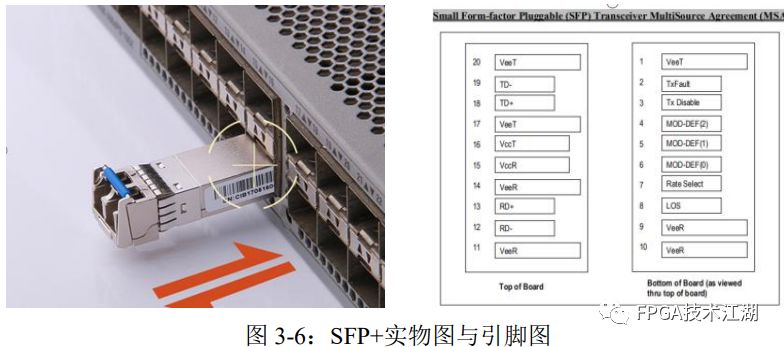

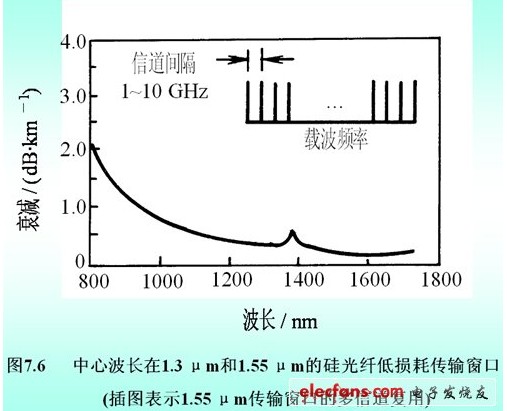

首先我们介绍所使用的光模块。图 3-6 所示为我们使用的 SFP 光口实物图与引脚图。使用的 SFP+的光模块支持 8B/10B,也可支持 64B/66B 的长波(1310nm) 的单模光纤(SMF),有效传输距离为 2m 到 10km,事实上最高可达到 25km。光 口支持 SFP-MSA 协议,选用的光模块支持 10GBase-LR/LW。

FPGA 与 SFP+光口的电路的原理图设计如图 3-7 所示。

作品难点与创新

3.1 AES 加密算法在 FPGA 上的实现

最常用的数据加密方式是软件加密,即在通用微处理器上编程实现,但其加 密速度普遍不高,算法实现的效率较低,安全性和可靠性有限,很多时候不能满足用户的需求。因此,需要更加快速,更加安全可靠的加密实现方式来满足人们 在一些场合下的数据保密要求。 由于我们传输的速率达到 5Gbps,这种 GTP 高速接口下若使用 FPGA+ARM 架构(如 ZYNQ),通过 ARM 完成加密算法将会使得我们效率大大降低,因此串 行通信实现 AES 加密算法已经不能满足我们的需求,故我们采用纯 PL 端 FPGA 设计来实现加密算法。FPGA 设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低,可重配,可靠性高以及移植性好等优点。 3.2 混沌序列密钥设计 混沌序列的产生主要有两类:一类是利用微分方程表示的混沌系统,产生时 间连续的混沌信号,系统由模拟电路来实现,它对电路固有参数及信号再生的误差很敏感,实际实现较困难。另一类是利用迭代方程(映射)或非线性数字滤波器结构表示的混沌系统,产生时间离散的混沌序列,系统由数字电路实现,更适合在通信中应用。本设计需要在 FPGA平台上实现,鉴于 FPGA 无法处理连续时 间系统,所以基于迭代方程来产生混沌序列,之后使用定点小数的方式对方程中的实数进行了处理,使其能在 FPGA 中进行运算。为了使该输出混沌密钥与发送 的明文产生时序相匹配,在输出之前还做了部分拼接操作,使整体序列保密性更高。

3.3 AES 算法在光纤链路上的算法移植

算法移植通常是通过成熟的库函数进行调用,该串行方式下一个时钟周期只 能完成一条指令的实现,算法移植相对简单,不会出现异步跨时钟域处理高速数 据等问题。我们选择纯 PL 端完成算法移植,在一个时钟周期下,既要完成算法的 数据输出,也要考虑到此刻光纤链路中传输状态。因此我们的效率虽然大大提升, 但对我们的设计是一个巨大的挑战。 针对速率匹配,数据对接,缓冲设计等问题,我们分别进行了模块化设计, 分别对其进行仿真和上板测试。在软件调试部分有详细的分析和设计介绍。证明 我们的算法移植是成功的。

3.4 针对语音/文字等加密数据进行特定帧结构定制

在算法移植过程中,我们针对 AES 算法对光纤协议进行了帧定制。传统的帧 传输是对数据流进行传输,对固定长度的数据流加上帧头帧尾进行判断。一旦丢包,整个帧全部丢弃,造成了极大的浪费。 我们对原始的这种光纤帧协议进行了定制,在原来每一帧的基础上,内部对 其封装了四个子帧,每一个子帧由 128 位组成(原因是我们每次加密的数据是 128 位)。对于每一个子帧,帧头为起始的 16 位数据,具有和其他 112 位数据不一样 的脉宽长度,便于后续的帧解析。 通过我们的设计,即使传输过程中丢包,只会影响该当次的 128 位数据,且 该设计给我们帧解析,加密算法的解码提供了便利的平台。

3.5 针对视频流数据进行外流水线设计

外部循环流水线结构由循环展开结构发展而来。具体方法是在组合电路与每 一轮 加密运算对应的部件之间都插入额外的寄存器。该方法可以在同一时刻处理 多个数据分组,提高系统在单位时间内处理数据的速度。 针对视频流,采用 AES 内外流水线设计,通过外流水线设计牺牲逻辑资源使 得加密传输速率提高 15 倍,传输速率可达 2.85Gbps。

3.6 接收端对帧数据恢复

光纤接收端设计部分除了会面临数据流缓冲,高速率通信中异步跨时钟域处 理等问题,还要剥离原始子帧结构,并且去除光纤本身的帧头帧尾。除了我们的加密数据,Aurora 协议本身还会不定期发送一些无效数据,我们要对其进行数据 恢复,并且拼接光纤链路中的 16 位数据,封装成一个个的 128 位加密数据。这也是我们设计的一大难点。

3.7 高速通信中时序约束和信号完整性分析

对于 GTP 高速接口,我们对其做时序约束是非常有必要的。除此之外,还要 要用专业的软件对光口进行测速,并对其信号质量进行分析和评估。 我们使用 Seiral I/O Analyzer 连接到 IBERT 核,验证高速串行通道的状态。从 眼图上可以观察出码间串扰和噪声的影响较小,数字信号整体的特征良好,从而 判断出系统具有非常良好的性能。 作品的难点与创新点部分设计,将会在第四部分(软件设计与流程)中详细 的阐述。

完成情况及软件设计流程

4.1 AES 算法 IP 核设计

该部分我们分加密和解密两块来详细说明。 加密: 为了验证优化后 AES 算法功能的正确性,需要选取测试向量进行验证。我们 从官方的文档中获得参考基本功能测试向量。

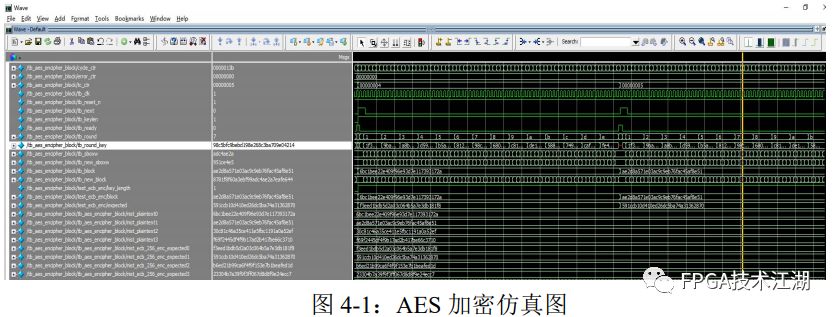

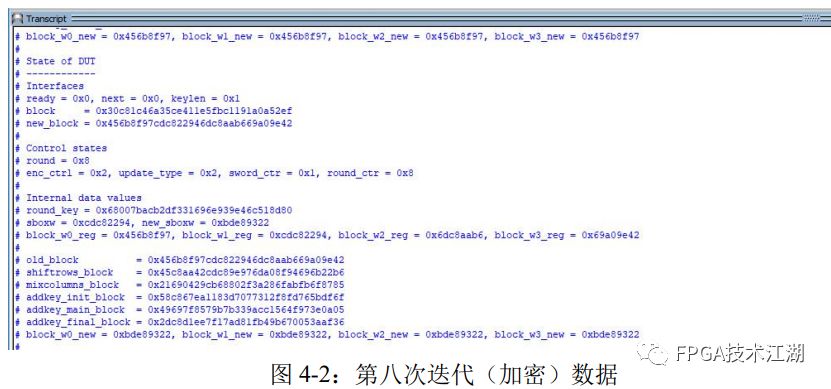

加密过程的 modelsim 仿真图 4-1 所示:该部分画面放大后可观察到有以下重 要数据: round(当前内部循环的次数), tb_round_key (测试向量特工的循环密钥值) tb_block (送入加密模块的数据) tb_new_block (加密后输出的数据) Sbox (加密所需的 s 盒数据) 由于数据比较庞大,我们将重要数据打印在了 modelsim 仿真的窗口,如图 4-2 所示为第八次迭代循环加密过程的部分信息。

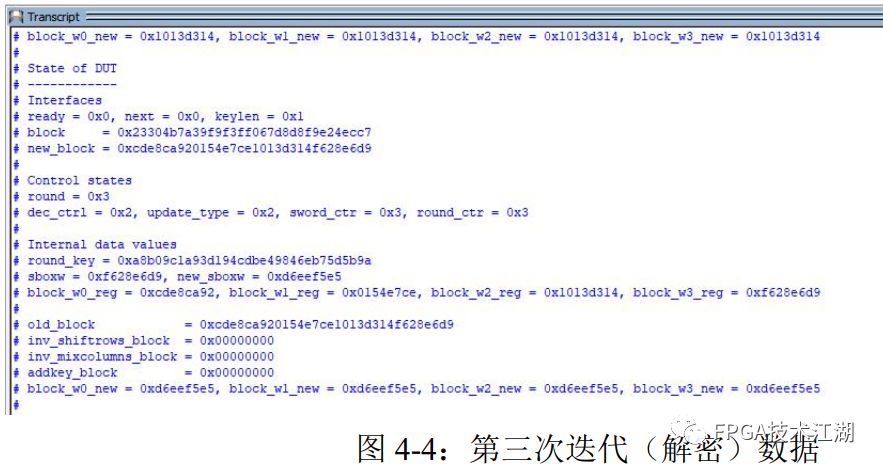

解密过程的 modelsim 仿真图(如图 4-3),该部分画面放大后可观察到有以下重要数据:round(当前内部循环的次数),tb_round_key (测试向量特工的循环密钥值),tb_block (送入解密模块的数据),tb_new_block (解密后输出的数据)。 由于数据比较庞大,我们将重要数据打印在了 modelsim 仿真的窗口,如图 4-4 所示为第三次迭代循环解密过程的部分信息。

4.2 AES 算法在光纤链路上的算法移植

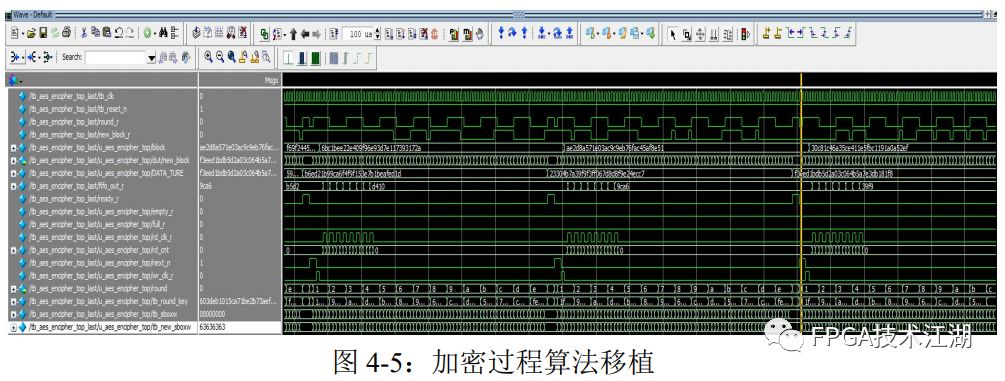

首先我们将 AES 算法分别封装成加密、解密两个 IP 核,内部产生上述测试向 量、密钥等数据。 加密后数据为 128 位位宽,由于光纤中传输的数据为 16 位位宽,故需要设计 一个位宽转换模块。 AES 加密后输出速率与光纤传输速率不一致,为异步信号。我们设计了一个 FIFO 控制模块,并调用了 IP 核进行设计。 我们在 vivado 中编译 IP 核数据,并调用 modelsim 观察我们测试数据,放大 图 4-5 后可观察以下重要数据: block:送入的带加密数据 new_block :加密以后输出的 128 位数据(每次加密迭代循环都有输出) DATA_TURE:当加密完成后,根据 ready 信号使能取出当前 128 位加密完成的数据 fifo_out_r:将 128 位数据转化成 16 位数据,并从 FIFO 端输出 next:使能拉高时,表示当前加密完成,可送入新的待加密数据 ready :当前数据加密完成,可以读取该数据

4.3 混沌序列密钥设计

通过前文的分析,我们选择了 logistic 模型。在 jupyter notebook IDE 上用 python 调用 matlab 库设计了 logistic 模型,迭代 200 次生成的序列如图 4-6。

改变不同的 u 值产生的模型仿真图 4-7 如下(初值 X0=0.5):

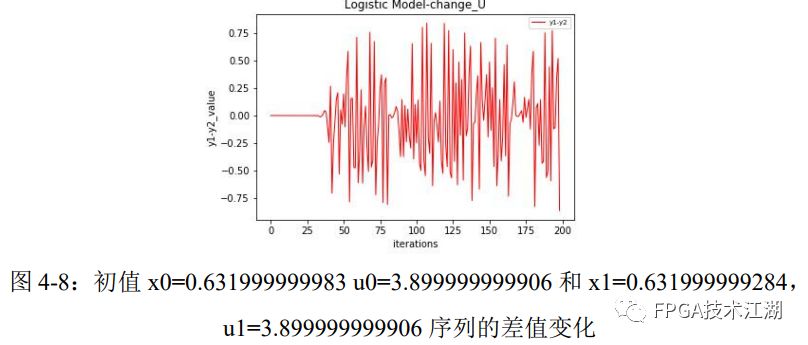

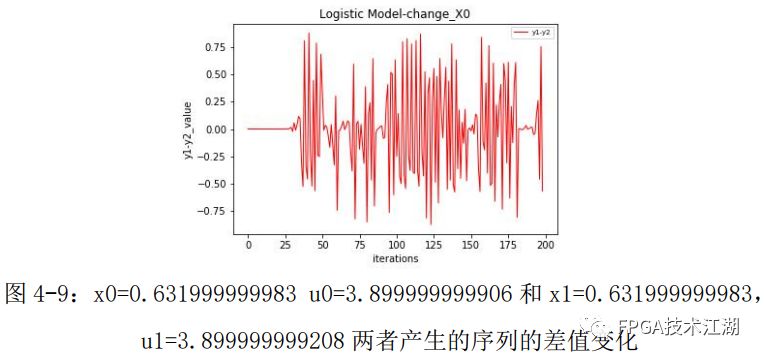

通过观察当 u 的取值在 3.8~4.0 左右时模型进入混沌现象。 接着测试模型对初值的敏感程度,设置初值 x0=0.631999999983 u0=3.899999999906 和 x1=0.631999999284,u1=3.899999999906 两者产生的序列的 差值变化如图 4-8,设置初值 x0=0.631999999983 u0=3.899999999906 和 x1=0.631999999983,u1=3.899999999208 两者产生的序列的差值变化如图 4-9。

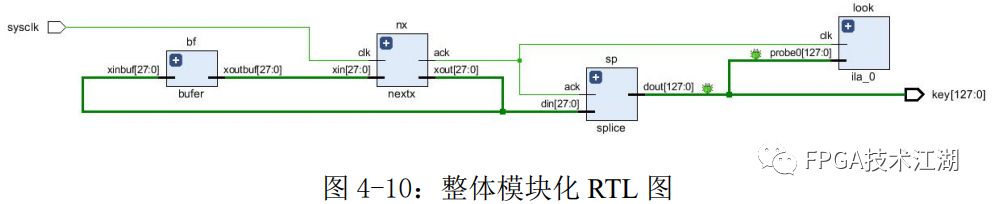

可以看出设置的初值仅仅只是相差 E-10,最后产生的序列相差很大。 将算法移植到 FPGA 平台,包括每次迭代循环的计算模块。为了避免模块的 输出直接又作为输入引起实现违规,将每次的输出信号引出,在另一个模块里缓 存。等待计算模块计算完成时,将上一次的计算结果作为新的数据作为计算模块 的输入。另外为了灵活与加密解密模块的数据位宽对接,设计了拼接模块,可以 灵活定制输出数据位宽与时序。整体模块化 RTL 图如图 4-10。

对系统进行仿真结果如图 4-11,时序和位宽都满足要求:

设计完成后分析系统模型输出数据的 Lyapunov 指数(简称李氏指数),它刻 画非线性系统混沌特性的有效方法之一,只要李氏指数大于零,则系统是混沌的。最终在硬件上生成的数据,通过软件分析其李氏指数为 0.4953767618,验证了该 模型为混沌系统。

4.4 针对语音/文字加密数据进行特定的帧定制

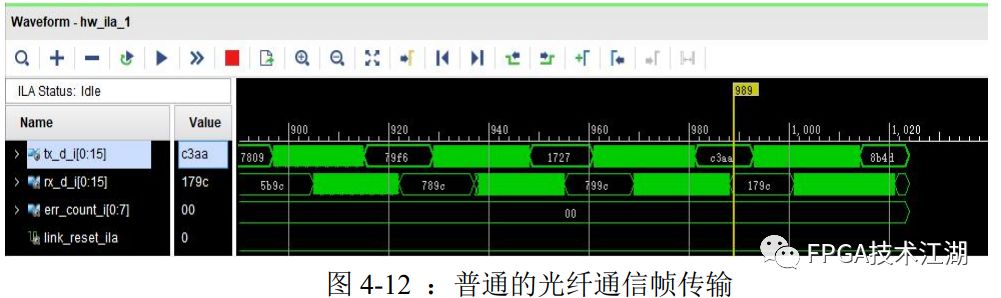

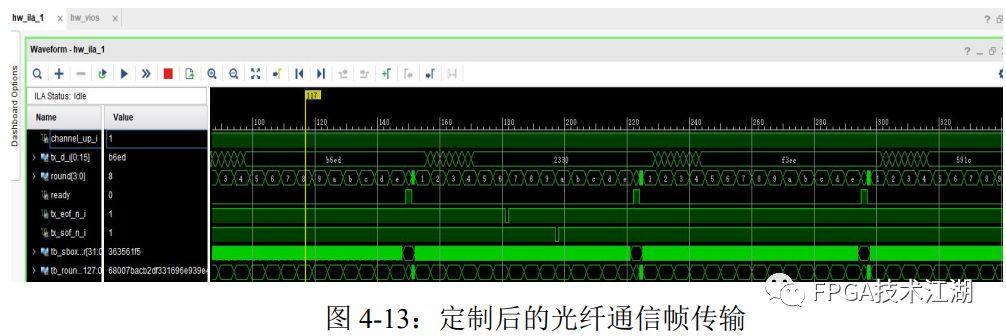

普通光纤传输的传输方式分为流传输和帧传输,而流传输由于其不可靠性, 以及不适合控制和定制的特点,我们选择了帧传输,如图 4-12 为普通的光纤通信 帧传输。 由于加密数据为 128 位位宽数据,而光纤中每次传输 16 位位宽数据,故八次 传输周期传输一个 128 位的加密数据。如果采用普通的数据流传输的话,一旦中 间有丢包,后续所有的数据将会错误,这在我们加密通信中是绝不允许的。 为了解决该问题,我们针对 AES 算法定制了一种帧结构(如图 4-13)。我们 将每一个 128 位加密数据作为一次传输的帧结构,而每次的前 16 位作为该帧结构 的帧头,这样做的好处就是:1.帧结构传输不容易产生误码和丢包 2.即使丢包 我们也不会影响下一个数据的传输。 我们在该项目的测试中,测试向量为上述四个 128 位数据循环发送。我们在 原来的帧结构的基础上,又封装了一层光纤链路自带的帧结构,以四个 128 位数 据为光纤传输的一个大帧结构。保证了链路传输的可靠性。

图 4-13 中的 tx_d_i 信号为我们发送到链路中的数据信号,以 b6ed 为例,该 16 位数据为加密后的 3 号测试向量起始 16 位数据,后面紧跟 7 个剩余的 16 位数 据,组成一个完整的 128 位加密数据。通过我们的帧定制操作,极大的提高了我 们加密传输的可靠性。

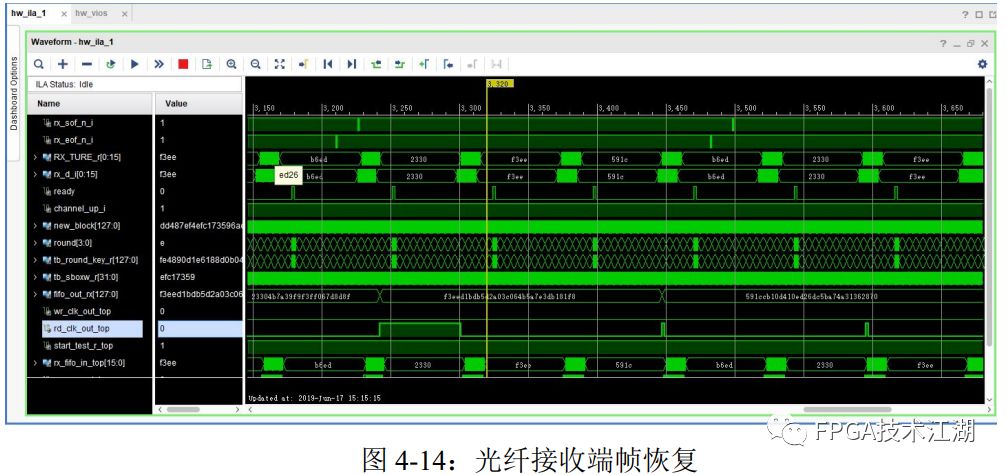

4.5 接收端对语音/文字加密数据帧数据恢复

接收端对帧数据进行恢复,去除定制的帧头帧尾,并消除原有 Aurora 协议不 定时发送的无效数据带来的误码。 如图 4-14 所示,我们将光纤接收端接收到的数据(rx_d_i)接收下来,并将 其进行 16 位转 128 位操作,输出数据为 fifo_out_rx,我们对比测试向量的数据发 现,我们的数据是正确无误的。

4.6 发送端对视频流数据进行外流水线设计

针对视频流数据,我们同时使用 15 个加密模块,分别错开一个周期进行同时 加密。如图 4-15 蓝色箭头所指:每个加密模块完成加密后,将加密数据送至寄存 器缓存,使得我们的加密效率提高了 15 倍。

系统综合测试分析

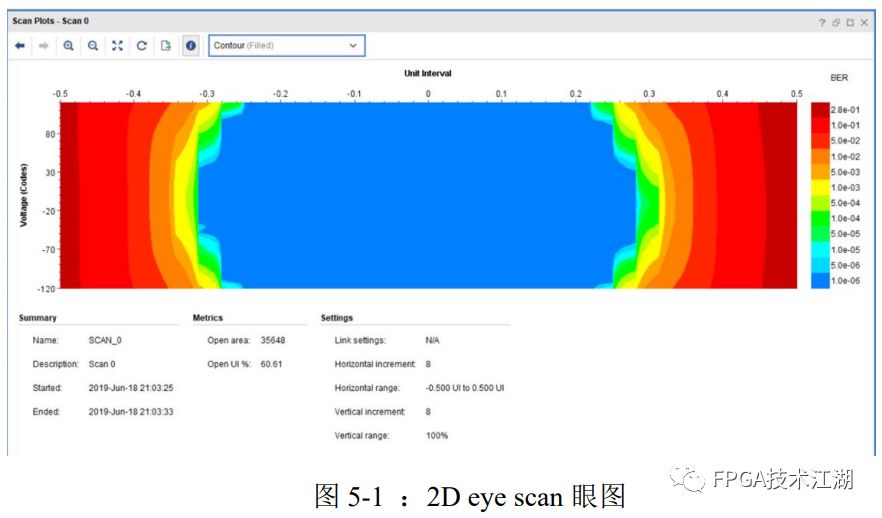

IBERT(Integrated Bit Error Ratio Tester)是 Xilinx 提供的用于调试 FPGA 芯片 内高速串行接口的工具。它通过 JTAG 总线提供了 FPGA 到 Vivado Serial I/O Analyzer 的通道。通过 IBERT 用户可以定制线速率、参考时钟速率、参考时钟来 源,总线宽度。它同时还额外需要一个系统时钟,这个时钟可以来自 GTX 收发器 或者其它 FPGA 管脚。 使用 IBERT 进行 GTP 通道的验证有以下三个步骤: 1.生成 ibert 核:根据硬件高速串行总线的需求来定制和生成 iber 核。 2.使用上一步的 ibert 核自动生成 ibert 参考设计并生成 Bit 文件。 3.使用 Seiral I/O Analyzer 连接到 IBERT 核,并验证高速串行通道的状态 我们在 vivado 中生成该测试工具,对 SFP+光口实际发出的数据进行测速和信 号完整性分析。如图 5-1 所示。我们可以在图的正下方观察到该链路的实际速率为 5Gbps,速率完全满足我们的设计需求;误码率越低,颜色越偏向蓝色(深蓝色);当误码率越高,颜色越偏向红色,眼图张开的大小就代表信号质量的好坏。我们 通过观察眼图可以发现,蓝色区域很大,且角度张开合理。结合图 5-2,通过 5Gbps 速率的光纤传输 4.557E10 Bit 数据后,误码率仅为 2.195E-11,远低于官方规定的 误码率 1.E-10 标准,可以得出结论:信号完整性分析良好,信号质量传输可靠。

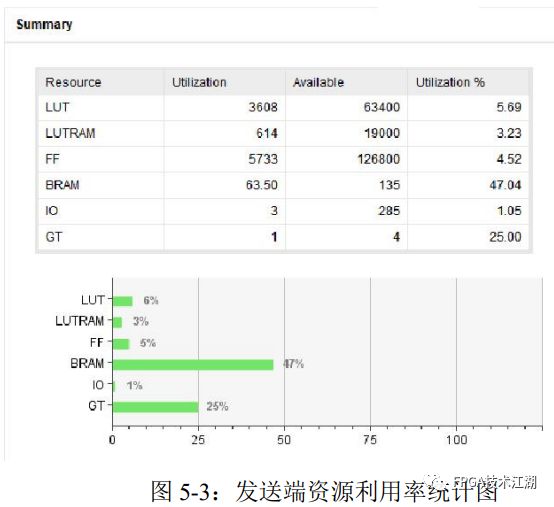

同时我们通过算法在硬件上的优化,可以占用很少的资源到达所需要求,如 图 5-3 和图 5-4 所示,可以看出很低的资源利用率。

总结

本设计具有很高的实用价值,在保密通信领域,视频安防监控领域,军用或 民用视频/音频传输领域,都有极强的应用场景。本次作品的难点和创新点在于: 1. AES 加密算法在 FPGA 上的实现; 2. AES 算法在光纤链路上的算法移植; 3.针对 AES 算法在光纤发送端进行特定的帧定制; 4.针对视频流做了外流水线设计,保证视频数据低延迟传输; 5.混沌序列的设计; 6.高速通信中时序约束和信号完整性分析。 参考文献 [1] 7 Series FPGAs GTX/GTH Transceivers User Guide [2] Vivado Design Suite User Guide [3] Aurora 8B/10B v11.0 LogiCORE IP Product Guide [4] Small Form-factor Pluggable (SFP) Transceiver MultiSource Agreement (MSA) [5] Xilinx.Aurora 8B/10B Protocol Specification.Revision 2.2[M].Xilinx, 2010,10:16-90 [6] L.Henzen and W.Fichtner,"FPGA parallel-pipelined AES-GCM core for 100G Ethernet applications[C]", 2010 Proceedings of ESSCIRC, Seville, 2010, pp. 202-205. [7]赵文虎,王志功,费瑞霞,朱恩,吴微.基于逻辑设计的光纤通信 8B/10B 编解码方法 研究[J].电路与系统学报,2003(02):48-53. [8]王志功.光纤通信系统超高速集成电路设计[J].中国科学,2000(03):35-40. [9]谢郁洁.基于 FPGA 的核间高速接口的设计与验证[D].电子科技大学,2014. [10]何少恒.基于 SFP光纤通信接口的高速IQ数据传输系统设计与实现[D].中北大 学,2016. [11]王小伟.AES 加密算法的研究与 IP 核设计实现[D].哈尔滨工业大学,2013. [12]Yufeng Liu,Xiangyang Xu,Hao Su.AES Algorithm Optimization and FPGA Implementation[J].IOP Conference Series: Earth and Environmental Science,2019,267(4). [13]杨静.一种 AES 算法加密传输系统的设计与实现[J].电子设计工 程,2019,27(03):123-126+131. [14]何德彪,胡进,陈建华.基 FPG 的高 AE 实现[J].华中科技大学学报(自然科学 版),2010,02:101-104.

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论