void SPI_Init(){M_CS_out;M_SCK_out;M_SDO_out;M_SDI_in;}//向从机写一个8位的数据,同时读出30个bit位,前两个bit位不读。long

2019-04-19 01:27:13

8位/16位/32-BIT系列单片机的区别是什么?有什么特点?

2021-09-24 07:15:36

有谁知道扰码器和解扰码器的VHDL编程,各位大哥们教教小弟,小弟菜鸟一个,老师布置的课程设计,后天就要教了!!!{:soso_e109:}{:soso_e109:}

2012-11-24 19:23:33

如果一个扰码器现在做并行化,例如要求输入位宽为32位,那么本原多项式如何确定?在实现的过程中,如果想使用并行,是不是需要将同移位寄存器长一致的周期后状态机算出来呢?不很明白为什么可以实现并行化,输出不是还是一位一位的数据的吗?是不是将对应的周期数计算出结果吗?

2019-05-07 16:53:54

AD5544的18位数据由2bit地址位和16位数据位组成,采用标准SPI的时候一次传输8位数据该如何传输呢?是从17-0位放置数据还是23-6位放置数据呢。datasheet上说最后18位被保留不知道什么意思

2023-12-19 08:08:15

AD9826串行接口的通过SDATA、SCLK和SLOAD实现写入四个寄存器

但是在进行读操作的时候,我不知道在什么bit位实现SDATA的输入输出方向切换?

每次读写都是16个bit,请问是在写完高4位地址后进行读操作呢?还是在写完高8位后进行读数据操作

2023-12-04 06:06:26

是ADI的SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。

调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号

2023-12-18 08:27:39

是ADI的SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。 调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号上

2018-09-06 14:32:00

BCD码的硬件实现,采用左移加3的算法,具体描述如下:(此处以8-bit 二进制码为例) 1、左移要转换的二进制码1位2、左移之后,BCD码分别置于百位、十位、个位3、如果移位后所在的BCD码列大于或

2017-05-11 16:21:02

我想问一下CYUSB3014位宽为8bit、16bit和32bit时,最大传输速率是不是一样的?

2024-02-28 07:08:20

DVB通用加扰算法代理协议蓝皮书

2009-05-08 09:02:30

串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达。两根线(也包括PCB的薄膜布线)独立的情况下,相互间应该不会有电气信号

2019-08-08 06:21:47

各位大神:根据FPGA bit位流文件,对其配置内容进行解析,以及反解,有高手请指教!感谢!

2019-05-23 15:48:48

楼主理解串口的不是很透彻,串口程序是用 小墨哥 的 串口程序修改的,现在要做的是把 16位的bit 用串口发送到上位机,可是,我也试图去分立 高8位,低8位,试验还是不通过,总是发送的不对有没有那个

2015-09-04 21:03:03

作者:一博科技SI工程师陈德恒摘要:随着电子设计领域的高速发展,产品越来越小,速率越来越高,信号完整性越来越成为一个硬件工程师需要考虑的问题。串扰,阻抗匹配等词汇也成为了硬件工程师的口头禅。电路板

2014-10-21 09:53:31

作者:一博科技SI工程师陈德恒3. 仿真实例在ADS软件中构建如下电路: 图2图2为微带线的近端串扰仿真图,经过Allegro中的Transmission line Calculators软件对其叠

2014-10-21 09:52:58

PCB设计中如何处理串扰问题 变化的信号(例如阶跃信号)沿

2009-03-20 14:04:47

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且

2018-08-29 10:28:17

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号

2020-06-13 11:59:57

[table][tr][td] 一、 什么是位段和别名区是这样的,记得MCS51吗? MCS51就是有位操作,以一位(BIT)为数据对象的操作,MCS51可以简单的将P1口的第2位独立操作:P1.2

2018-07-09 00:22:05

[table][tr][td] 一、 什么是位段和别名区是这样的,记得MCS51吗? MCS51就是有位操作,以一位(BIT)为数据对象的操作,MCS51可以简单的将P1口的第2位独立操作:P1.2

2018-07-04 09:34:17

USB Audio方案(192KHZ采样,24bit位宽)Mike Meng 孟凡忠 email:mike@rti.com.hkmsn:mfz118@hotmail.com; Skype:mfz118; QQ:15958574

2011-05-08 18:12:20

”与“1”的出现概率都接近50%。扰乱虽然改变了原始传送码流,但这种扰乱是有规律的,可以在接收端解除。将待发送的信息序列与发端产生的m序列进行模二加(扰码),扰码序列通过传输信道传送到接收端,接收端接

2019-12-18 09:37:35

块中, SRC_CRC_EN=3 时,可以在 WiMAX 标准下为编码进行加扰,对应的,在上行就需要对加扰的信号进行解扰,利用 TCP3D 可进行解扰操作,但是,现在不知道 BCP 的加扰是以何种算法实施的,在 TCP3D 中该怎样布置解扰算法呢?

希望各位老师给予帮助,十分感谢!

2018-06-21 12:21:49

串扰串扰的途径:容性耦合和感性耦合。串扰发生在两种不同情况:互连性为均匀传输线(电路板上大多数线)非均匀线(接插件和封装)近端远端串扰各不同。返回路径是均匀平面时是实现最低串扰的结构。通常发生这种

2017-11-27 09:02:56

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变

2019-05-31 06:03:14

继上一篇“差模(常模)噪声与共模噪声”之后,本文将对“串扰”进行介绍。串扰串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达

2018-11-29 14:29:12

串扰的基本原理

2021-03-18 06:26:37

所谓串扰,是指有害信号从一个传输线耦合到毗邻传输线的现象,噪声源(攻击信号)所在的信号网络称为动态线,***扰的信号网络称为静态线。串扰产生的过程,从电路的角度分析,是由相邻传输线之间的电场(容性)耦合和磁场(感性)耦合引起,需要注意的是串扰不仅仅存在于信号路径,还与返回路径密切相关。

2019-08-02 08:28:35

在选择模数转换器时,是否应该考虑串扰问题?ADI高级系统应用工程师Rob Reeder:“当然,这是必须考虑的”。串扰可能来自几种途径从印刷电路板(PCB)的一条信号链到另一条信号链,从IC中的一个

2019-02-28 13:32:18

怎么发送16位bit到 串口,串口只能发8位? 或者谁有编好的模块,借来看看啊。。。。脑袋已经大啦!!!

2016-07-28 10:10:21

为什么CC1101信道出现串扰现象?各位大神,我在使用CC1101的时候,遇到如下问题,我购买的是模块,并非自己设计,所有参数,使用smart rf生成,参数如下:base frequency

2016-03-11 10:01:10

多了,这样我想有个问题就是,在正常采集时,这几个通道间会不会有互相串扰的问题。谢谢。

另外我想知道互相串扰产生原因,如果能成放大器内部解释更好

2023-11-21 08:15:40

继上一篇“差模(常模)噪声与共模噪声”之后,本文将对“串扰”进行介绍。串扰串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达

2019-03-21 06:20:15

串扰的概念是什么?到底什么是串扰?

2021-03-05 07:54:17

什么是串扰?互感和互容电感和电容矩阵串扰引起的噪声

2021-02-05 07:18:27

航空通信系统变得日益复杂,我们通常需要在同一架飞机上安装多条天线,这样可能会在天线间造成串扰,或称同址干扰,影响飞机运行。在本教程模型中,我们利用COMSOL Multiphysics 5.1 版本模拟了飞机机身上两个完全相同的天线之间的干扰,其中一个负责发射,另一个负责接收,以此来分析串扰的影响。

2019-08-26 06:36:54

什么是有扰射频?怎么消除有扰射频?

2021-05-25 06:51:47

串扰信号产生的机理是什么串扰的几个重要特性分析线间距P与两线平行长度L对串扰大小的影响如何将串扰控制在可以容忍的范围

2021-04-27 06:07:54

看了郭天祥的51单片机24c02的程序,其中BIT write=0;这句话是什么意思?上边说是标志位,但我不明白标志位在这里是什么意思?标志位怎么使用的?什么时候用到。

2013-02-25 10:36:18

面对串扰,包地是万能的吗?请看不一样的解答

2016-12-30 16:29:07

原创|高速SI培训1.信号串扰的成因串扰(Crosstalk),顾名思义、是指不同信号互连链路之间的相互干扰。对于传输线而言,即能量从一条传输线耦合到另一条传输线上,当不同传输线产生的电磁场发生

2016-10-10 18:00:41

如果您给某个传输线的一端输入信号,该信号的一部分会出现在相邻传输线上,即使它们之间没有任何连接。信号通过周边电磁场相互耦合会产生噪声,这就是串扰的来源,它将引起数字系统的误码。一旦这种噪声在相邻

2019-07-08 08:19:27

为16位还是8位?请举例说明如何使用Pix1Exchange 8BIT传输数据。在上面的场景中,我可以这样配置用于将16位数据写入8位寄存器:SPI1_Exchange8bit

2019-07-08 08:33:53

静态存储器SRAM是一款不需要刷新电路即能保存它内部存储数据的存储器。在SRAM 存储阵列的设计中,经常会出现串扰问题发生。那么要如何减小如何减小SRAM读写操作时的串扰,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

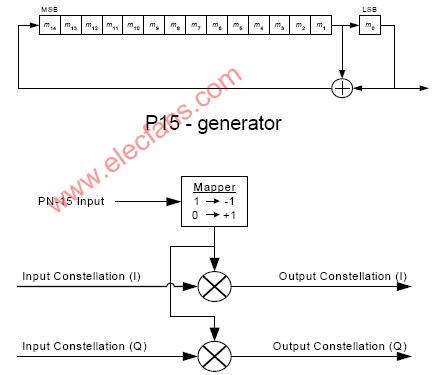

下行扰码的生成过程是怎样的?如何用FPGA去实现下行扰码?

2021-04-30 07:24:05

在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字电路中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

2019-11-05 08:07:57

是有规律的,可以在接收端解除。将待发送的信息序列与发端产生的m序列进行模二加(扰码),扰码序列通过传输信道传送到接收端,接收端接收到扰码序列,使用同样的m序列进行模二加,即可恢复原来的信息。

三

2023-09-21 10:42:02

求一位大神做老师,加QQ3279828860其他的详谈

2018-05-20 02:07:42

示波器通道间串扰的影响 目前几乎所有通用品牌的主流示波器通道都不是隔离的,那么在进行多通道测试的时候,通道与通道之间会一定程度互相干扰,因此通道隔离度指标非常重要,隔离度越高的示波器测量就越精确

2020-03-23 18:53:35

双绞线的性能在一直不断的提高,但有一个参数一直伴随着双绞线,并且伴随着双绞线的发展,这个参数也越来越重要,它就是串扰 (Crosstalk)。串扰是影响数据传输最严重的因素之一。它是一个信号对另外一个

2018-01-19 11:15:04

有没有人在学习自抗扰技术的,能请教一下吗,刚开始学有很多不会的地!

2015-11-16 11:31:08

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

的bit位宽都定义为8疑问:这是为什么呢?Int ColorSpace_getBpp(ColorSpace_Type colorSpace)[ Int bpp;switch (colorSpace

2018-07-27 08:15:46

请教AD9945 寄存器配置关于9945寄存器的配置和版本:查看相关资料说四个寄存器需要一起配置,即每次需要发送4bit(3bit地址+1bit测试位)+48bit数据(12bit*4),查看手上

2018-08-15 08:04:07

是SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。 调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号上就会出现噪声。将采样的时间延长也无法消除串扰。想请教一下各路专家,造成串扰的原因和如何消除串扰,谢谢。

2019-05-14 14:17:00

[size=18.6667px]各位大侠:请问ADXL345:16位bit ,13位数据(16g)第一个为符号位 余下的是啥?谁有补码数据处理c语言?

2018-08-20 07:32:25

“28-Bit Shift In”三个功能,我想使用“16-Bit Parallel Capture”功能,因为它能在时钟上升沿时捕捉电平,比较高速,但我只用到其中一位(1个管脚),其他位的管脚作为ARM的其他

2018-06-21 02:27:33

请问一下51单片机bit定义标志位无效原因是什么?

2021-10-15 08:13:41

高频数字信号串扰的产生及变化趋势串扰导致的影响是什么怎么解决高速高密度电路设计中的串扰问题?

2021-04-27 06:13:27

电路上的开关检测电路,外部DI1开路的时候,光耦不发光,DIB1输入mcu高电平;外部DI1合闸接地GND-E的时候,光耦发光,DIB1低电平。在平常应用没问题,但是做抗扰度试验就不行了,DI1和GND-E加差模2.5kV,100KHz的阻尼振荡干扰信号,整个设备就死机了,请问哪里改进,增加抗扰度。

2020-03-25 09:16:20

本帖最后由 逸興遄飛 于 2016-4-15 14:08 编辑

辐射抗扰:10V 有点不明白

2016-04-15 09:24:44

一一阐述了。如果要想做扰码器,首先要知道自己的扰码器最长周期是多少位的。例如在我们的工程中,由于扰码只是其中的一个部分,他需要承接上面发送数据的格式,这样一来,根据相关标准中指定的扰码多项式选择这样的一

2019-07-31 16:30:47

求各位大神做静电抗扰度试验的方法,以及相关的利弊。是不是都是按照国标做的,产品是按照什么标准做的实验?

2016-04-21 13:04:47

系数设置为4.3。图中分别在A0、B1、C1处加上了示波器探头,可利用示波器观看波形,B1的10MW电阻也是为了加探头而设置的。仿真结果如图5所示。

从图5中可以看出串扰的幅度比较

2018-08-28 11:58:32

高速数字设计领域里,信号完整性已经成了一个关键的问题,给设计工程师带来越来越严峻的考验。信号完整性问题主要为反射、串扰、延迟、振铃和同步开关噪声等。本文基于高速电路设计的信号完整性基本理论,通过近端

2010-05-13 09:10:07

在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析

2018-09-04 14:48:28

串扰问题产生的机理是什么高速数字系统的串扰问题怎么解决?

2021-04-25 08:56:13

DVB COMMON SCRAMBLING ALGORITHMINTRODUCTIONThis document contains the forms of the distribution

2009-05-07 21:36:40 35

35 一、简要概述: 在芯片设计过程中,一个系统通常是同步电路和异步电路并存,这里经常会遇到CDC也就是跨时钟域处理的问题,常见的处理方法,可能大家也已经比较熟悉了,主要有单bit跨时钟处理、多bit

2021-03-22 10:28:12 6257

6257 以 32-bit 英飞凌 TC377 为例右下图可见,虽然是32-bit MCU,但是每个地址对应的是一个byte【8-bit】左上图是通过 Trace32 查看单片机memory, 可见

2021-10-25 16:36:01 11

11

电子发烧友App

电子发烧友App

评论