众多的行业标准、规格尺寸、频率和频谱所有权都在推动对商业无线的灵活性要求不断提升。Xilinx®多模无线目标设计平台这是面向了高吞吐量、带 有域优化FPGAs、IP构建块、设计工具、参考设计和开发板的信号处理密集型系统的需求。单芯片数字无线装置可以设计用于支持多种标准,极大的简化了供 货链,并使原始设备制造商(OEM)能够对网络提供商的要求快速做出响应。

通过高传输效率降低资本支出和运营支出

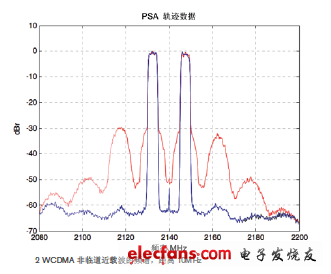

LDMOS1 功率放大器的3G无线接口的典型传输效率在8%到15之间。最新一代的功率放大器和Xilinx峰值因数降低(CFR)和数字预失真 (DFD)LogiCORE™ IP利用先进的数字算法、效率可以把它提高到35%到45%。这表示对于典型的10000个基站的网络来说,每年的运营支出(OpEx2)成本可以节省2 千万美元之多。通过在功率放大器中采用更小的晶体管,还可以降低资本支出(CapEx3),而且能够在天线上使用相同的传输功率额定值。

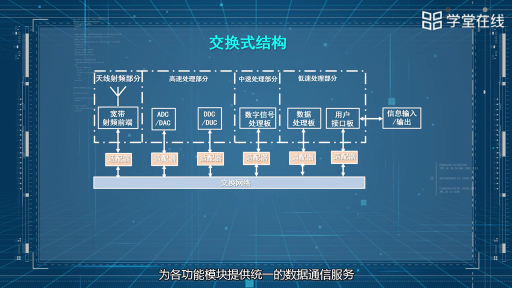

集成是降低功率和成本及提高可靠性的关键

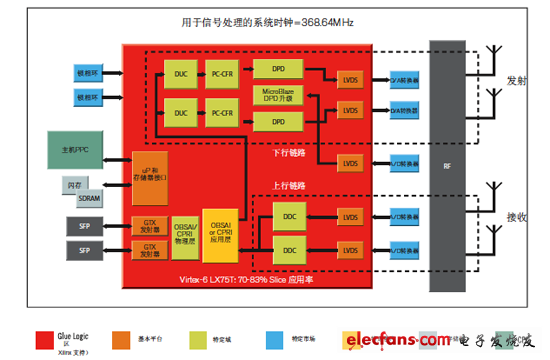

使 用单一的FPGA替换多个ASSP可以实现最小的数字PCB占用面积。Xilinx的FPGA把丰富的DSP与逻辑电路资源结合在了一起,在具有实现 CPRI,OBSAI或JESD204A连接能力的千兆位级发射器(MGT)上高效的实现了数字上变换(DUC)、数字下变换(DDC)、CFR和DPD 算法。Xilinx FPGA的低功率高性能构造可以提供在同级别产品中领先的功耗性能和最低的总体电路板成本。

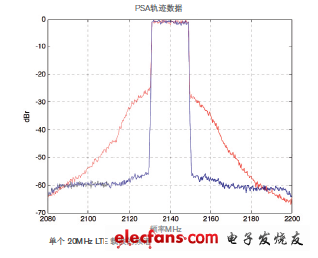

例:使用DPD LogiCORE IP进行2发射、2接收 (2x2) LTE-DFE参考设计

参考设计的特点

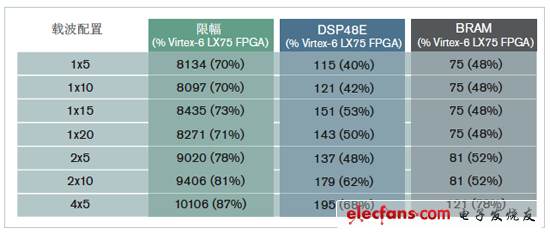

• DUC/DDC,用于每个天线的5、10、15及20MHz单载波和2x5、2x10和4x5MHz多载波选件

• Xilinx CFR,输出峰值与平均功率比(PAPR)-7dB,在误差向量幅度(EVM)《4%,邻道泄漏比(ACLR)》70dB 时

• Xilinx DPD最多支持4个带单MicroBlaze™处理器引擎的发射器,可以提供最高30dB的频谱矫正性能和超过40%的Doherty功率放大器效率

• 全OBSAI主从PHY利用内置的低功率MGT支持最高6.144Gbps的线路速度

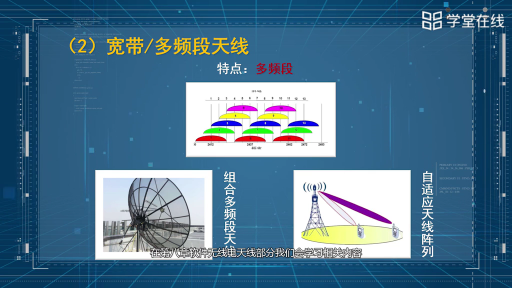

• 可扩展到2x4 (2T4R)和4x4 (4T4R) 天线阵列,与Virtex®-6 FPGA包迁移组合

FPGA资源利用

• 包括了上图中标注的所有资源,包括:

o 微处理器接口

o OBSAI主从

o OBSAI简单应用层

o 2发射、2接收 DUC/DDC/CFR,具有以下使用Xilinx LTE-DFE参考设计实现的载波配置,和Xilinx DPD LogiCORE IP

多模无线演示平台

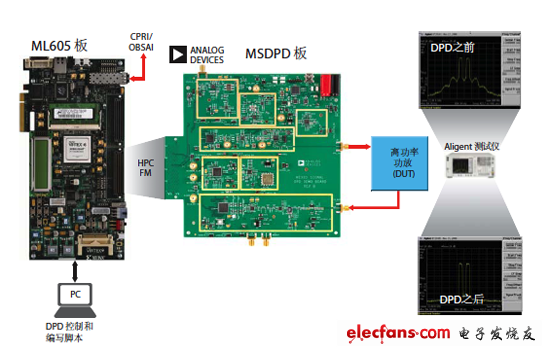

无线射频子系统的设计能与它们所处的应用环境息息相关。这对于复杂的算法如数字预失真尤其明显,在该算法中,很难对诸如热和无功晶体管存储器和模拟信号链路的特性等模拟电路效应进行建模。

Xilinx 已经在与AnalogDevices公司合作制造高性能的多模无线演示平台,它可以演示第三方功率放大器在各种频率和任意无线接口下的DPD解决方案。 XilinxML605电路板和Analog Devices的混合信号数字预失真(MSDPD)电路板通过两块电路板上的 FMC 接头连接起来。XilinxML605上实施了具有DUC、DDC、CFR和DPD功能的高级信号处理应用,充分利用了Analog Devices公司MSDPD板上的高性能数据转换器和 RF 信号链路。

特点

Xilinx ML605板

• Virtex-6 LX240T FPGA 使用户可以为任何波形开发复杂的DUC/DDC、CFR和DPD算法

• 如需完整的规格,请访问: http://www.xilinx.com/products/devkits/EK-V6-ML605-G.htm

Analog Devices的MSDPD电路板

• 支持超过 20MHz的传输带宽

• 可配置在装配体上,用于800MHz - 2.7GHz RF频率

• 20dB RF输出功率调整,分辨率10-bit

• +10dBm RF输出功率

• 符合苛刻的MC-GSM性能要求 (带AD9122)

• 数据转换器的的占用面积与更低规格的型号兼容

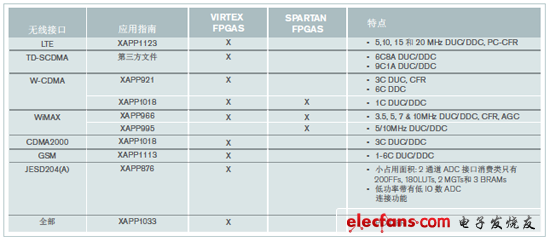

现有的Xilinx无线参考设计小结

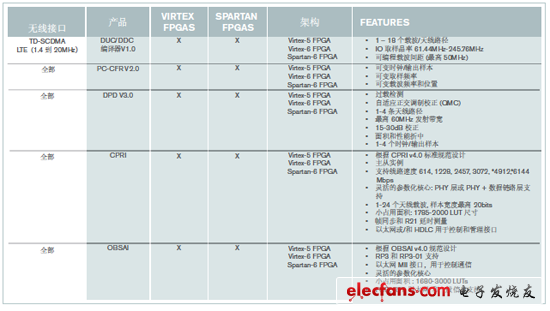

现有的Xilinx无线Logicore IP小结

电子发烧友App

电子发烧友App

评论