一、 引言

现代通信技术、微电子技术和计算机技术的飞速发展,促进了无线通信技术从数字化走向软件化。软件无线电的出现掀起了无线通信技术的又一次革命,它已经成为目前通信领域中最为重要的研究方向之一。所谓软件无线电,是指构造一个通用的、可重复编程的硬件平台,使其工作频段、调制解调方式、业务种类、数据速率与格式、控制协议等都可以进行重构和控制,选用不同的软件模块就可以实现不同类型和功能的无线电台,其核心思想是在尽可能靠近天线的地方使用宽带A/D和D/A变换器,并尽可能地用软件来定义无线功能[1]。

软件无线电具有极大的应用价值和广泛的应用前景。在军事上,不但可以解决不同无线设备间的互连互通,而且还可以现场开发新波形。在商业方面,可实现移动通信的无缝接入和完全自由的个人通信,缩短系统的开发周期和降低运营商的成本,现已成为3G和4G所采用的一项关键技术。

本文研究了中频软件无线电的实现方案,并设计了基于FPGA的通用硬件平台。在此平台上,通过PC机下载软件,实时实现了软件无线电中频至基带的波形处理和多种不同的调制解调方式。

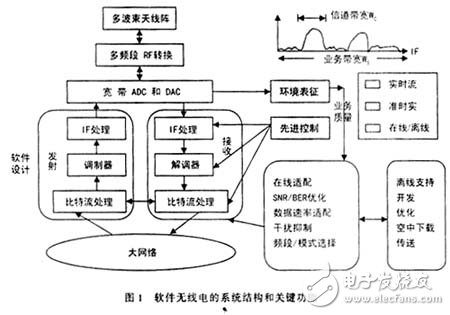

二、 软件无线电的系统结构

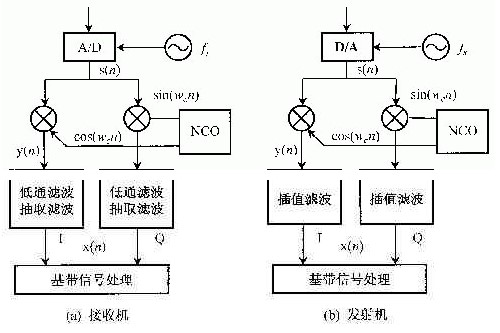

软件无线电赋予了无线电台多种特性。如图1所示,软件无线电用软件定义了包括RF信道接入和波形合成等空中接口的所有方面,宽带ADC和DAC在中频转换每个RF业务频段成为模拟和数字形式,带宽为WS的宽带数字接收机信号流包括了全部用户信道,其中每个用户的带宽Wc《WS 。

在图1所示的软件无线电中,中频ADC和DAC信道可以同时使用可编程的数字硬件和软件来处理。中频处理包括:用来分离用户信道的滤波;数字波束成形;空时联合均衡;空间分集、极化或频率分集信道的综合,以及捕获高质量波形的其它方法。一般情况下,需要多个中频,或者用零中频来处理。数字下变频技术可以利用带通波形抽样信号的频域周期性,将带通波形直接变换到基带。

在软件无线电的发射机中,基带信号由软件实现的信道调制解调器转换成抽样后的信道波形,驱动高性能DAC。中频处理软件还可以对基带信号进行预加重或非线性预编码处理。具体实现时,调制解调功能、中频处理和RF信道接入可以合并成一个部分,例如直接转换接收机。另外,软件或各种特性间实时转换的动态编译允许这些分立的功能集成到一个如FPGA这样的器件中。

三、 中频软件无线电实现方案的研究

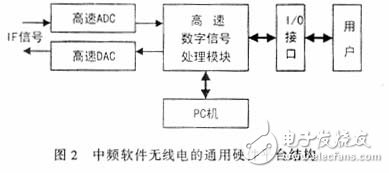

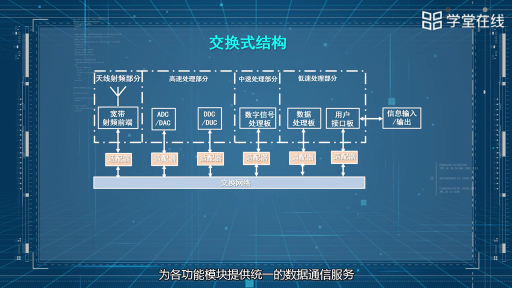

典型的中频软件无线电的通用硬件平台结构如图2所示,包括A/D变换器、D/A变换器、数字信号处理模块和PC机,具有很强的灵活性和高度的开放性。

图2中的数字信号处理模块用来实现多媒体处理、调制解调、波形处理、上/下变频和控制等功能。此模块可以灵活扩展,满足不同无线通信系统对数字信号处理的运算速度和运算量的要求。PC机具有良好的人机接口,可以完成如下功能:初始化系统;提供软件开发环境;实现在线/离线开发应用软件;下载软件到数字信号处理模块等等。

1. 软件无线电中数字信号处理能力所面临的挑战

数字信号处理模块是软件无线电的核心部分。软件无线电要求数字信号处理模块能实时处理ADC变换后的数字信号,并用软件的方法来实现大量的无线电功能,这些功能包括:编解码、调制解调、滤波、同步、盲均衡、检测、数据加密、传输加密纠错、跳扩频及解扩和解跳、通信环境评估、信道选择等,而单个DSP根本无法完成这些功能,对于基站则差距更大。 考虑单个信道的情况,最基本的解调需要10次操作/秒,一个性能良好的FIR/IIR信道选择滤波器需要100次操作/秒,再加上均衡、解交织、信道解码、解复用、差错控制等等。对于一个采样率为30~50MHz的信道,所需要的处理速度很容易就达到了5000MIPS(每秒百万指令)。文献[2]对单信道DSSS(直接序列扩频)军事波形的处理需求进行了估计:此波形的码片速率为10 Mchip/s,ADC的采样率为40 MSPS,数据速率为9 600 bit/s,完成脉冲成形、PN(伪随机)码产生、解复用、解扩/相关、载波同步、跟踪、Viterbi译码、盲均衡和控制等功能;全部所需要的处理速度大约为12.78 GFLOPS(每秒十亿次浮点操作)。现在3G所使用的宽带CDMA技术,单信道所需要的处理速度的量级也与上述军事波形相当,甚至更高。对于基站,由于需要处理很多信道,所需要的处理速度会达到上千GIPS(每秒十亿指令)的量级。

然而目前可用的一些高速DSP的性能,最快的也不超过5 GIPS,与实际需求相差巨大。这种处理资源的匮乏,被称之为DSP瓶颈[3],是影响软件无线电发展的一个至关重要的技术挑战。

2. 实现中频软件无线电系统的传统方法

为解决数字信号处理资源匮乏这一问题,目前实现中频软件无线电系统的传统方法有2种,即用多个DSP实现和用DSP+参数化ASIC实现。

(1)多个DSP方法

这种方法一般采用多个DSP组成树状或网状结构,并行处理数据流,但这种方法最大的弊端是系统体积大、供耗高、成本高。

(2)DSP+参数化ASIC方法

这种系统是目前较多采用的实现方法。在这种系统中,参数化ASIC可有限编程,完成对数字信号处理速度要求较高的部分,DSP做较低速的数字信号处理。这种方法虽然减小了系统的体积,降低了功耗,但是由于参数化ASIC可编程的限制较大,严重地限制了系统的灵活性和开放性,难以体现软件无线电的优越性。

3.用FPGA实现中频软件无线电的优势

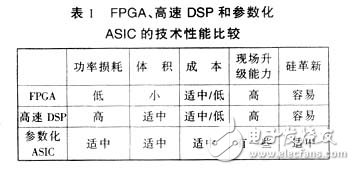

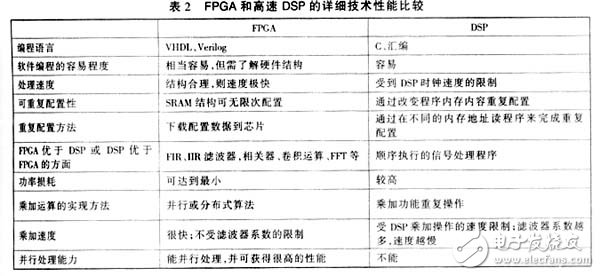

本文采用FPGA来实现中频软件无线电。表1和表2所示的比较分析表明,FPGA与参数化ASIC、DSP比较有很多优势,它不但在功耗、体积、成本方面优于参数化ASIC、DSP,而且处理效率高、现场可编程性能良好。不同于DSP的单流处理方式,FPGA是多流并行处理,这种处理方式使FPGA能完成DSP难以实现的许多功能,如FIR/IIR滤波器、扩频、跳频模式。因此,FPGA能很好地体现软件无线电的灵活性和开放性,很适合在软件无线电中做高速数字信号处理,是实现中频软件无线电的理想选择。

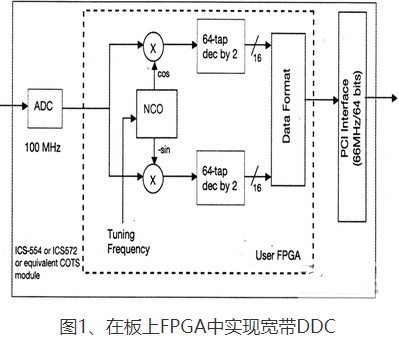

4.采用FPGA实现中频软件无线电系统

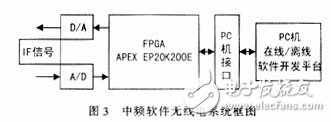

图3为所实现的中频软件无线电系统框图。系统从IF(中频)进行A/D和D/A变换。下面就系统的各部分做一介绍。

1 宽带D/A和A/D转换器

D/A和A/D转换器分别把中频数字信号转换成模拟信号,中频模拟信号转换成数字信号。D/A变换器和A/D变换器的选择,直接关系到软件无线电的总体性能。因此,必须根据系统的要求,综合考虑D/A变换器和A/D变换器的各方面性能,做出选择。

(1)宽带D/A转换器

选用了AD公司的AD9713B,性能指标如下:

1)具有12 bit精度;

2)转换速率最快为80 MSPS;

3)SFDR(无杂散动态范围)为70 dBc。

这里,DAC锁存时钟为40 MHz。AD9713B后接两级放大器,将模拟信号放大后输出。

(2)宽带A/D转换器

在软件无线电中,对ADC的性能要求很高,ADC的选择比DAC更为重要。选择ADC时,需要考虑其采样频率、带宽、转换位数和SFDR。而这几个性能指标是互为约束的,必须综合考虑确定。

在此,ADC选用AD公司生产的AD9042。AD9042是高速、高性能、低功耗的单片12位模/数变换器,其性能指标如下:

1)最大采样速率41 MSPS;

2)SFDR为80 dBc;

3)信噪比为68 dB。

实际使用中,采样时钟为40 MHz,AD9042的性能很好。

2FPGA――数字信号处理模块

FPGA选用了Altera公司的APEX EP20K200E器件,这个器件为20万门容量,1.8 V低功耗,具有多种I/O接口和多钟配置方式的单片系统级集成的可编程逻辑器件。

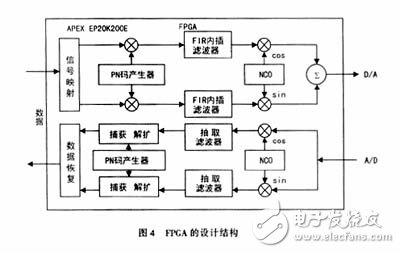

FPGA主要完成数字上/下变频、滤波、调制/解调、扩频/解扩、载波以及PN(伪随机码)的同步和跟踪等功能。

FPGA的设计结构如图4所示。在此,以DSSS(直接序列扩频)信号为例说明。发射的设计为,系统将125 kbit/s的数据映射成上下支路各62.5 kbit/s的数据与PN码产生器输出的4Mchip/s的PN码相乘扩频,然后由14 bit 的FIR滤波器完成内插滤波,滤波器输出的信号为20 MHz,与NCO相乘上变频至中频,并取高12 bit输出至D/A变换器。接收的设计与发射相对应,A/D变换器输出的40 MHz的12 bit中频数字信号与NCO相乘正交下变频成I、Q两路信号,这2路信号经抽取滤波变为20 MHz的基带信号,输入到解扩电路完成PN码的捕获、解扩(用[HJ71mm]?匹配滤波器相关器实现)以及信号相关后的功率检测,解扩后的信号和检测到的功率信号输入到码跟踪电路完成码元跟踪,最后完成解码,恢复数据。完成这些功能,所占的FPGA资源为:7142个LE(逻辑单元),16896 ESB(嵌入式逻辑块) bits。

3 PC机及其接口

PC机为FPGA提供软件开发环境,完成在线/离线的软件开发和调试,并通过RS232口与FPGA通信,实时下载软件到FPGA。

五、系统性能

系统采用FPGA完全实现了中频软件无线电系统的软件可编程,具有很高的灵活性、开放性和通用性。设计的FPGA软件模块,如NCO、数字滤波器等可为多种调制/解调模式所使用。各种调制/解调模式相应的配置软件以文件的形式存储在微机里,可根据具体要求下载到FPGA,从而实现调制/解调模式的实时改变。经测试,系统采用的时钟为40 MHz时,可达到的工作性能如下:

(1)中频载波:可以任意设置,最高可达16 MHz,最大频率误差为0.009 Hz;

(2)信息速率:可变,最高可达4 Mbit/s;

(3)调制/解调模式:通过更换软件,系统可实现AM、PM、FM、BPSK、QPSK、DSSS等模式。

六、 结论

FPGA在软件无线电中的应用已经越来越被人们所重视。用FPGA来实现中频软件无线电系统具有很高的灵活性和开放性,充分体现了软件无线电的优越性,是当前实现软件无线电技术的理想方案。

电子发烧友App

电子发烧友App

评论