作者: OpenSLee 1 概述 在数字信号处理中,CIC滤波器是FIR滤波器中最优的一种,其使用了积分,梳状滤波器级联的方式。 CIC滤波器由一对或多对积分-梳状滤波器组成,在抽取CIC中,输入

2020-12-05 10:21:00 2654

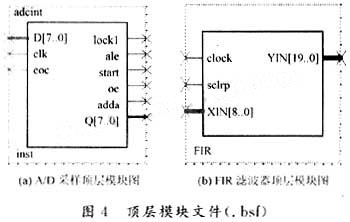

2654 fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

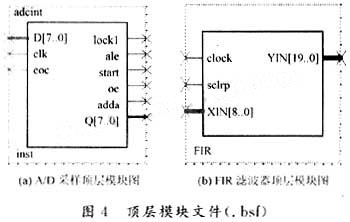

。本文研究了一种16阶FIR滤波器的FPGA设计方法,采用Verilog HDI语言描述设计文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平台上进行了实验仿真及时序分析,并探讨了实际工程中硬件资源利用率及运算速度等问题。

2012-08-11 18:27:41

做出取舍,才能设计出符合需求的解决方案。在设计滤波器以满足已知要求的过程中,有许多既有的挑战。这些要求主要是在电气、机械和环境方面。从系统级设计所提出的约束,例如机械尺寸之类,通常都具有极高的重要性

2019-06-24 07:21:26

。BAW 中的声波以垂直方式传播,而 SAW 滤波器则采用水平行进路径。它如何过滤掉特定的频率?谐振频率与薄膜厚度成反比,这同时适用于金属和介电层。例如,减少顶层金属的厚度可以增加共振频率。这就

2019-10-28 08:00:00

滤波器是一种选频装置,可以使信号中特定的频率成分通过,而极大地衰减其它频率成分。一、概述1、定义凡是可以使信号中特定的频率成分通过,而极大地衰减或抑制其他频率成分的装置或系统都称之为滤波器,相当于

2019-06-24 07:15:11

详解面向TDD系统手机的SAW滤波器的技术动向

2021-05-10 06:18:34

带通滤波器(BPF)被广泛用于通带非常窄、通带以外任何其它频率被衰减的应用。公式(1)是带通滤波器的二阶带通传输函数:其中,K代表恒定的滤波器增益,Q代表滤波器的品质因数。

2019-06-24 07:23:07

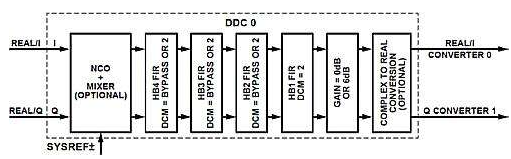

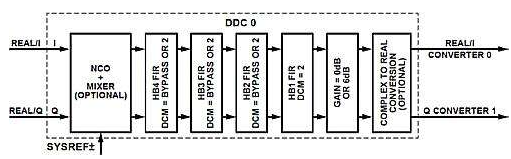

AD9689芯片 DDC抽取滤波器进行多芯片同步时使用什么信号进行复位同步?是sysref信号还是什么?datasheet没有提供说明。

2023-12-07 06:43:42

你好!在使用AD9789芯片的过程中,发现中文和英文数据手册的P44页有不对应的地方,16倍数字可调带通滤波器公式中,中文数据手册中最高中心频率为Fdac/2,而英文数据手册中最高中心频率为Fdac,请问以哪个参考为准,谢谢!

2018-11-16 10:10:37

分别为1MSPS和1.8MSPS,为过采样带来了具有重要意义的可能性,特别是音频频段或更高频段。为此,必须在外部FPGA或DSP中搭载定制型抽取滤波器。如前所述,可以绕过后者,以在必要时将其延迟降至最低

2021-08-04 07:00:00

CIC抽取滤波器MATLAB仿真和FPGA实现(1)设计理想滤波器目标:1、滤波器在有效频段内纹波满足设计要求。2、抽取或内插处理后在有效频段内不产生混叠。3、滤波器实现简单,需要资源较少。这个

2021-08-17 08:27:40

什么是抽取?DDC的作用是什么?DDC滤波器应该多宽?DDC滤波器的频率是固定的吗?DDC滤波器是否影响SNR和SFDR?ADC能否提供多个DDC?

2021-05-21 06:34:42

, 只需要对一个指令积习循环就可以完成FIR计算。 适合于多采样率转换,它包括抽取(降低采样率), 插值(增加采样率)操作, 无论是抽取或者插值,运用FIR滤波器可以省去一些计算,提高计算效率, 相反

2011-09-24 16:05:53

输入数据和历史输入数据,IIR的滤波输出取决于当前输入数据、历史输入数据和历史输出数据。以基于FPGA硬件的数字滤波器为例,FIR在处理信号时不需等待前一个信号的滤波输出,只需要考虑输入数据便可实时

2019-06-27 04:20:31

PIC32 MZ2048 EFM100 HORDER 2.04i AM在函数中运行DSP1 FieldFixIM32()时存在问题。DSP滤波功能,DSPFILTERFIL32()没有内部抽取,工作

2018-08-24 16:00:33

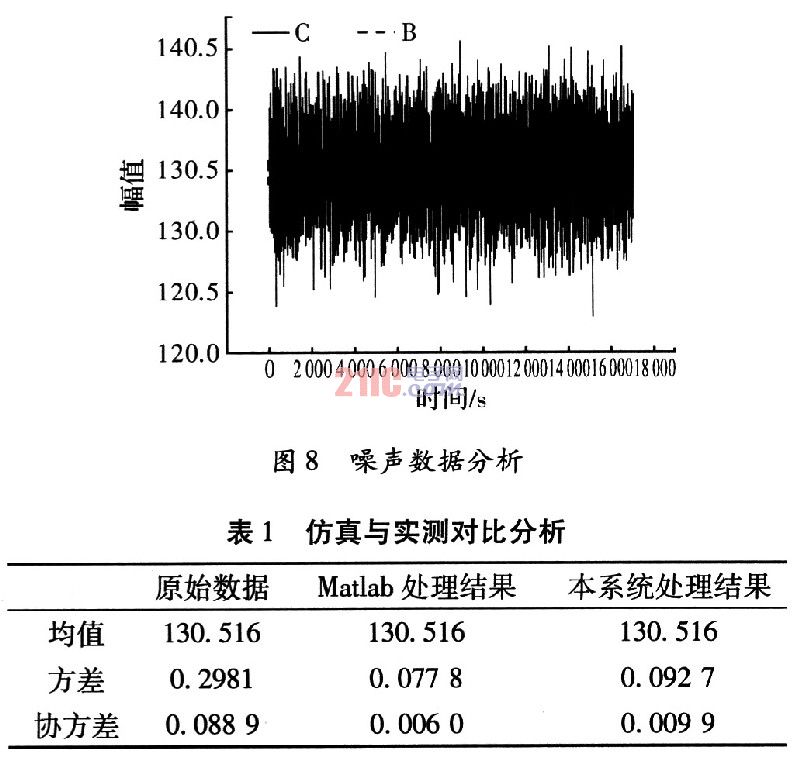

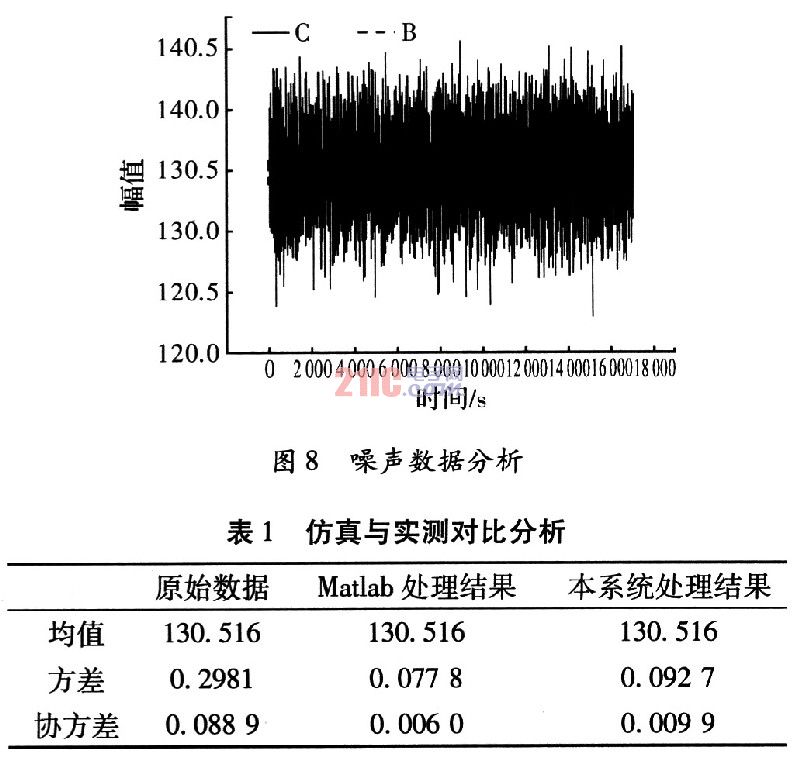

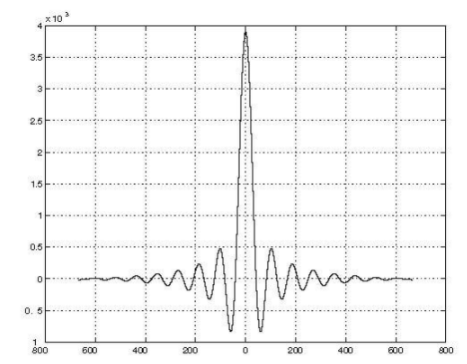

FIR滤波器工程说明本案例设计了一个15阶的低通线性相位FIR滤波器,采用布莱克曼窗函数设计,截止频率为500HZ,采样频率为2000HZ;实现全串行结构的滤波器;采用具有白噪声特性的输入信号,以及

2017-08-02 17:35:24

我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR)的因子抽取调制器采样频率

2018-08-30 15:05:47

通带数字滤波器。正如我的同事Ryan Andrews在其关于抗混叠滤波器的博文中解释道,Σ-Δ ADC中的数字滤波器具有另外一项抽取功能。这些滤波器以低很多的速率(fDR)通过被称为过采样率(OSR

2018-08-30 14:51:23

分数速率的转换6.4 6个恒等式及其典型应用6.4.1 与抽取操作有关的恒等式6.4.2 与插值操作有关的恒等式6.4.3 典型应用6.5 多相滤波器6.5.1 多相抽取滤波器的基本理论6.5.2 多相

2012-04-24 09:33:23

中滤除其中需要的窄带信号,可降低数据流速率,以满足后续的DSP器件处理,其实现的关键是要找到一个高效的抽取滤波器。C IC(Cascaded Integrator Com b)滤波器[1]只有加法和延迟单元,不必要像一般的F IR滤波器有复杂的乘法计算,是一个很好的全文下载

2010-06-02 10:07:03

kHz 比音频信号带宽20~20kHz 大得多 为了从 PWM 开关信号中恢复出音频信号 通常采用低通滤波器 LPF 低通滤波器频率特性如图 1所示图 2 与图 3 为 PWM 滤波前后的时域与频域

2011-11-07 14:46:21

主要任务:1.熟悉低通滤波器的原理及应用2.熟悉FPGA的硬件描述3.FPGA如何实现小数分频器4.用MATLAB对低通滤波器的验证预期成果或目标:FPGA对低通滤波器的Verilog(或VHDL

2013-04-04 22:16:11

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

是π,因此我们得出,抗混叠低通滤波器的截止频率是π/M1.3内插抽取的过程是降低采样率的过程,那么插值的过程当然就是提高采样率的过程。大体的思路可以这么理解,我们将经f1抽样下得到的数字信号的每两个点

2018-11-15 00:27:19

的关系CIC滤波器通常用于抗混叠抽取/内插滤波器(抽取与内插结构见本文开头的链接)。考虑抽取/内插的过程、CIC滤波器的特性(系数为1的特殊FIR滤波器)以及FIR滤波器的实现结构,就会发现,当CIC

2020-09-28 09:36:54

/3位置处。)最简单的滤波器类型为RC滤波器,如图3中基于低电流ADP161x升压设计的输出端所连接的那样。该滤波器具有低成本优势,无需阻尼。但是,由于功耗的原因,它仅对极低输出电流转换器有用。本文

2023-02-11 07:00:00

我正在尝试在级联模式下配置抽取滤波器,Block A 和 B 的基本配置已完成。ADC 触发基地。我已将 ACR1 配置为将 ADC 结果发送到滤波器块而不是 RFIFO,转换命令根据 ACR1 使用备用配置命令进行更新。我仍然无法在 TAP 寄存器中看到任何值。

2023-05-25 07:38:45

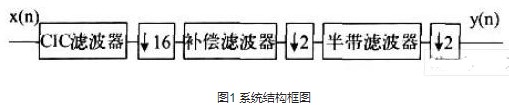

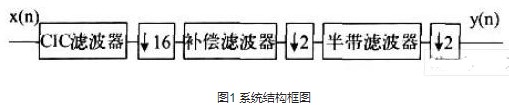

设计一般采用CIC、HB、FIR级联的形式组成。同时,由于CIC滤波器的通带性能实在太差,所以中间还要加上一级PFIR滤波器以平滑滤波器的通带性能。

2019-09-20 06:13:11

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于FPGA的FIR滤波器设计与实现 文章研究基于FPGA、采用分布式算法实现FIR滤波器的原理和方法,用

2012-08-11 15:32:34

源码-基于FPGA设计的插值滤波器设计.rar (12.14 KB )

2019-05-08 06:35:28

成长,CIC低通滤波器得到了广泛的应用。长期以来,CIC梳状滤波器一般是在通用DSP处理器上实现的,由于DSP处理器的顺序执行特性的限制,其速度很难满足一些高速抽取与插值系统的需要。FPGA具有优良的全硬件并行执行的特性,研究CIC梳状滤波器的设计及其FPGA实现具有重要的现实意义。

2019-09-23 07:22:30

在电子设备中,到处都可以看到数字信号处理(DSP )的应用,从MP3播放器、数码相机到手机。DSP设计人员的工具箱的支柱之一是有限脉冲响应(FIR )滤波器。FIR滤波器越长(有大量的抽头),滤波器

2019-07-08 08:01:03

本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2021-04-29 06:50:18

滤波器在FPGA中的实现用FPGA来实现滤波器的设计优点用FPGA来设计滤波器,不但设计简单,而且成本小,可靠性好。且无需像传统的设计芯片一样进行测试。主要优点:设计简洁。若设计有误,则只需

2021-07-30 07:03:10

在信号处理中,滤波器的系数我们往往都是通过MATLAB来设计,只要我们知道滤波器的通带截止频率和阻带起始频率,就可以通过MATLAB中的fdatool(在MATLAB2020中

2020-12-24 16:03:16

在现代电子系统中,到处都可以看到数字信号处理( DSP )的应用,从MP3播放器、数码相机到手机。DSP设计人员的工具箱的支柱之一是有限脉冲响应( FIR )滤波器。FIR滤波器越长(有大量的抽头

2019-10-22 06:55:44

技术优化由FIR理论知:要满足基本的滤波器衰减和噪声特性要求,抽取系数为N的单个滤波器需要大量的抽头(乘法器)才能实现。最新的Virtex-5系列FPGA内嵌的DSP48E模块(主要包含硬件乘法和加

2009-10-23 10:26:53

本文将针对中频PCM/DPSK遥测信号全软化解调器中数字级联抽取滤波器的设计及软化实现进行研究。

2021-06-04 07:07:09

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2021-05-07 06:02:47

为什么要设计一种理想滤波器呢?CIC抽取滤波器是由哪些部分组成的?怎样去设计一种CIC抽取滤波器并对其进行MATLAB仿真呢?

2021-11-19 07:29:44

在我的上一篇文章中,我讨论了增量-累加模数转换器 (ADC) 的2个重要特点。这2个特点简化了抗混叠滤波器的设计:一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号

2018-09-05 14:52:59

分方程如下所示:由差分方程可知IIR滤波器存在反馈,因此在FPGA设计时要考虑到有限字长效应带来的影响。差分方程中包括两个部分:输入信号x(n)的M节延时网络,相当于FIR的网络结构,实现系统的零点

2020-09-27 09:22:58

各位大侠,小弟最近要设计一个用于sigma-delta ADC的数字抽取滤波器,甚是着急,但是苦于毫无头绪,敬请各位高手指点啊。下面是设计指标: 信号频率为250hz,调制器采样频率频率为

2012-02-26 22:00:16

各位大侠,小弟最近要设计一个用于sigma-delta ADC的数字抽取滤波器,甚是着急,但是苦于毫无头绪,敬请各位高手指点啊。下面是设计指标: 信号频率为250hz,调制器采样频率频率为

2012-02-26 15:52:55

的NCO的数字调谐字提供采样速率的小数分频,通过分辨率位数提供精确定位。调谐字具有范围和分辨率,可以将滤波器按频谱放置在需要的地方。滤波器的通带应与抽取后的转换器的有效频谱宽度相匹配。使用DDC的显著优势

2018-10-24 09:56:03

【作者】:李学易;郝禄国;卢晓锋;【来源】:《电视技术》2010年02期【摘要】:就DVB/CMMB数字回波消除直放站研发中涉及的抗混频数字抽取滤波器这一关键技术进行了详细研究,对3种数字抽取滤波器

2010-04-22 11:30:26

中注入 的噪声。在实际应用中,采样速率远高于奈奎斯特理论指出的 两倍基频信号频率。因此,后置数字滤波器可以利用针对更高 信噪比和更高分辨率的滤波技术来降低转换过程中注入的噪 声,例如:信号带宽之外

2018-10-16 18:45:40

于Δ-Σ模数转换器中?我在上篇博文中提到,“正弦”的名称源于它的以sin(x)/ x函数形式存在的频率响应。该滤波器具有这种反应的原因与它为什么常用于Δ-Σ模数转换器密切相关。在特定数目的调制器时钟周期

2018-08-30 14:51:19

利用matlab设计一个线性相位FIR带通滤波器,并在FPGA上实现。要求:1、滤波器指标:过渡带带宽分别为100~300HZ,500~700HZ,阻带允许误差为0.02,通带允许误差为0.01,采样

2015-06-16 19:25:35

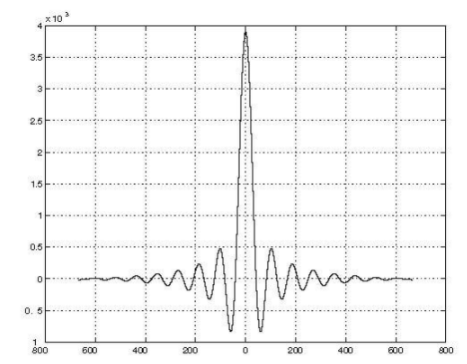

FIR抽取滤波器的通阻带容限为0.14、可以采用matlab为我们提供的firhalfband函数来设计半带滤波器,设计过程很简单,函数直接返回FIR半带滤波器系数。关于firhalfband函数

2015-08-29 15:33:49

我们得出:镜像低通滤波器的截止频率为:π/D四、分数倍抽取与内插根据前面抽取与内插的介绍我们知道了,内插的过程是先进行内插处理,再通过镜像低通滤波器,抽取的过程就是先进行抗混叠低通滤波,再进行抽取

2015-08-29 15:25:38

,得到相应阶数的滤波器系数,量化并进行16进制转换供FPGA使用。 前面说了,多相结构的FIR滤波器是在算法上下功夫,所以本身滤波器的设计过程就是普通滤波器的设计过程,并没有什么不同,下面再来看多相

2015-08-29 15:37:11

FPGA收发器资源可以得到更好的分配,以接收所需的低带宽并疏导来自多个ADC的数据。可在FPGA的多相滤波器组信道器中针对频分复用 (FDM) 应用进行额外滤波。高性能GSPS ADC现将数字下变频

2019-06-14 05:00:09

探讨了DDC中抽取滤波系统的设计方法和基于DSP Builder的具体实现方案,采用CIC滤波器、HB滤波器、FIR滤波器三级级联的方式来降低采样率,并进行了模型仿真,结果表明设计是可行的

2009-09-17 11:35:08 23

23 插值和抽取滤波器被广泛应用于现代通信系统中,然而基于传统DSP 或者FPGA 的滤波器,具有数据率低和占用资源多的缺点。为了克服这些缺点,本文针对一种多核DSP 处理器, 提出

2009-11-27 15:26:57 9

9 在软件无线电的下变频模块中,级联梳状积分滤波器有着重要的应用,其主要作用是信号的抽取与低通滤波。文中总结了级联梳状积分抽取滤波器的理论要点,并介绍了采用FPGA

2010-01-06 15:16:45 31

31 设计一个由现场可编程门阵列(FPGA)控制的滤波器。该滤波器主要由3个模块组成:前置放大、滤波电路、FPGA显示与控制电路等利用FPGA作为放大器及程控滤波器电路中继电器组的控制模

2010-07-17 18:00:09 45

45 基于FPGA的数字滤波器的设计与实现

在信息信号处理过程中,如对信号的过滤、检测、预测等,都要使用到滤波器,数字滤波器是数字信号处理中使用最广泛的一

2010-01-07 10:45:35 3474

3474

FPGA的Kalman滤波器的设计

摘要:针对电路设计中经常碰到数据的噪声干扰现象,提出了一种Kalman滤波的FPGA实现方法。该方法采用了TI公司的高精度模数转换

2010-04-13 13:32:46 2566

2566

摘 要:为了降低地震数据采集系统的成本和功耗,采用数字信号处理器(DSP)实现-△模数转换器中的数字抽取滤波器算法。通过采取查表法、倒序循环遍历法以及模拟循环寻址法等优化方法,以较低工作频率实现了四通道四级抽取滤波运算,达到了系统设计的要求。

2011-02-25 16:00:23 68

68 为补偿传统CIC滤波器的通带衰减,提出一种改进型的CIC抽取滤波器,即在SCIC滤波器之后级联一个二阶多项式内插滤波器。基于硬件实现的要求,给出改进型CIC滤波器的FPGA高效实现原理图。仿真结果表明改进的CIC滤波器具有更好的通阻带特性。

2011-03-15 14:06:35 52

52 为了解决高速抽取滤波器系统中传统CIC滤波器旁瓣抑制不够的问题,通过对级联COSINE抽取滤波器和传统CIC抽取滤波器的原理推导进行对比,分析出级联COSINE滤波器在幅频特性上同CIC滤波

2011-05-03 18:11:53 31

31 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影

2011-08-26 15:12:11 160

160 文中基于多速率数字信号处理原理,设计了用于数字下变频技术的CIC抽取滤波器。通过分析CIC滤波器的原理及性能参数,利用MATLAB设计了符合系统要求的CIC滤波器,并通过FPGA实现了CI

2013-04-15 19:29:28 71

71 4阶24倍抽取CIC滤波器设计,有兴趣的同学可以下载学习

2016-04-27 15:51:58 26

26 ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上实现了一种下采样率为64的抽取滤波器。Modelsim仿真结果表明,该抽取滤波器设计是有效的,达到了设计指标。

2017-11-17 09:01:55 5303

5303 设计了采样频率为640 MHz、过采样率为64的高频数字抽取滤波器。该数字抽取滤波器由CIC(Cascaded Integrator Comb)滤波器(降16倍)、CIC补偿滤波器

2018-02-21 12:08:00 1815

1815

文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。

2018-04-19 11:34:00 1846

1846

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1072

1072

数字抽取滤波器是ΣΔADC(ΣΔAnolog-to-Digital Converter)的重要组成部为分,旨在从高速、低分辨率的调制信号中重构出高分辨率、奈奎斯特频率的信号。为节约硬件资源,同时满足

2018-06-29 14:32:00 11289

11289

∑-△调制器与数字抽取滤波器是∑-△ ADC 实现16bit 以上精度的关键电路模块。∑-△调制器依靠过采样与高阶闭环负反馈控制实现的噪声整形技术,将基带内的量化噪声搬移到高频段,而数字抽取滤波器

2019-05-08 08:18:00 3969

3969

滤波器系数决定滤波器特性,理论上讲,只用一组滤波器系数是不能实现可变参数滤波器的。由2节可知,下抽取率N与滤波器截止频率成反比,与阻带衰减成正比,与滤波器长度成正比。假设下抽取率为N0时滤波器系数h(n),n=0,1,2…L-1,我们怎样通过h(n)这组基准系数来获得N不等于N0时的滤波器系数呢?

2018-10-26 14:37:36 7976

7976

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

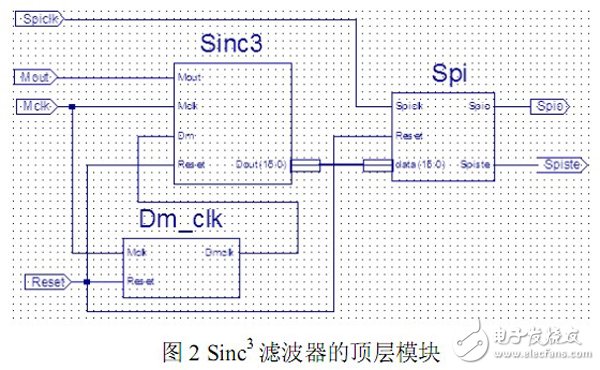

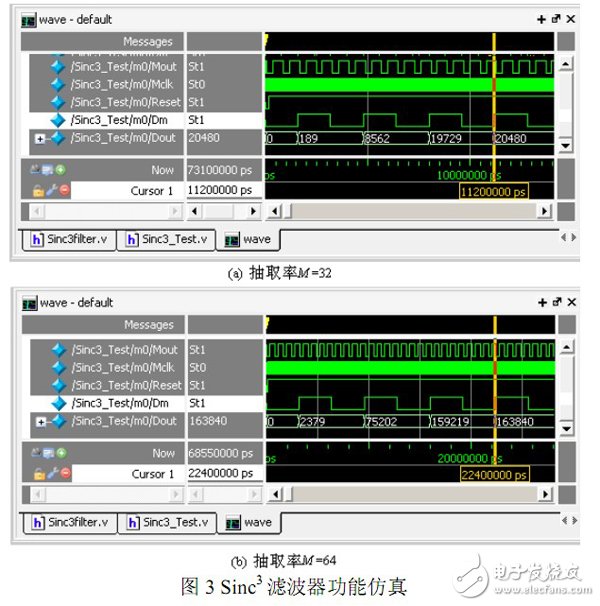

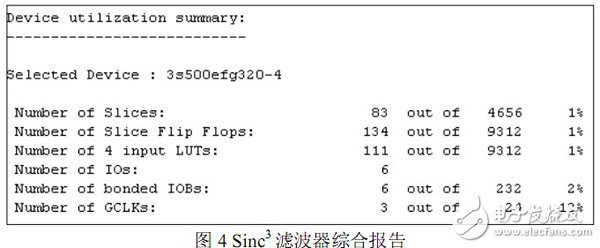

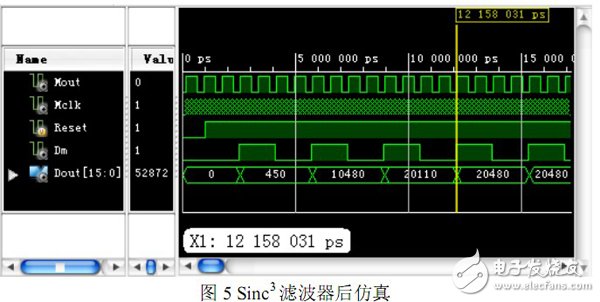

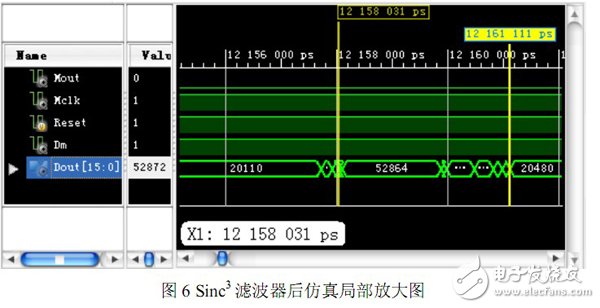

3 针对Σ△ADC输出端存在的高频噪声问题,设计了一种 Sinc数字抽取滤波器,实现了Σ-△调制器输出信号的高频滤波。分析了Sinc滤波器的结构原理,基于 Spartan6FPGA进行滤波器的设计与实现

2020-08-26 17:12:00 14

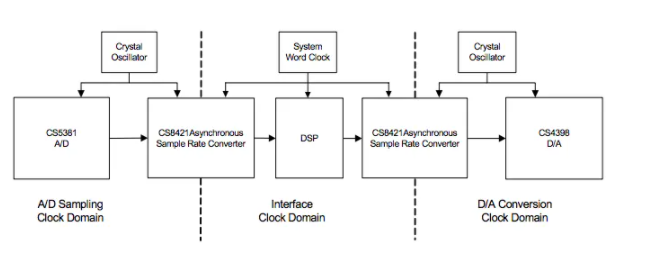

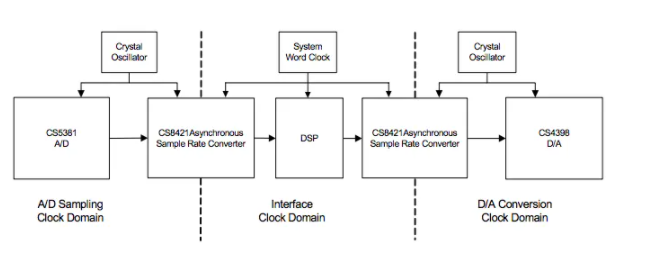

14 本应用笔记将介绍带有异步抽取滤波器的音频模数转换。它提出了转换过程对高频系统时钟的要求,并提出了这种音频转换的解决方案。 介绍 现代高性能 delta-sigma 模数 (A/D) 和数

2021-06-04 17:48:49 1290

1290

本白皮书介绍了有关抽取和插值滤波器的新观点。它提供了有关这些滤波器的简要介绍和历史观点,以及信号等待时间的可听性,IIR滤波器的适用性和相位失真的可听性。 引言和历史观点 早期的数字音频转换系统需要

2021-05-25 11:22:59 8369

8369

基于FPGA的_ADC数字抽取滤波器Sinc_3设计(现代电源技术基础杨飞)-该文档为基于FPGA的_ADC数字抽取滤波器Sinc_3设计总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 13:58:04 20

20 一阶有源滤波器原理详解

2022-11-14 09:52:23 1934

1934 二阶有源高通滤波器原理详解

2022-11-18 09:48:10 2685

2685 二阶有源带通滤波器原理详解

2022-11-21 11:00:49 2751

2751 我们将再次以AD9680为例。在这种情况下,无论速度等级如何,归一化抽取滤波器响应都是相同的。抽取滤波器响应仅随采样速率成比例。在此包含的示例滤波器响应图中,没有准确给出具体的插入损耗与频率的关系

2023-06-30 15:43:41 1667

1667

电子发烧友App

电子发烧友App

评论