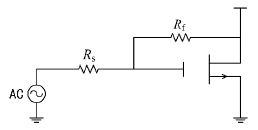

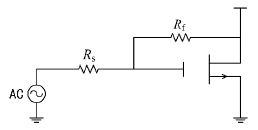

低噪声放大器是无线接收系统中第一个模块,影响着整个系统的噪声性能和灵敏度等参数。随着超宽带技术的发展,宽带低噪声放大器设计已成为当前设计的一个热点。根据目前国内外发表的相关文献,当前宽带低噪声放大器的结构大致有带通滤波网络匹配和电阻负反馈2 种结构。

2018-09-05 08:11:00 4577

4577

低噪声放大器设计资料

2022-11-22 09:16:52 712

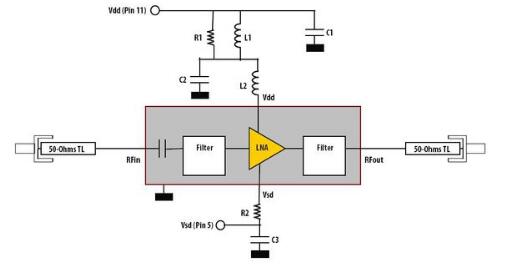

712 低噪声放大器低噪声放大器(LNA)被用来将天线收到的微弱的无线蜂窝信号,放大到混频器所需要的幅度。如果低噪声放大器损坏,通常会造成手机接收信号差的故障。低噪声放大器通常又称为前置射频放大器,前置

2021-07-27 07:57:52

更少,放大器是当今RF/IF信号链中功能最多样的构建模块之一;想请教一下大牛 ;低噪声放大器和中频放大器有什么样的特性?

2021-04-07 06:52:54

低噪声放大器除了用于接收机的信号放大以外,在测试和测量中也经常用到。以下列举了一些低噪声放大器在射频测试和测量中的典型应用。一、用于电磁环境测量电磁环境测量是保证各类无线电业务正常开展的必要环节

2017-11-08 10:10:46

低噪声放大器除了用于接收机的信号放大以外,在测试和测量中也经常用到。以下列举了一些低噪声放大器在射频测试和测量中的典型应用。一、用于电磁环境测量电磁环境测量是保证各类无线电业务正常开展的必要环节

2018-01-23 09:52:05

低噪声放大器在无线数据接收中有哪些应用?

2019-08-23 07:08:00

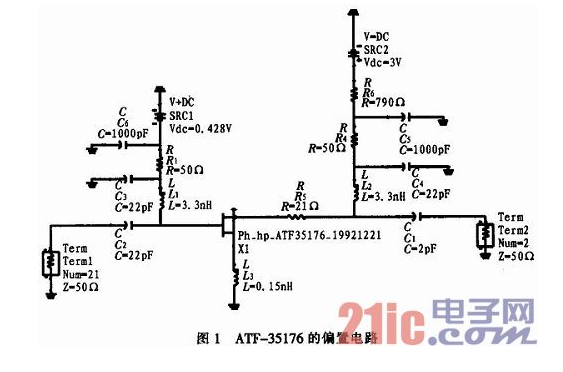

低噪声放大器设计 线性仿真

2019-03-15 17:23:22

低噪声放大器(LNA)是怎样提出来的?低噪声放大器(LNA)有哪些优势?低噪声放大器(LNA)主要应用在哪些领域?

2021-04-23 06:46:07

`低噪声放大器,噪声系数很低的放大器。一般用作各类无线电接收机的高频或中频低噪声前置放大器,以及高灵敏度电子探测设备的放大电路。在放大微弱信号的场合,放大器自身的噪声对信号的干扰可能很严重,因此希望

2017-09-11 15:43:24

ADS设计低噪声放大器的详细步骤

2012-08-20 07:56:37

(频分多址)和TDMA(时分多址)相比,具有系统容量大而且配置灵活、频谱利用率高、软切换、保密性能好的优点。基于这些优点CDMA技术得到了广泛的应用。 CDMA低噪声放大器作为CDMA接收机的第一

2019-06-19 07:03:12

(频分多址)和TDMA(时分多址)相比,具有系统容量大而且配置灵活、频谱利用率高、软切换、保密性能好的优点。基于这些优点CDMA技术得到了广泛的应用。CDMA低噪声放大器作为CDMA接收机的第一

2019-07-09 08:14:06

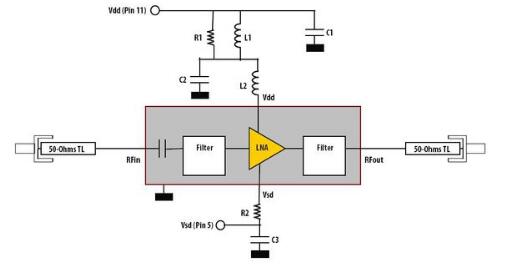

CMD132是Custom MMIC的X波段宽带低噪声放大器,该放大器适用于C波段和X波段的微波无线放大器应用,MMIC提供设计和测试服务,其中产品RF毫米波电路可用于卫星通信,雷达系统,蜂窝

2019-07-17 10:13:32

如何优化LNA的指标?MAX2640低噪声放大器用于ISDB-T设计,有什么优势?

2021-04-20 07:13:51

` 本帖最后由 330538935 于 2018-6-13 17:56 编辑

QPB9331低噪声放大器产品介绍QPB9331报价QPB9331代理QPB9331咨询热线QPB9331现货

2018-06-13 17:37:43

RFFM4527低噪声放大器产品介绍RFFM4527报价RFFM4527代理RFFM4527咨询热线RFFM4527现货,王先生深圳市首质诚科技有限公司RFFM4527是一个低噪声放大器(LNA

2018-06-14 14:55:20

`SPF5043Z 低噪声放大器产品介绍SPF5043Z报价SPF5043Z代理SPF5043Z咨询热线SPF5043Z现货,王先生深圳市首质诚科技有限公司SPF5043Z一种高性能GaAs

2018-06-22 10:28:00

目前,有关低噪声放大器的讨论常常关注于RF/无线应用,但实际应用中,噪声对于低频模拟产品(如数据转换器缓冲、应变仪信号放大和麦克风前置放大器)也有很大影响,是一项重要的考虑因素。为了选择一款合适

2018-12-19 13:56:15

为什么低噪声放大器的第一级要尽可能的放大?

2023-11-21 08:01:12

1、低噪声放大器在通讯系统中的作用随着通讯工业的飞速发展,人们对各种无线通讯工具的要求也越来越高,功率辐射小、作用距离远、覆盖范围大已成为各运营商乃至无线通讯设备制造商的普遍追求,这就对系统的接收

2019-06-20 06:15:56

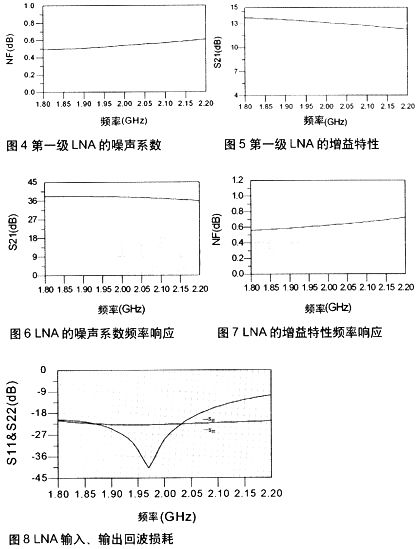

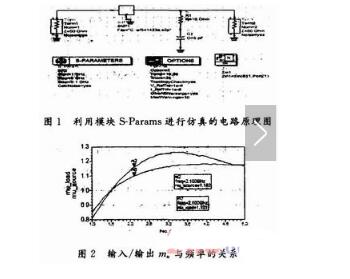

【作者】:宫波;李淑华;【来源】:《电子设计工程》2010年02期【摘要】:介绍接收机前端的低噪声放大器(LNA)对于整个通信设备的接收机系统灵敏度的影响,利用ADS软件对接收机低噪声放大器进行改进

2010-04-24 09:02:08

低噪声放大器是通信、雷达、电子对抗及遥控遥测系统中的必不可少的重要部件,它位于射频接收系统的前端,主要功能是对天线接收到的微弱射频信号进行线性放大,同时抑制各种噪声干扰,提高系统的灵敏度。特别是随着

2019-08-01 06:31:15

低噪声放大器性能指标及设计步骤根据噪声最小设计输入匹配电路如何利用ADS仿真器设计低噪声放大器?

2021-04-22 07:24:57

请问如何利用ATF-54143设计一款低噪声放大器?

2021-04-21 06:56:50

为什么要设计低噪声放大器?请问如何利用ATF54143设计低噪声放大器?

2021-04-13 06:26:22

如何采用CHRT的0.35μm RFCMOS工艺,在EDA软件IC 5.1设计环境中设计了一个2.4 GHz的低噪声放大器?

2021-04-12 06:41:55

如何设计一种集成度高、匹配方便的宽带低噪声放大器?

2021-04-02 07:06:59

放大器设计对噪声性能的影响是什么常见放大器设计的典型噪声参数如何正确选择低噪声放大器?

2021-04-14 06:17:09

射频前端低噪声放大器(LNA)电路是无线电设备前端电路设计中的重要内容。由于实际的无线电传播环境通常较为恶劣,因此,其射频前端电路中必须考虑采用LNA。LNA作为射频模块中的关键电路,其噪声大小

2019-08-01 06:34:15

如何进行宽频带低噪声放大器的设计?选择平衡式电路结构来进行宽频带低噪声放大器的设计有什么优势?

2021-04-06 07:18:10

近年来在射频通讯接收机中,低噪声放大器的噪声,增益和线性度直接影响着整个射频前端的性能,因此它成为整个射频前端设计的关键所在。其中,宽带低噪声放大器成为近年来的国内外的研究热点。宽带低噪声放大器主要

2010-05-13 09:06:35

TOP1 射频低噪声放大器电路 射频LNA设计要求:低噪声放大器(LNA)作为射频信号传输链路的第一级,它的噪声系数特性决定了整个射频电路前端的噪声性能,因此作为高性能射频接收电路的第一级LNA

2021-07-28 08:51:10

的体积要大过低噪声放大器(LNA)。功率放大器的工作电流在安培数量级,而LNA只需要毫安级的电流。

2019-06-19 08:25:12

怎么实现WCDMA分布式基站低噪声放大器电路设计?

2021-06-07 06:22:33

、传感器网络将逐渐引领人类步入“网络即传感器”的传感时代。 低噪声放大器LNA ( low noise amp lifier)是射频接收前端的主要组成部分。由于位于接收前端的第一级,直接与天线相连

2019-08-22 06:06:08

怎样设计和仿真低噪声放大器?有什么流程?低噪声放大器技术指标与设计原则低噪声放大器设计步骤

2021-04-07 06:19:47

在雷达或无线电接收器中,敏感型低噪声放大器 (LNA) 在承受较大的输入信号时必定会发生损坏。那么,有什么解决方案?

2019-08-02 06:26:46

0 引言在雷达射频接收系统中,对系统性能指标的要求越来越高,其中低噪声放大器是影响着整个接收系统的噪声指标的重要因素。与普通的放大器相比,低噪声放大器作用比较突出,一方面可以减少系统的杂波干扰,提高

2019-07-09 06:08:25

基于HP41511的微波低噪声放大器的设计

2021-04-06 09:12:27

如何去设计一种2.4 G的低噪声放大器?对2.4 G的低噪声放大器怎样进行仿真?

2021-04-21 06:17:57

高线性低噪声放大器的工作原理是什么?高线性低噪声放大器该如何去设计?怎样对高线性低噪声放大器进行电磁仿真?

2021-04-22 06:34:26

为什么低噪声放大器的第一级要尽可能的放大?

2018-08-24 07:15:03

怎么设计一种2.5GHz WiMAX低噪声放大器?

2021-04-20 06:27:09

怎样去设计一种低噪声放大器?如何对低噪声放大器进行仿真?

2021-05-26 06:04:52

怎样去设计全集成的低噪声放大器?怎样对全集成的低噪声放大器进行模拟仿真?

2021-04-21 06:18:40

怎样可以提高低噪声放大器的测量精度?低噪声放大器的特点和应用有哪些?如何精准的测量低噪声放大器的各种指标参数?网络分析仪系统是如何构成的?低噪声放大器传统的测试方法中存在哪些问题?

2021-04-14 06:59:08

一种多模低噪声放大器电路:

一种多模低噪声放大器电路,其适合多个射频接收标准,是一种共源共栅结构的窄带放大器,其特征在于,包括:输入匹配

2007-07-16 23:37:54 23

23 Ka波段低噪声放大器的研镧:本文介绍了~种毫米波低噪声放大器的设计技术,应用CAD技术设计了波导到微带的过渡,结合其它电路设计和组装工艺,研制出了工作带宽为3GHz的Ka波

2009-11-01 14:56:59 16

16 射频低噪声放大器的ADS设计:本文首先简要介绍了低噪声放大器设计的理论基础,并以2.1-2.4Ghz 低噪声放大器为例,详细阐述了如何利用Agilent 公司的ADS 软件进行分析和优化设计该

2009-11-01 15:07:13 71

71 S波段低噪声放大器的分析与设计:介绍了S 波段低噪声放大器(LNA ) 的设计原理和流程。对影响电路稳定性和噪声性能的、易被忽视的因素进行了详细分析。文中重点分析实际电路可能

2009-11-01 15:16:46 20

20 低噪声放大器设计指南:低噪声放大器在通讯系统中的作用随着通讯工业的飞速发展,人们对各种无线通讯工具的要求也越来越高,功率辐射小、作用距离远、覆盖范围大已成为各

2009-11-13 23:04:53 535

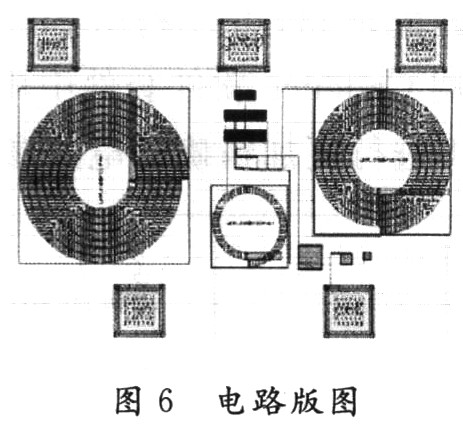

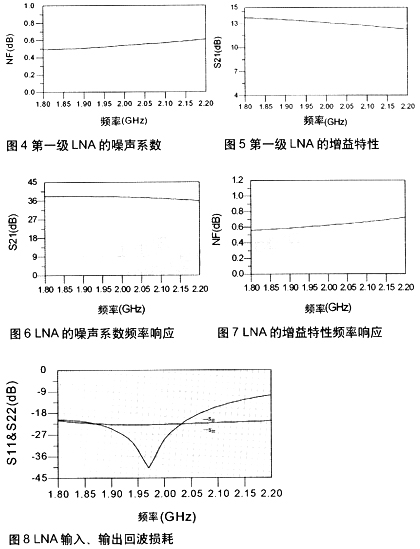

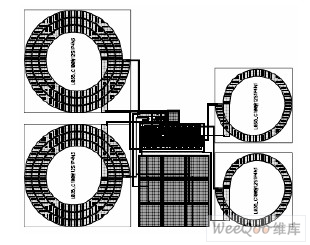

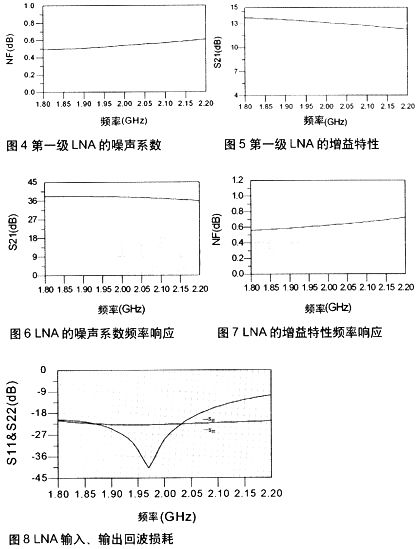

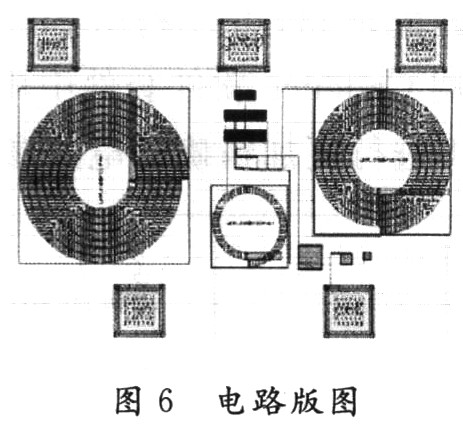

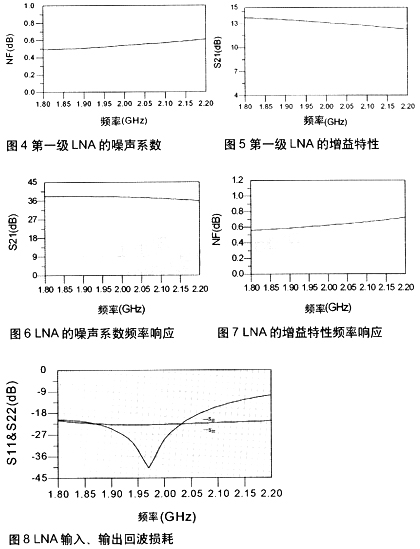

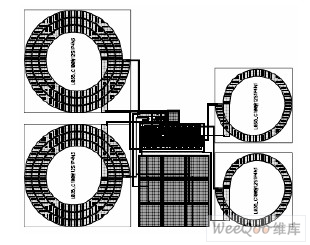

535 论述了在射频电路仿真软件ADS中实现低噪声放大器的整个设计过程,包括低噪声放大器的晶体管的选取、输入输出匹配网络设计以及实现形式等。结合版图与系统结构框图,论述该

2010-07-21 15:18:00 43

43 摘要:介绍一种用于航天GPS接收机的无源微天线的低噪声放大器设计。内容涉及选择低噪声放大器的输入匹配网络及优化匹配参数;并通过实际测试验证了它在天

2006-03-11 13:32:04 763

763

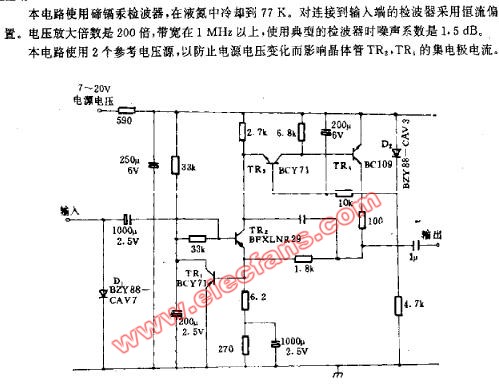

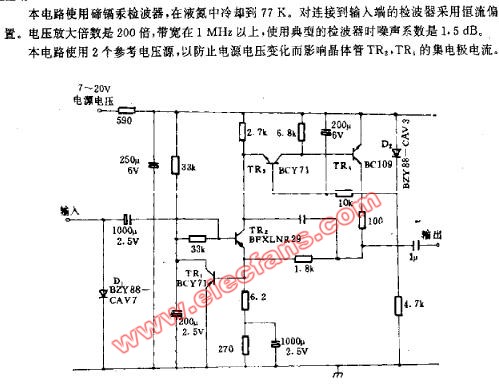

用低噪声放大器的红外检波电路图

2008-12-24 21:56:58 2561

2561

L波段低噪声放大器的设计

低噪声放大器(LNA)是雷达、通信、电子对抗、遥测遥控等电子系统中关键的微波部件,有广泛的应用价值。由于微波系统的噪声系数基本

2009-04-22 15:51:47 1102

1102

利用Cadence设计COMS低噪声放大器

结合一个2.4 GHz CMOS低噪声放大器(LNA)电路,介绍如何利用Cadence软件系列中的IC 5.1.41完成CMOS低噪声放大

2009-07-06 18:23:09 2737

2737

射频低噪声放大器的ADS设计

本文首先简要介绍了低噪声放大器设计的理论基础,并以2.1-2.4Ghz 低噪声放大器为例,详细阐述了如何

2009-10-20 20:45:05 5814

5814

L波段低噪声放大器的设计

引言

低噪声放大器(LNA)是雷达、通信、电子对抗、遥测遥控等电子系统中关键的微波部件,有广泛的应用价值。由于微波系统的噪

2010-02-04 10:43:15 1138

1138

低噪声放大器,低噪声放大器是什么意思

噪声系数很低的放大器。

2010-03-05 10:10:44 3468

3468 3GHz CMOS低噪声放大器优化设计

摘 要: 基于0.18 μm CMOS工艺,采用共源共栅源极负反馈结构,设计了一种3 GHz低噪声放大器电路。从阻抗匹配及噪声优化的角度分析了

2010-04-13 12:57:29 1485

1485

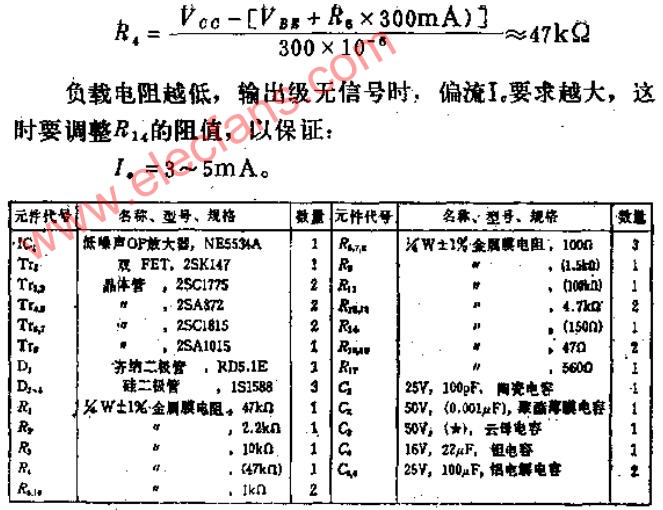

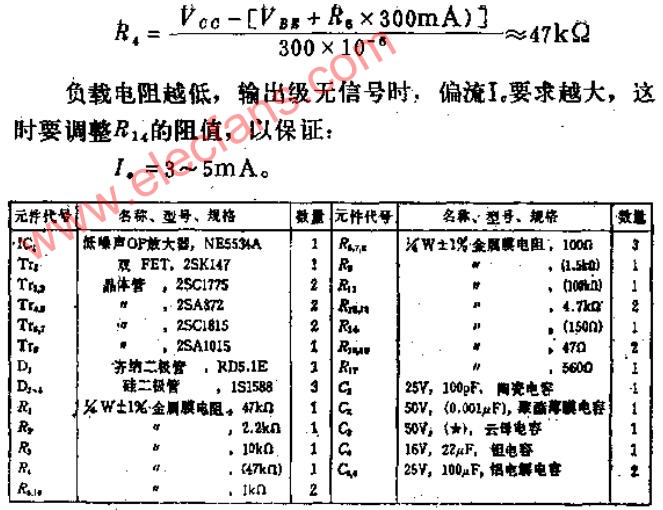

用于高阻抗电路的低失真、低噪声放大器

电路的功能

近年来,噪声及失真特性得到改进的低噪声放大器品种繁多,已无须用分立元件制作了。此外,

2010-04-26 18:27:48 1827

1827

共基差分低噪声放大器

2011-01-10 11:15:41 88

88 本文简要的介绍了低噪声放大器的原理,并用Agilent 公司的ADS 软件设计、仿真了一个Ku 波段的低噪声放大器。

2011-10-13 17:39:31 67

67 低噪声放大器(LNA)是无线系统前端中重要器件,其性能决定了整个接收机的信噪比及整机性能。本文在介绍了低噪声放大器的工作原理之基础上,综述了CMOs基毫米波低噪声放大器的最新

2011-12-16 14:29:17 27

27 宽带低噪声放大器系统的研究与探测,及噪声的提取

2015-12-10 15:24:18 1

1 低噪声放大器(续)池保勇_清华大学微电子学研究所设计室

2016-06-27 16:22:31 0

0 低噪声放大器_池保勇_清华大学微电子学研究所设计室

2016-06-27 16:22:31 0

0 UHF_SHF单片低噪声放大器的设计_唐健

2017-01-07 19:00:39 2

2 一种L频段高线性度低噪声放大器的设计_崔伟

2017-01-07 21:45:57 0

0 用于相控阵雷达的高线性度低噪声放大器_张小波

2017-01-08 10:18:57 1

1 本文对S波段宽带低噪声放大器进行了设计与实现。文中首先阐述低噪声放大器

的相关理论,对二端口网络的表述、传输线、匹配网络等微波电路设计的一些基本理

论进行了介绍。然后给出宽带放大器的主要技术指标

2022-07-08 16:42:53 20

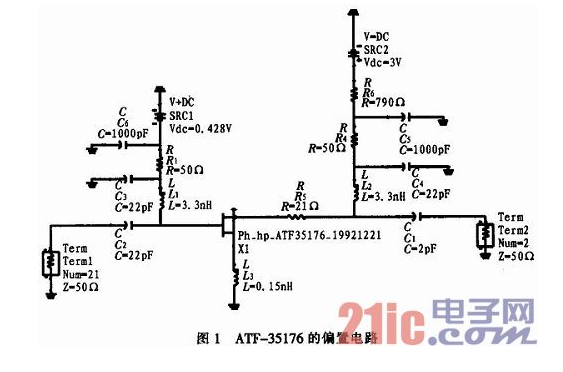

20 工程师们一般都把RF低噪声放大器设计视为畏途。要在稳定高增益情况下获得低噪声系数可能极具挑战性,甚至使人畏惧。不过,采用最新的GaAs(砷化镓)异质结FET,可以设计出有高稳定增益和低于1dB噪声系数的放大器。本设计就讲述了一个有0.77dB噪声系数的低噪声放大器。

2017-11-23 17:17:34 2958

2958

在无线通信终端中,低噪声放大器是射频接收系统中的第一级有源电路,主要功能是放大天线从空中接收到的微弱信号,降低噪声干扰,以供系统解调出所需的信息 数据,低噪声放大器的设计对整个接收机来说是至关重要的。低噪声放大器在提供增益的同时,应尽可能地减少噪声,以及完成接收大信号不失真和好的线性度。

2017-12-10 15:19:01 1533

1533

低噪声放大器,噪声系数很低的放大器。一般用作各类无线电接收机的高频或中频前置放大器,以及高灵敏度电子探测设备的放大电路。在放大微弱信号的场合,放大器自身的噪声对信号的干扰可能很严重,因此希望减小这种噪声,以提高输出的信噪比。

2018-02-12 09:44:01 11819

11819

低噪声放大器(LNA)是射频收发机的一个重要组成部分,它能有效提高接收机的接收灵敏度,进而提高收发机的传输距离。因此低噪声放大器的设计是否良好,关系到整个通信系统的通信质量。

2018-02-12 10:42:50 24169

24169

在整个接收系统中,低噪声放大器总是处于前端的位置。整个接收系统的噪声取决于低噪声放大器的噪声。与普通放大器相比,低噪声放大器一方面可以减小系统的杂波干扰,提高系统的灵敏度;另一方面放大系统的信号

2018-12-28 15:55:14 18075

18075

低噪声放大器, 噪声系数很低的放大器。一般用作各类无线电接收机的高频或中频前置放大器,以及高灵敏度电子探测设备的放大电路。在放大微弱信号的场合,放大器自身的噪声对信号的干扰可能很严重,因此希望减小这种噪声,以提高输出的信噪比。

2019-12-20 09:10:26 21420

21420 Qorvo提供了各种具有低噪声性能的工业领先晶体管和放大器。Qorvo低噪声放大器提供各种产品解决方案,包括分立晶体管、集成内部匹配和片内线性化的封装mMIC解决方案,以及用作推挽或平衡放大器配置

2020-11-03 15:34:36 658

658 低噪声放大器简介

2023-01-07 09:28:37 1574

1574 低噪声放大器的设计原理是通过最小化噪声源的贡献,从而实现尽可能低的噪声水平。在放大器的设计中,噪声通常来自于电阻、晶体管和其他元件的热噪声以及输入和输出端口的噪声耦合。为了降低噪声水平,设计低噪声放大器需要采取以下原则:

2023-07-25 09:44:25 968

968 低噪声放大器工作原理详解 低噪声放大器是一种特定类型的放大器,其用途非常广泛。低噪声放大器在射频和微波领域中非常受欢迎,因为它可以有效降低信号的噪声,同时将信号放大到所需的水平。 本文将详细介绍

2023-09-05 17:37:06 2508

2508 低噪声放大器放在哪里?低噪声放大器的作用是什么? 低噪声放大器(low-noise amplifier,LNA)是一种电子产品,通常用于放大弱信号,使其更适合接下来的处理。它通常被用于通信系统、雷达

2023-09-05 17:49:37 958

958

![]()

![]()

电子发烧友App

电子发烧友App

评论