要满足苛刻的频率合成器要求,通常需要做到一定程度的设计灵活性。基本的锁相环(PLL)频率合成器能以低成本、高空间效率、低功耗封装提供合理的频谱纯度和频率捷变,因此它在射频(RF)系统核心位置发挥作用

2022-10-14 10:30:36 2025

2025 ,这是为了支持扫频而引入的。利用第二个累加器来提供一个稳定增加的变量。先进DDS可将该变量增加到基本频率调谐字上,从而获得一个频率稳定变化的信号。也可以将其与POW结合以实现相位扫描。或者将其与ASF结合

2018-08-01 07:29:23

本文由ADI时钟和信号部市场经理JLKeip撰写 在上篇内容 DDS or PLL? 中承诺,我会对DDS/PLL优势对比表的一些微妙之处做一个评述。 这里先谈谈我认为更适合DDS的一些特点。 频率

2019-01-18 13:19:36

本文由ADI时钟和信号部市场经理JLKeip撰写在上篇内容 DDS or PLL? 中承诺,我会对DDS/PLL优势对比表的一些微妙之处做一个评述。 这里先谈谈我认为更适合DDS的一些特点。频率

2018-10-11 11:15:23

合成一个正弦信号,那么了解一点直接数字式频率合成器(Direct Digital Synthesizer,DDS)会有助于您确定最佳解决方案哦~ 多数工程师在求学时接触过锁相环(PLL),但DDS不是

2019-02-13 11:54:20

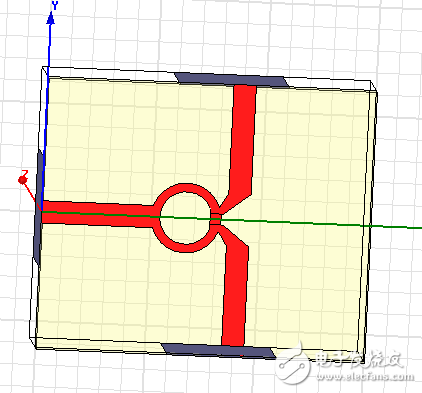

Ka波段E面和H面90°弯接头的设计

2010-09-08 17:41:55

几何尺寸缩小,这一差距也会缩小,但规模经济也会导致其缩小。PLL使用更广泛,生产规模要大得多,有助于改善成本结构。如果是针对大规模应用,并且DDS方案有一些优势,那么在价格上应该有一定的协商空间。宽频

2018-10-31 10:57:30

设备量大,导致体积大、成本高。DDS+PLL合成方式包括DDS激励PLL的方式、DDS内插入PLL做分频器以及DDS与PLL混频的方式。DDS激励PLL做分频器的方式由于DDS最大输出频率不高,需要多次

2019-06-21 06:32:34

资料下载。希望大家喜欢哦! 本讲义涉及以下主题内容五种类型的频率合成什么是时钟? 常用频率是多少?锁相环(PLL)基本模型鉴频鉴相器(PFD) 驱动电荷泵(CP)数字PLL框图 —— 分频器PLL中输入

2018-10-26 09:16:36

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

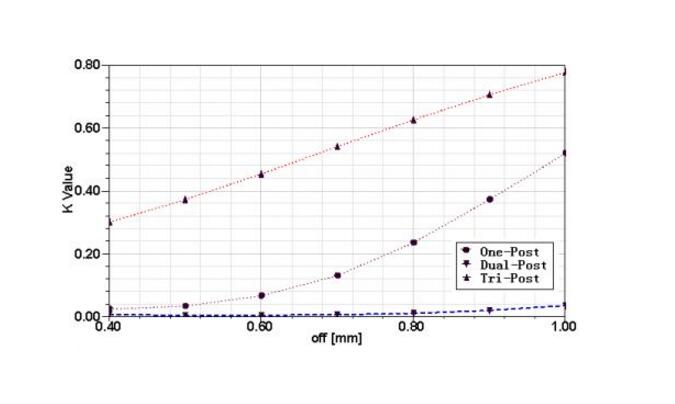

【作者】:潘晓艳;【来源】:《信息与电子工程》2010年01期【摘要】:介绍一种模块化的L波段细步进捷变频频率综合器,采用直接数字频率合成器实现细步进,采用上变频器+倍频器来提高并扩展带宽。讨论其

2010-04-22 11:47:59

TGA4508 Ka波段低噪声放大器重要参数频率范围:30-42GHz增益 :21dB噪声系数 :2.8dB适用于VSAT 和 电子战 项目TGA2595 Ka波段功率放大器重要参数频率范围

2020-05-29 08:55:33

`上海迦美信息通讯技术有限公司PLL/频率综合器15K-30K上海1-3年硕士及以上全职职位诱惑: 年底三薪,员工旅游,定期体检,餐饮补贴 职位描述:岗位职责:1.PLL及相关电路模块设计,如LC

2016-01-07 11:01:43

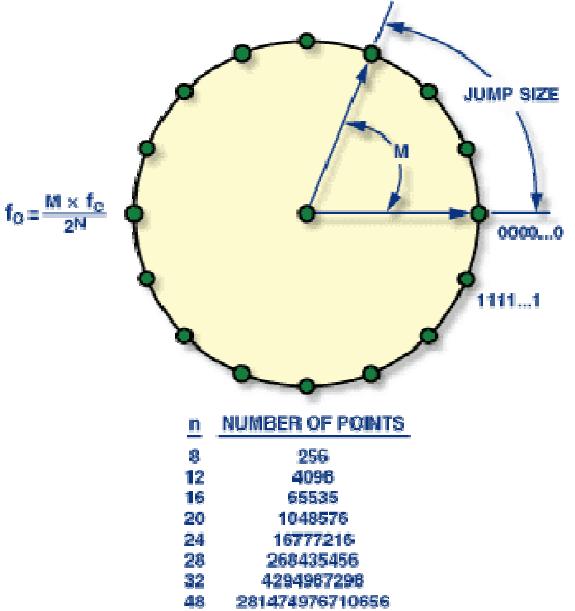

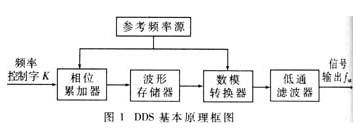

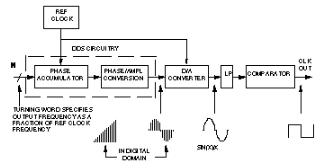

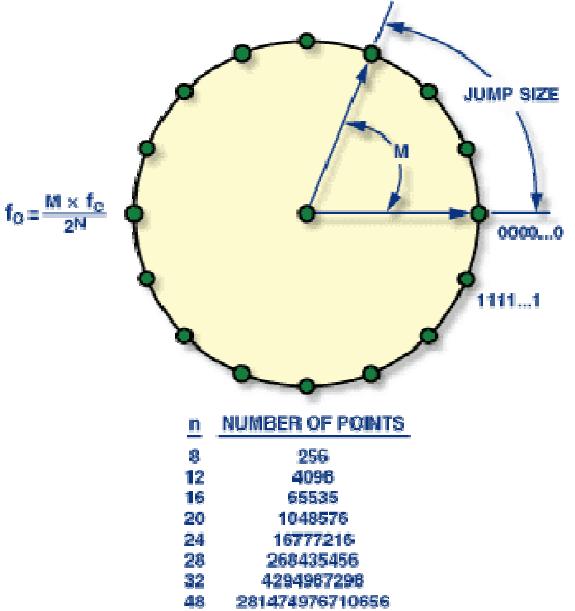

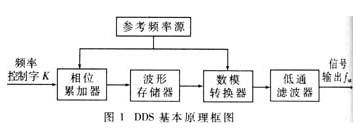

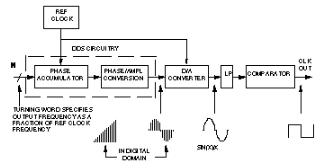

的设计方案。 1 DDS的结构及工作原理 DDS的基本结构由参考时钟、相位累加器、ROM、DAC(数模转换器)和LPF(低通滤波器)组成,见图1。 DDS的工作原理是:在参考时钟fr的控制下,频率

2011-07-16 09:09:54

变化的敏感; A型我电荷泵的PLL频率合成器是在这项工作中提出。闭环系统的稳定是实现使用一个离散时间环路滤波器。 I型系统架构导致开关速度快。离散时间环路滤波器的相位/频率检测器和VCO调谐节点之间的隔离。因此性能可以达到一个良好的刺激。PLL博士论文_全集成频率综合器[hide][/hide]

2011-12-15 11:17:56

请教有经验的射频工程师,采用DDS+PLL的方式设计雷达发射源,要求发射信号为26GHz单频连续波信号以及三角形LFMCW信号,25.5GHz~26.5GHz,调制周期2ms,通过单片机控制波形切换,请推荐DDS和PLL芯片型号,以及晶振的选择,十分感谢

2018-10-09 17:39:06

直接数字频率合成(DDS)在过去十年受到了频率合成器设计工程师极大的欢迎,它被认为是一种具有低相位噪声和优良杂散性能的灵活的频率源,基于DDS的频率合成器在许多应用中能比基于锁相环(PLL)频率

2019-07-08 07:26:17

的重要部件。基于矩形波导的功率分配/合成网络由于本身低损耗、应用频率高的特点成为研究人员的研究重点。在毫米波段,对于二进制功率分配波导单元结构多采用3-dB 波导E-面分支结构,该波导分支结构具有

2019-06-19 06:26:05

GSPS转换器是当下热门,其优势在于既能缩短RF信号链,又能在FPGA中创建更多资源结构以供使用,例如:减少前端的下变频以及后级的数字下变频器 (DDC)。但相当多的应用仍然需要高频率的原始模拟带宽

2019-09-11 11:51:24

与POR或ASF能力的结合。下面是辅助累加器迄今最有意义的用法:1. 最初,这是为了支持扫频而引入的。利用第二个累加器来提供一个稳定增加的变量。先进DDS可将该变量增加到基本频率调谐字上,从而获得一个频率

2018-10-31 10:53:03

本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

2021-04-20 06:42:27

信号发生器是一种常用的信号源,广泛应用于通信、测量、科研等现代电子技术领域。信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成技术(DDS

2019-09-29 08:08:12

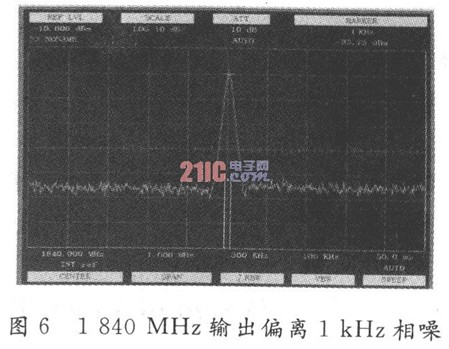

信号能力,具有宽带、小步进、低杂散的频率源也就变得越来越重要。 直接数字式频率合成源(DDS)驱动锁相环(PLL)方式,近端环路内杂散按20lgN恶化(N为锁相环倍频次数)[1],其电路结构简单,易于

2020-12-03 16:06:44

直接数字频率合成(DDS)具有快速频率切换和调制能力,应用广泛。但是,当低功耗和低成本是主要考虑因素时,DDS常常不得不退居其次,让位于模拟锁相环(PLL)。AD9913改变了这一局面,不仅

2011-09-06 14:47:52

测试木材的介电常数。从低频段到高频段(ka波段),具体波段可以根据实际讨论,低一些也行。

2019-07-01 19:21:58

AD9850 是AD I 公司采用先进的DDS 技术, 1996年推出的高集成度DDS 频率合成器, 它内部包括可编程DDS 系统、高性能DAC 及高速比较器, 能实现全数字编程控制的频率合成器和时钟

2008-04-10 13:14:29 83

83 利用反向并联二极管对的二倍频原理,设计了Ka波段二倍频器。用高级设计系统ADS设计软件包的射频设计软件对二倍频器的电路进行了模型设计和仿真分析,并对设计出的二倍频器

2008-11-17 23:24:09 50

50 给出了Ka 波段相对论绕射辐射振荡器(RDG)的辐射功率测量方法和实验结果。器件采用带反射器两段式过模慢波结构,由于器件的过模结构特点,实验选择用空间积分方法测试辐射功

2009-02-28 17:02:18 19

19 杂散抑制差和输出频率低是DDS的两大缺点,并且随着输出带宽的增加杂散性能更加恶化。传统的解决方法是采用更好的算法和改进DDS芯片本身的结构。该文在分析了DDS杂散性能和

2009-03-11 22:09:22 19

19 DDS直接频率合成,由Quicklogicw公司提供

2009-05-14 10:51:37 26

26 DDS(直接数字频率合成)技术是一门在频率合成领域的新兴技术,具有响应时间短,精度高等优点。而PLL(Phase Locked Loop)锁相环技术虽然工作速度慢,但稳定可靠。VXI 总线具有

2009-06-01 16:12:24 17

17 DDS的结构和在系统设计中的优势以及D A转换器在DDS中的应用:

2009-06-10 11:11:09 34

34 ALA0025 - Ka 波段 25 KHz 稳定性 PLL LNB ALA0025 规格转换增益 55 dB ty p.(50dB m in.

2022-11-14 09:21:10

ALB0025 - Ka 波段 25 KHz 稳定性 PLL LNB ALB0025 规格转换增益 55 dB ty p.(50dB m in.

2022-11-14 09:33:33

针对PLL体系结构的频率合成及规划:In many applications, it is desired to generate a set of frequencies from

2009-08-17 09:52:31 8

8 本文讨论了DDS+PLL 结构频率合成器硬件电路设计中需要考虑的几方面问题并给出了设计原则,依此原则我们设计了一套短波波段频率合成器,实验结果证实了其可行性。

2009-09-07 16:07:29 34

34 直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率

2009-09-11 15:55:32 13

13 Ka波段低噪声放大器的研镧:本文介绍了~种毫米波低噪声放大器的设计技术,应用CAD技术设计了波导到微带的过渡,结合其它电路设计和组装工艺,研制出了工作带宽为3GHz的Ka波

2009-11-01 14:56:59 16

16 针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

36 直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率合

2010-08-04 15:57:03 0

0 DDS,什么是DDS,DDS的结构

DDS概述

直接数字式频率综合器DDS(Direct Digital Synthesizer),

2009-09-03 08:42:40 4227

4227

U波段常用电台频率表

频道号

发信频率

收信频率

2009-10-20 15:21:46 7228

7228 DDS是什么意思,DDS结构,DDS原理是什么

什么叫DDS

直接数字式频率合成器DDS(Direct Digital Synthesizer),实际

2010-03-08 16:56:38 45260

45260 DDS+PLL高性能频率合成器的设计方案

频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率

2010-04-17 15:22:13 3209

3209

休斯和Avanti扩展Ka波段卫星服务范围一宗为期多年的4200万美元交易,由休斯公司向Avanti提供Ka波段技术,以扩展HYLAS 1 & 2卫星在欧洲/中东和非洲的宽带服务范围

&nb

2010-04-29 16:45:17 491

491 对宽带多媒体卫星通信系统的需求进行分析的基础上,对基于星载ATM交换的KA波段宽带多媒体卫星通信系统的技术特点 系统组成、协议栈结构及工作模式进行简要介绍

2011-03-22 15:50:39 164

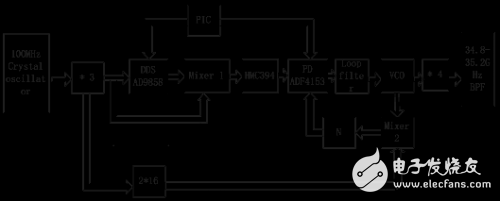

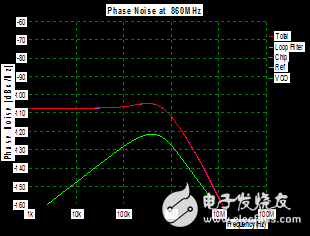

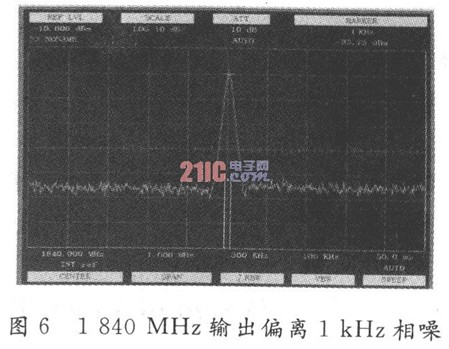

164 针对高性能DDS芯片AD9858设计宽带 频率合成器 , 分析DDS的工作原理,给出宽带频率合成器的原理框图和实现过程,并对软件控制流程进行了详细说明,结合理论对系统的相位噪声和杂散

2011-06-22 10:49:03 50

50 本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

2011-07-18 09:38:02 3423

3423

结合直接数字频率合成(DDS)和锁相环(PLL)技术完成了X波段低相噪本振跳频源的设计。文章通过软件仿真重点分析了本振跳频源的低相噪设计方法,同时给出了主要的硬件选择和详细

2012-03-20 15:52:28 18

18 在非相参雷达测试系统中,频率合成技术是其中的关键技术.针对雷达测试系统的要求,介绍了一种用DDS激励PLL的X波段频率合成器的设计方案。文中给出了主要的硬件选择及具体电路设

2012-06-28 17:33:39 39

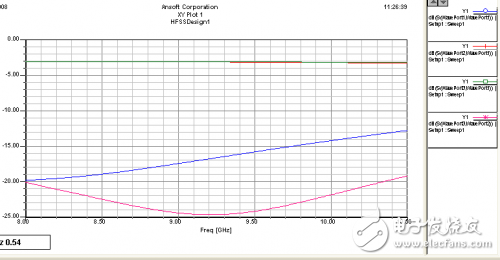

39 介绍了一种横向Ka波段宽带波导-微带探针过渡的设计,基于有限元场分析软件Ansoft HFSS对该类过渡的设计方法进行了研究。最后给出了Ka波段内的优化数据。仿真结果表明,该宽带波导

2012-08-29 17:11:09 54

54 介绍了一种Ka波段的四路功率分配/合成网络。该网络采用H面波导裂缝电桥结构,只需要一个耦合单元,结构简单、易于加工。这种合成网络将使用在基于MMIC单片TGA1141的四路功率合成器

2012-11-09 16:21:05 31

31 为了满足宽频段、细步进频率综合器的工程需求,对基于多环锁相的频率合成器进行了分析和研究。在对比传统单环锁相技术基础上,介绍了采用DDS+PLL多环技术实现宽带细步进频综,输

2013-04-27 16:26:51 48

48 为了研制一种锁定时间短、相位噪声低、杂散抑制度高的频率合成技术,采用了直接数字式频率合成器(DDS)驱动锁相环(PLL)的结构。该频率合成器综合了DDS频率转换速度快、频率分

2013-07-26 11:55:05 42

42 一种Ka波段基片集成波导功率合成器的设计.

2016-01-04 15:21:55 0

0 DDS-PLL组合跳频频率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 详细介绍了直接数字频率合成器(DDS)的工作原理、基本结构。在参考DDS 相关文献的基础上,提出了符合结构的DDS 设计方案,利用DDS 技术设计了一种高频率精度的多波形信号发生器,此设计基于可编程逻辑器件FPGA,采用Max+PlusⅡ开发平台,由Verilog_HDL 编程实现。

2016-11-22 14:35:13 0

0 学习单片机电路图的很好的资料——DDS-PLL组合跳频频率合成器

2016-11-03 15:15:39 0

0 一种基于DDS的S波段频率源设计,下来看看

2017-01-13 13:46:17 27

27 K波段低相位噪声频率综合器的设计与实现_郑永华

2017-01-08 10:18:57 3

3 将DDS和PLL技术结合起来,采用DDS直接激励PLL的混合频率合成方案完成了X波段微波变频信号源的设计,一定程度上解决了频率分辨率、频率转换速度和相位噪声的问题,并完成了实机研制、系统联调试

2017-10-27 11:18:52 4

4 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2017-10-27 17:54:21 8

8 频率源的一个重要方式,但是它体积大、设备复杂、杂散也较大。数字锁相集成器件出现以来,锁相式频率合成器得到迅速发展,但是当需要窄频率步进时,环路带宽需要降低,致使锁定时间变长,不能满足快速跳频的要求。DDS的出现恰好可

2017-11-14 15:46:48 2

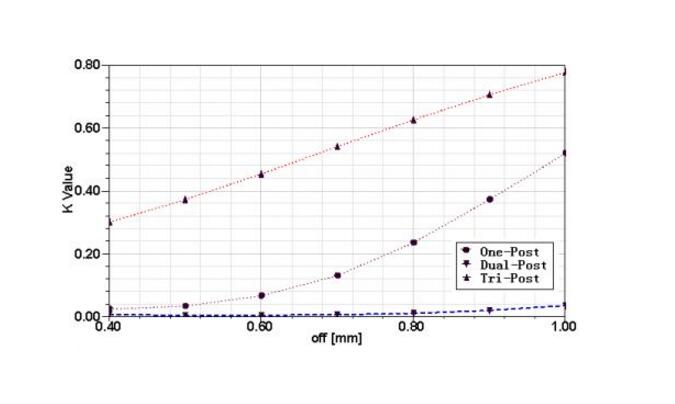

2 1 引言 Ka波段具有许多让人注目的特点,如高数据传输率和良好的保密性,这使得它吸引了大量工程技术人员的注意。因此大量Ka波段商用和军用的电路得以实现。但是,对低成本,结构紧凑和高性能的追求必然

2017-11-14 16:08:17 0

0 的新型通信卫星的研发具有重要意义。由于Ka波段接收机具有频率高、信息容量大、抗干扰性强等特点,目前我国的新型通信卫星多采用该项技术。因此,研制高性能的Ka波段接收组件迫在眉睫。 2 系统组成及工作原理 该组件主要由射频通道、混频

2017-11-17 15:42:24 5

5 (PLL)技术的间接频率合成器目前应用最为广泛。直接模拟频率合成器(DAS)采用倍频器、分频器、混频器及微波开关来实现频率合成,具有最优的近端相位噪声和高速捷变频特性,但结构复杂、成本昂贵的特点限制其只能应用于雷达等高端

2017-11-18 09:55:09 4

4 日晚,卫星中继终端用国产Ka波段行波管作为主份首次开机成功,工作正常。 实践十六号卫星任务是实现空间探测和技术试验。该卫星装备的X和Ka波段两个国产行波管放大器均由中国科学院电子学研究所自主研制。实践十六号卫星国产X波段、Ka波段行波管开机成

2017-12-06 09:48:14 688

688 Ka波段是电磁频谱的微波波段的一部分,Ka波段的频率范围为26.5-40GHz。Ka代表着K的正上方(K-above),换句话说,该波段直接高于K波段。Ka波段也被称作30/20 GHz波段,通常

2018-02-20 18:20:00 2661

2661

Ka波段具有许多让人注目的特点,如高数据传输率和良好的保密性,这使得它吸引了大量工程技术人员的注意。因此大量Ka波段商用和军用的电路得以实现。

2018-05-02 10:40:00 2179

2179

直接数字式频率综合器 DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。DDS

2018-06-19 08:00:00 25

25 TrimQUT TGA45—SM是Ka波段封装的驱动放大器。TGA45 12SM工作在28~32 GHz,是使用TrimQuin的功率PHEMT生产工艺设计的。

2018-08-28 11:26:00 2

2 本文档的主要内容详细介绍的是TGA4507 Ka波段低噪声放大器的详细数据手册免费下载

2018-08-22 11:26:00 4

4 TrimQuT TGA4541-SM是一个可变增益放大器,用作线性Ka波段应用中的驱动放大器。TGA45 41-SM从28到31 GHz工作,并使用TrimQuin的PHEMT生产工艺设计。

2018-08-10 11:28:00 2

2 本文档的主要内容详细介绍的是TGA4508 Ka波段低噪声放大器的详细数据手册免费下载。

2018-08-02 11:29:00 9

9 本文档的主要内容详细介绍的是TGA4507 Ka波段低噪声放大器详细数据免费下载。

2018-08-02 11:29:00 8

8 介绍了直接数字频率合成器(Direct Digital fiequency Synthesizer,DDS)的基本结构和工作原理,并在此基础上着重论述了利用舭软件建立DDS的理想和杂散仿真模型的方法。通过建立仿真模型,可以更方便有效地对DDS杂散分布特点进行分析。

2019-11-06 17:48:21 15

15 PLL 频率合成器基本构建模块 PLL 频率合成器可以从多个基本构建模块的角度来考察。我们在前面已经提到过这个问题,下面将更加详细地进行探讨:鉴频鉴相器(PFD) 参考计数器(R) 反馈计数器

2020-12-03 01:47:00 21

21 KU波段是指比IEEE 521-2002标准下的K波段频率低的波段,KU的频段通常下行从10.7到12.75GHz,上行从12.75到18.1GHz。

2020-11-27 16:14:00 30124

30124 ADMV4530:带集成小数N PLL和压控振荡器的双模Ka波段上变频器数据表

2021-04-24 16:10:26 10

10 HMC7054:Ka波段HPA数据表

2021-04-27 12:03:55 8

8 近二十年来,随着数字集成电路和微电子技术的发展,出现了一种新的频率合成技术--直接数字合成 Direct Digital Synthesize 技术。DDS的出现导致了频率合成领域的第二次

2021-05-20 11:10:11 5449

5449

PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 直接数字频率合成技术(DDS+PLL)资料下载。

2021-06-07 14:41:54 38

38 在典型的永久性卫星通信设施中,室外设备和室内设备在功能上是分开的。室外设备由Ka波段天线、低噪声块(LNB)和下变频级组成,其将Ka波段信号下变频为L波段信号,然后发送到室内单元。

2022-08-22 11:56:09 999

999 Ka波段上运行着数据速率最高的最先进卫星通信系统。由于Ka波段频率的传输质量在很大程度上取决于天气条件,因此需要仔细规划和选择合适的系统配置。

2022-10-26 16:42:22 748

748 传统Ka波段地面站卫星通信系统依赖于室内到室外配置。室外单元包含天线和块下变频接收机,接收机输出L波段的模拟信号。该信号随后被传送到室内单元,室内单元包含滤波、数字化和处理系统。Ka波段的干扰信号

2023-01-04 10:44:30 765

765 新的集成完整DDS产品为敏捷频率合成应用提供了一种有吸引力的模拟PLL替代方案。长期以来,直接数字频率合成 (DDS) 一直被认为是生成高精度、频率捷变(宽范围内可快速变化的频率)、低失真输出波形的卓越技术。

2023-01-30 09:51:57 1148

1148

与基于PLL的传统频率合成器相比,NCO和DDS的显著优势包括:极高的频率分辨率、快速灵敏性,以及可轻松生成完美正交的正弦/余弦波形

2023-02-19 11:18:10 521

521 pll频率合成器工作原理与pll频率合成器的原理图解释 我们要搞清楚pll频率合成器工作原理与pll频率合成器的原理图就要先搞清楚pll和频率合成器的概念。 频率合成器:将一个高稳定度和高精度的标准

2023-02-24 18:19:52 8266

8266

Ka波段上运行着数据速率最高的最先进卫星通信系统。Ka波段站点分集配置依赖DWDM射频-光纤传输系统和冗余切换单元,虹科提供最合适的解决方案,确保最大的系统可靠性和可用性。

2022-11-02 15:43:19 587

587

频率的产生有两种方法:DDS和PLL,但是为什么射频工程师一般用PLL多,很少用DDS呢?

2023-06-28 09:38:48 1823

1823

影响PLL的应用领域。PLL锁定时间可以根据PLL的频率精度来计算,下面是一个详细的讨论。 PLL - 综述 PLL是一种电路,它在输入信号和输出信号之间建立了一个相位锁定环,以使输出频率与输入频率之间存在固定的关系。举例来说,如果PLL的输入频率为f_in,而输出频

2023-09-02 15:12:23 811

811 电子发烧友网站提供《一种横向Ka波段宽带波导-微带探针过渡的设计.pdf》资料免费下载

2023-10-23 14:11:43 2

2 电子发烧友网站提供《一种用DDS激励PLL的X波段频率合成器的设计方案.pdf》资料免费下载

2023-10-24 09:10:26 4

4 电子发烧友网站提供《Ka波段基片集成波导带通滤波器的设计.pdf》资料免费下载

2023-10-25 11:18:32 0

0

电子发烧友App

电子发烧友App

评论