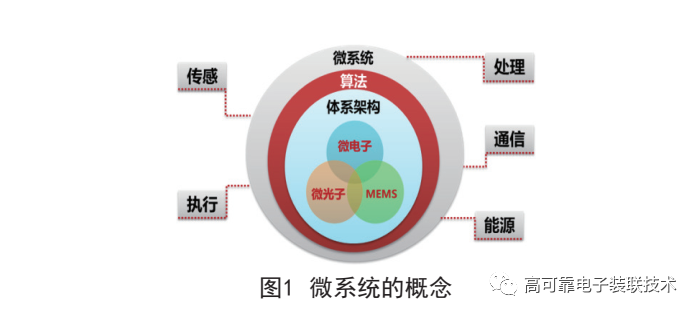

摘 要:军事电子装备和民用通信系统复杂度日益提升, 射频(RADIO FREQUENCy,RF) 集成技术正从传统的混合集成技术或多芯片组件技术向芯片化的系统级封装技术(SySTEM IN PACKAGING,SIP) 快速发展。对射频系统级封装(RF⁃SIP) 中的高性能互连技术需求进行了分析, 依据先进封装互连技术的发展趋势, 总结了芯片倒装集成、 芯片埋置与扇出以及三维堆叠等技术在面向 RF⁃SIP 应用的最新研究进展, 最后提出了射频系统级封装互连技术的主要挑战和发展方向。

0 引言

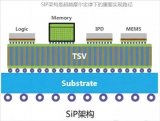

现代军事电子装备的发展对射频系统提出了微型化、多功能、可重构的需求[1] ,射频系统功能复杂度日益提升。有源相控阵(ACTIVE ELECTRONICALLy SCANNED ARRAy,AESA) 技术要求射频系统实现高性能、可扩展、 低成本以及低剖面等特性,当前射频系统集成架构从多芯片组件(MULTI⁃CHIP MODULE,MCM) 向系统级封装(SySTEM IN PACKAGING, SIP) 方向发展[2⁃3]。在SIP的集成架构下,通过异构集成技术将多个不同功能的有源、 无源器件高密度地集成在单一封装内, 形成具有系统或子系统功能的单元。射频系统级封装(RF⁃SIP) 通常采用 BGA、LGA 等标准的器件封装形式, 以便进一步地通过表面贴装技术(SURFACEMOUNTED TECHNOLOGy, SMT) 在系统母板上集成, 形成更为复杂和完整的电子系统[4] 。

相比 MCM 集成, 采用 RF⁃SIP 集成架构的射频系统主要优势如下:

1)在后摩尔时代的技术趋势下, 射频系统可持续吸收异构集成(HETEROGENEOUS INTEGRATION) / 系统级封装的最新技术, 实现更复杂、 更高性能的系统集成;

2)RF⁃SIP 采用标准的封装形式, 产品结构、 工艺方法具有较强的规范性和通用性, 因此新产品导入周期短,可快速进入批量生产, 制造成本低;

3)利用高低频复合母板, 通过 SMT 工艺实现RF⁃SIP 与电源、 数字处理及天线等功能单元之间的板级系统集成,消除体积庞大的射频/ 低频电缆, 大幅提升系统集成密度及可靠性。 基于以上显著优势, RF⁃SIP 在国内外得到了广泛的研究与应用。民用移动通信设备的射频前端模块主要采用 SIP 技术实现, 支撑SUB⁃6GHz 到毫米波, 甚至亚太赫兹频段的应用[5⁃6] 。在军事电子装备领域, 面向轻薄化低剖面天线阵面的发展需求,采用 RF⁃SIP 集成技术实现收发组件(TRANS⁃MITTER AND RECEIVER, T / R) “芯片化” 是一个重要的技术趋势[7] ,尤其在阵元间距仅几个毫米的毫米波频段更是如此[8] 。 互连技术是 SIP 的核心使能技术。相对于传统的引线键合技术, 处于研究和应用前沿的先进封装互连技术包括芯片倒装(FLIP CHIP) 、 芯片埋置与扇出(CHIP EMBEDDED AND FAN⁃OUT) 以及三维堆叠(3DSTACKING) 等。射频电路系统通常包含多样化的元器件和零部件,如化合物半导体、 硅基射频芯片、集成 无 源 器 件 (INTEGRATED PASSIVE DEVICES,IPD) 、MEMS 等, 这些器件采用了不同的材料和工艺, 互连和封装要求差异大, 因此 RF⁃SIP 具有非常鲜明的异构集成特征, 并倾向于综合采用多种先进互连技术。

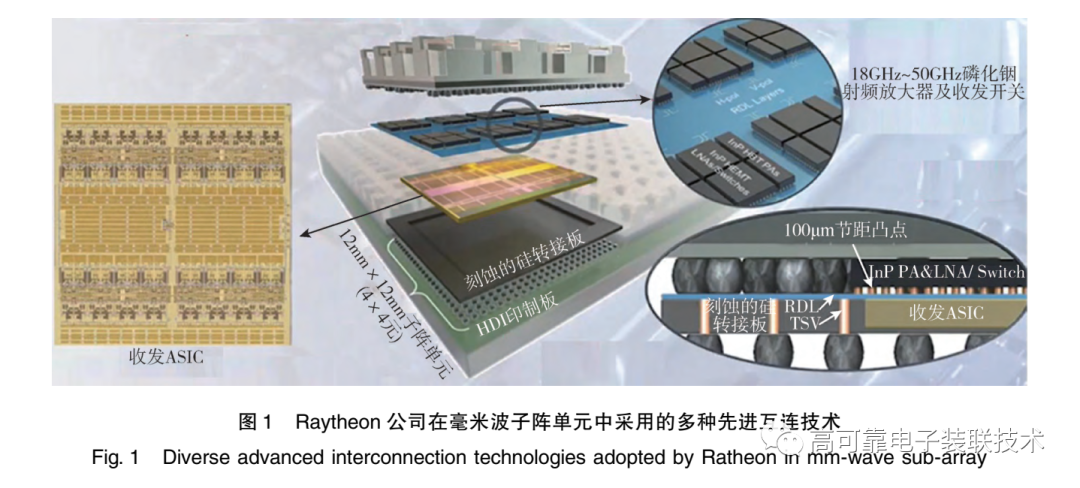

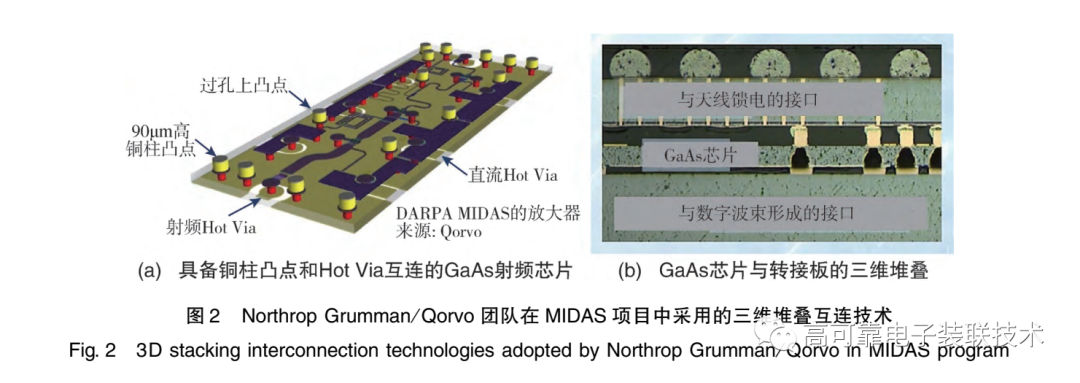

以美国国防高级研究计划局(DARPA) 主导的毫米波数字阵列项目(MIDAS) 为例, RAyTHEON 公司的 4 × 4 子阵单元中, 综合利用了硅基转接板、有机高 密 度 基 板、 再 布 线 层 ( REDISTRIBUTE LAyER,RDL) 、 微凸点倒装等技术, 将硅基 ASIC 多功能芯片、 磷化铟(INP) 低噪放/ 功放以及低剖面宽带阵列天线进行堆叠集成, 展示了一种 18GHz ~ 50GHz 超宽带应用的低剖面三维异构集成架构[9] , 如图1所示。该项目的另一研究团队(NORTHROP GRUMMAN / QOR⁃VO) 采用铜柱凸点、 热过孔(HOT⁃VIA) 等互连结构, 通过多金属与多温度的键合技术将硅转接板、砷化镓 (GAAS) 射频芯片、 锗硅(SIGE) 有源转接板、 CMOS 芯片实现可靠的垂直堆叠互连, 如图 2所示[10] 。

由于分布参数的作用, RF⁃SIP 集成方案的选择对射频信号的传输、 增益、 噪声、 功率以及隔离等系统指标有着直接的影响。先进封装互连技术应用于RF⁃SIP 时将面临射频电路性能相关的挑战, 本文重点综述了 RF⁃SIP 中的芯片倒装、 芯片埋置与扇出、 三维堆叠三类先进封装互连技术的研究进展。

1 芯片倒装技术

传统的射频封装或模块通常采用引线键合技术,但由于基板上的键合焊盘必须布置在芯片的外围, 加之键合引线必须存在一定的高度, 因此互连结构大, 封装内空间利用率低, 集成密度难以进一步提升。芯片倒装技术通过互连材料将芯片有源面与基板焊盘进行组装,相对引线键合,射频芯片倒装的主要技术优势如下:

1)互连距离短、 分布参数小、 一致性好, 尤其在毫米波频段互连性能优异;

2)利用芯片底部面积以面阵的方式与基板在垂直方向互连, 互连结构几乎不占用额外的封装空间, 集成密度高;

3)有效降低封装高度, 有利于封装的三维堆叠集成, 构建复杂功能的 RF⁃SIP。

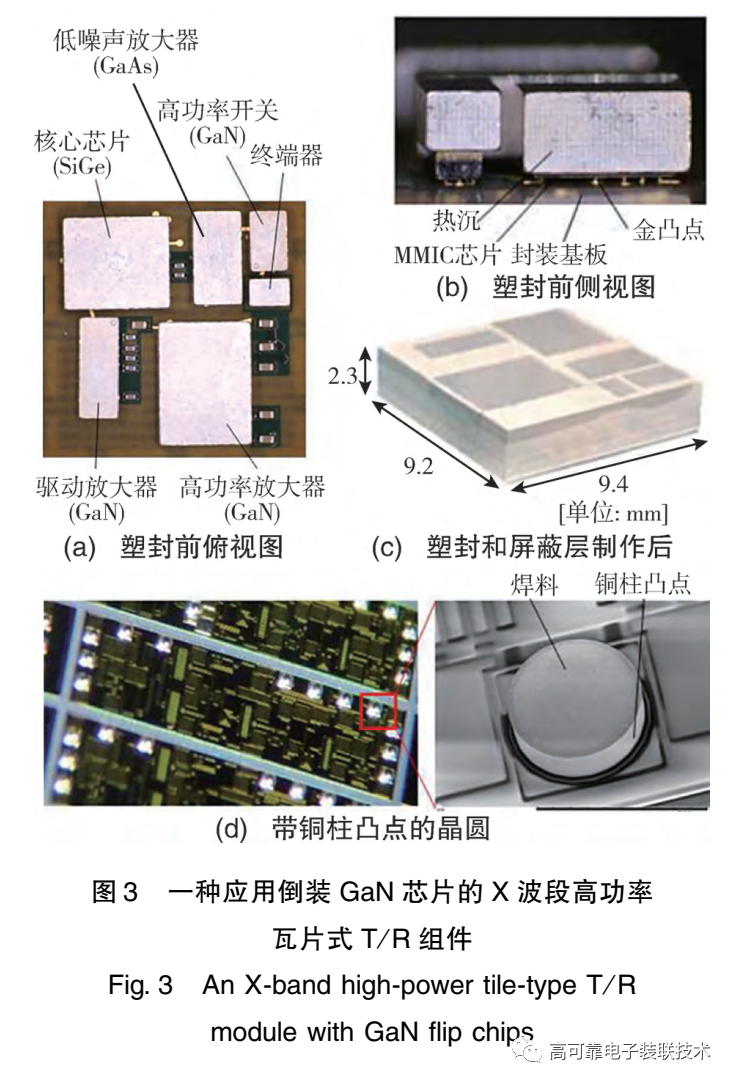

射频芯片倒装技术的研究在 20 世纪90 年代就已开始[11⁃12] , 但由于射频芯片的 I / O 数量少, 单个I / O 的互连成本相对引线键合优势并不明显, 再加上化合物半导体射频芯片因环保和工艺的差异,在利用硅芯片成熟的微凸点产业链能力上存在障碍, 导致了射频芯片倒装技术的应用速度远慢于数字芯片。但随着技术的成熟和产业规模的扩大,化合物半导体FOUNDRy 公司发布了倒装芯片工艺设计套件(PROCESS DESIGN KITS, PDK) , GAAS 和硅基射频芯片的倒装技术已得到大量的应用。在 GAN 芯片方面的技术也即将走向量产应用, 如 QORVO公司获得美国国防部 “ COPPER⁃PILLAR⁃ON⁃GAN” 的项目合同, 目标在 2022 年将 GAN 铜柱倒装芯片技术从小批量的原型工艺推进至高产量、 高可靠的 9 级制造成熟度。 面向低剖面雷达孔径的应用, 日本三菱电机[13] 报道了一种 X 波段高功率 T / R 组件, 其中的SIGE 核心芯片、GAAS 低噪放以及 GAN 功放/ 开关芯片全部采用铜柱凸点倒装集成在有机基板上,然后进行塑封、 屏蔽层制作等工艺, 在尺寸仅9。 2MM × 9。 2MM × 2。 3MM 的 SIP 封装中实现了 20W的发射功率, 如图 3所示。在商业

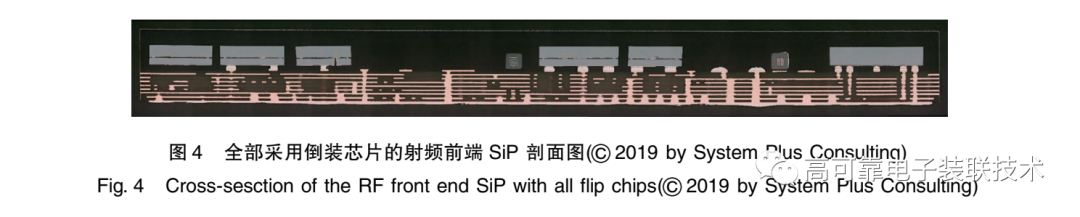

无线通信应用的射频前端 SIP 中, 近年来倒装射频芯片已经成为主流, 如 BROADCOM 公 司 2019 年 量 产 的 射 频 前 端AFEM8092, 封装的 29 颗 MMIC 全部基于倒装技术集成, 封装中芯片面积占比高达 40% , 而且由于消除了芯片粘结、 引线键合等工序, 制造流程简化,整体成本下降, 如图 4 所示。

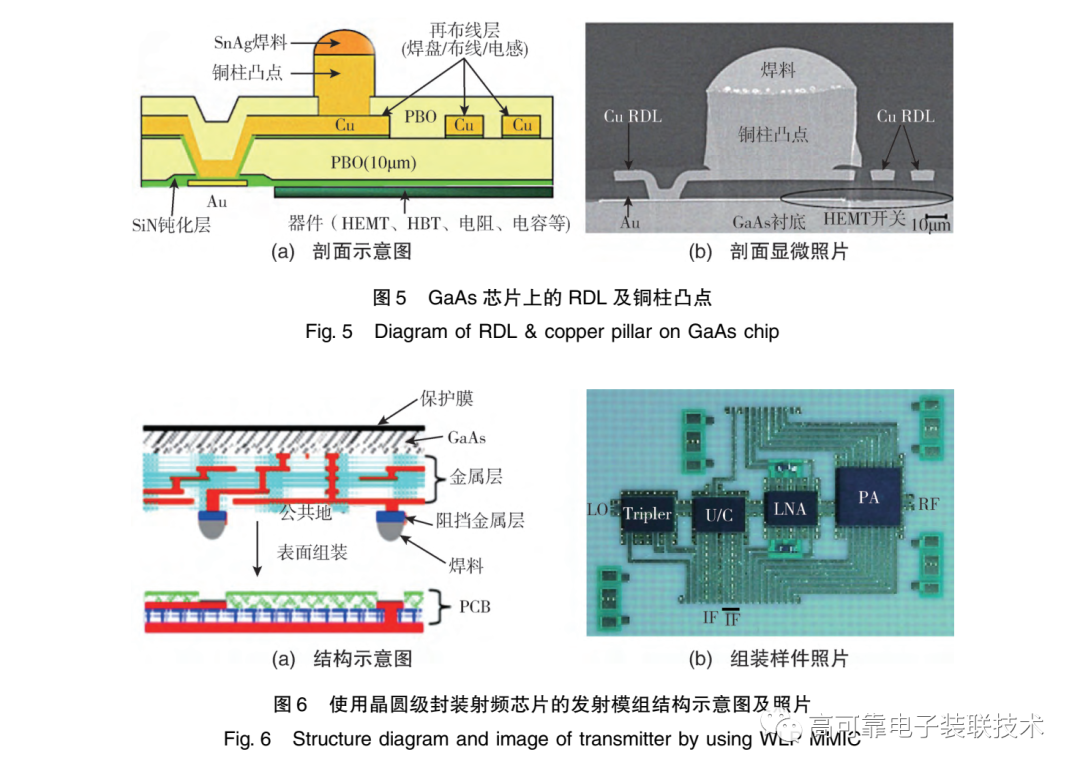

RF⁃SIP 中的芯片倒装技术主要包括芯片⁃封装协同设计、 射频芯片凸点制备、 射频高密度基板、倒装集成装配、可靠性技术等要素。在 RF⁃SIP 中应用芯片倒装技术, 需重点在芯片⁃封装协同设计和射频芯片凸点制备两个维度作特殊的考虑。 与数字电路不同, 射频芯片表面设计有大量的传输线、电感等无源元件, 其传输阻抗、 Q 值等参数易受凸点焊接后的高度、 使用的底部填充和基板材料的影响, 因此射频倒装芯片通常需要与封装进行协同设计[14] 。考虑到装配工艺的精度远低于晶圆工艺, 为降低封装对芯片性能的影响,一种思路是在芯片中采用共面波导传输线(CPW) ,将传输线电场约束在 CPW 的缝隙附近, 并在此基础上进一步优化芯片到基板之间的距离[14⁃15] ;另一种思路是采用晶圆级封装(WAFER LEVEL PACKAGING,WLP) 在芯片表面增加低介电常数的厚介质和再布线层(REDISTRIBUTIONLAyER, RDL) [16] , 甚至设置接地层形成 “反转传输线” 结构[17⁃18] , 屏蔽安装基板对芯片性能的影响, 如图 5 和图6 所示。

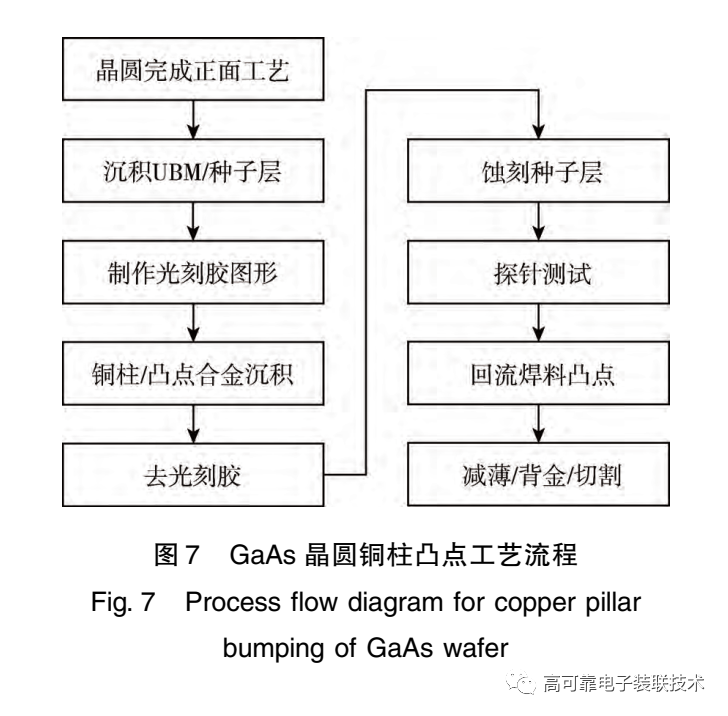

中国电科29所[19] 总结和对比了射频芯片中焊料球凸点、铜柱凸点以及金球凸点这三种主流的凸点制备技术和应用特点。其中,金球凸点与化合物半导体芯片的金属化体系(AU) 兼容,无须制作UBM层,具有较好的灵活性。带焊料帽的铜柱凸点制备工艺显然更为复杂,但可获得更小的互连节距(≤100μM) ,是倒装芯片技术应用的关键技术之一。为解决凸点电镀和晶圆减薄过程中的破片问题,需要重新设计晶圆的后道工艺流程,并优化晶圆减薄所采用的临时键合工艺。图7给出了一种可行的GAAS晶圆铜柱凸点工艺流程[20] 。

2 芯片埋置与扇出技术

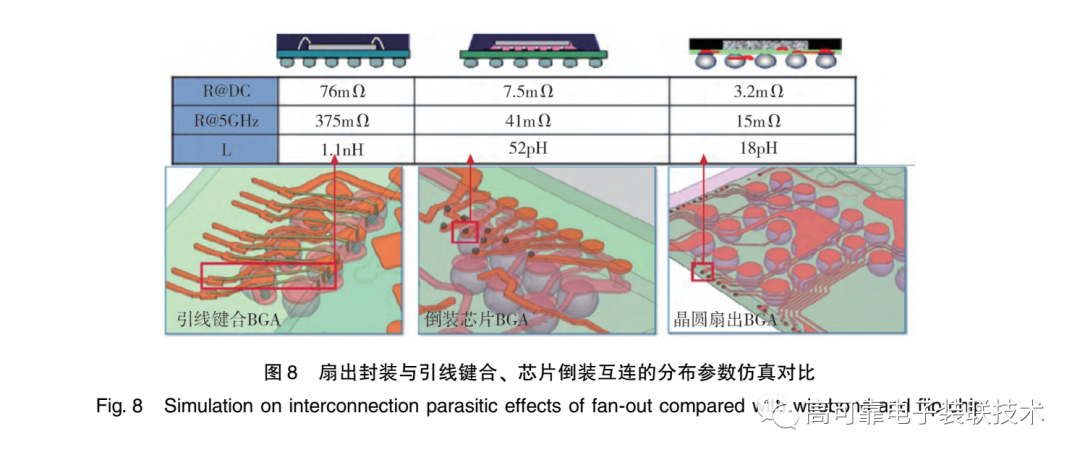

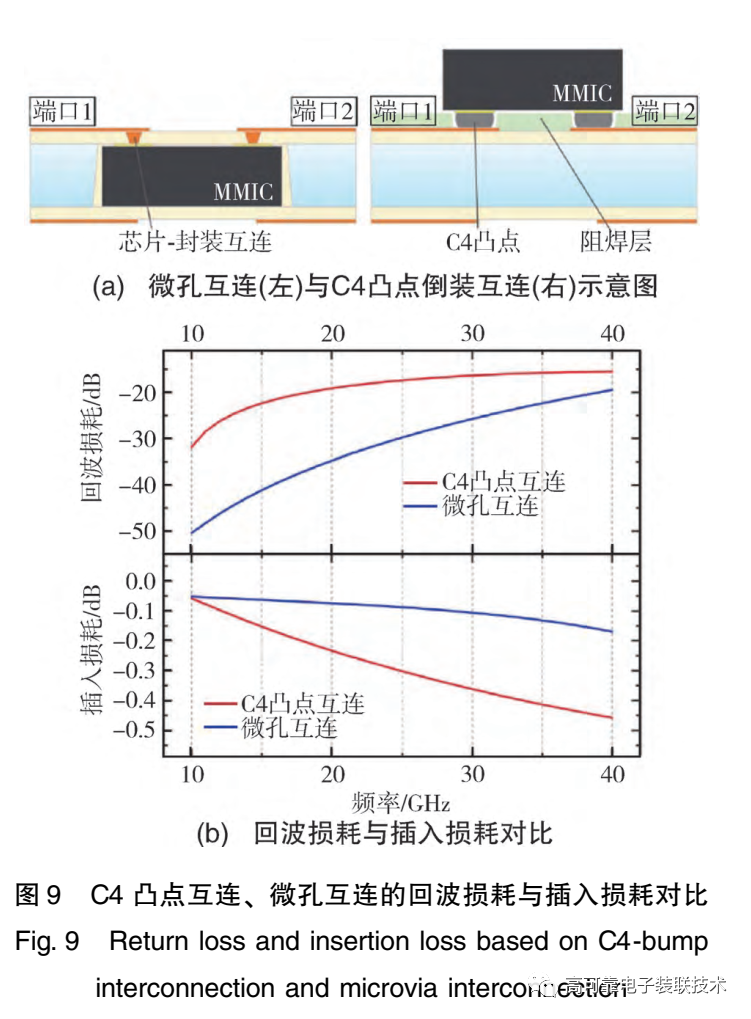

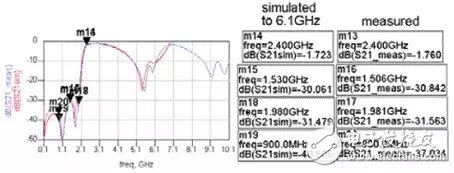

芯片埋置与扇出技术指基于晶圆级或面板级工艺,将器件埋置于塑封料或者基板之中, 然后通过 RDL 扇出器件的 I / O 端口并形成封装[21] 。当埋置多颗不同种类的器件时, 即可形成 SIP[22⁃23] 。扇出技术通过微孔和 RDL 实现芯片⁃封装的互连,由于互连距离短,分布参数(RLC) 小[24] ,毫米波频段互连性能优势明显[25⁃26] 。如图 8 和图 9 所示, 分布参数、 插入损耗相比倒装互连下降至少 50% ,更远优于引线键合。因此, 芯片埋置与扇出互连技术能很好地适应微波/毫米波的应用需求。

自 INFINEON 公司 2009年将基于塑封重构晶圆工艺路线的 EWLB (EMBEDDED WAFER⁃LEVEL BALL GRIDARRAy) 投入量产以来,埋置与扇出工艺作为一种先进封装技术得到了迅速的发展, 并衍生出众多的技术变体。除了已得到较充分研究和成熟应用的“芯片先装/面朝下(CHIP FIRST / FACE DOWN) ”、 “芯片先装/ 面朝上(CHIP FIRST / FACE UP) ”、 “芯片后装/ 面朝下(CHIPLAST / FACE DOWN) ” 这三种基于塑封工艺的技术形态[27] 外, 最近还发展了基于硅、 玻璃、金属以及陶瓷等材料作为埋置材料的扇出系统级封装。华天科技[28] 展示了在硅晶圆上通过 BOSCH 工艺刻蚀高精度盲腔并采用光敏干膜压膜技术埋置了毫米波芯片的封装案例,该方案得益于硅晶圆的高导热性, 因此散热性能优良[29] 。

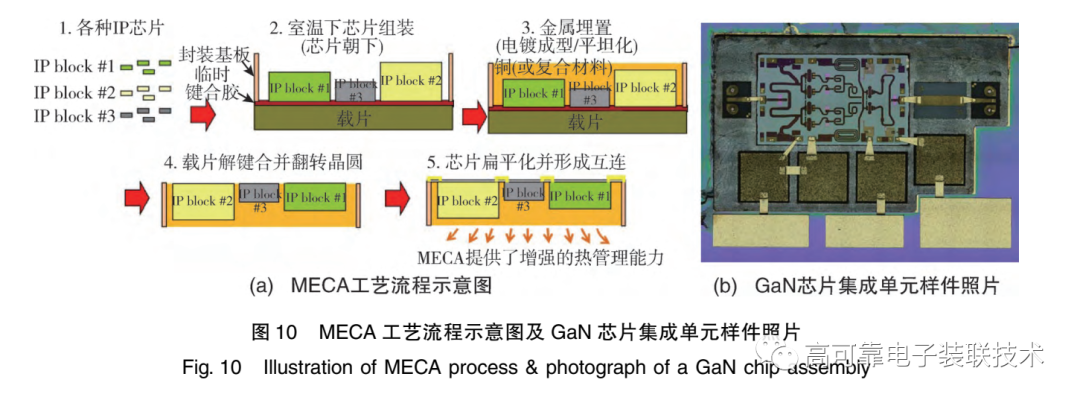

此外,由于芯片与埋置材料为同质材料, 克服了塑封重构晶圆在多芯片封装时翘曲控制的难题[30] 。玻璃以其良好的尺寸稳定性、 优良的高频介电性能以及可制作高密度垂直互连通孔(THROUGHGLASS VIA, TGV)等 独 特 优 势, 也 被 应 用 到 RF⁃SIP 扇 出 封 装中[25, 31⁃32] 。美国休斯实验室(HRL) 提出了一套面向高性能相控阵应用的金属埋置芯片组装工艺(METAL⁃EMBEDDED CHIP ASSEMBLy,MECA ) 。

如 图 10 所示[33⁃34] , 包含 GAN 毫米波功放芯片在内的多颗异质芯片在室温下临时键合到载片上,之后通过电镀铜填充工艺将所有芯片进行埋置,去掉临时载片之后制作空气桥进行芯片互连。MECA 提供了良好的散热环境, 相比 AUSN 共晶到钨铜热沉的工艺, GAN芯片输出功率提升了 42% 。此外, 国内基于多层共烧陶瓷(如 ALN) 制作盲腔,利用苯并环丁烯(BENzO⁃CyCLO⁃BUTENE, BCB) 作为填充介质预埋置芯片, 然后采用CMP 工艺平坦化并露出芯片凸点, 进一步制作 RDL 互连。中国电科 38 所[35] 和14 所[36] 分别对陶瓷盲腔的激光加工技术和埋置应力进行了研究,成功制作了陶瓷基的射频埋置扇出系统级封装电路结构, 在保留了多层陶瓷封装高导热、 高布线层数等原有特点的同时, 利用RDL 技术提升了互连性能并降低了封装剖面厚度。

3 三维堆叠技术

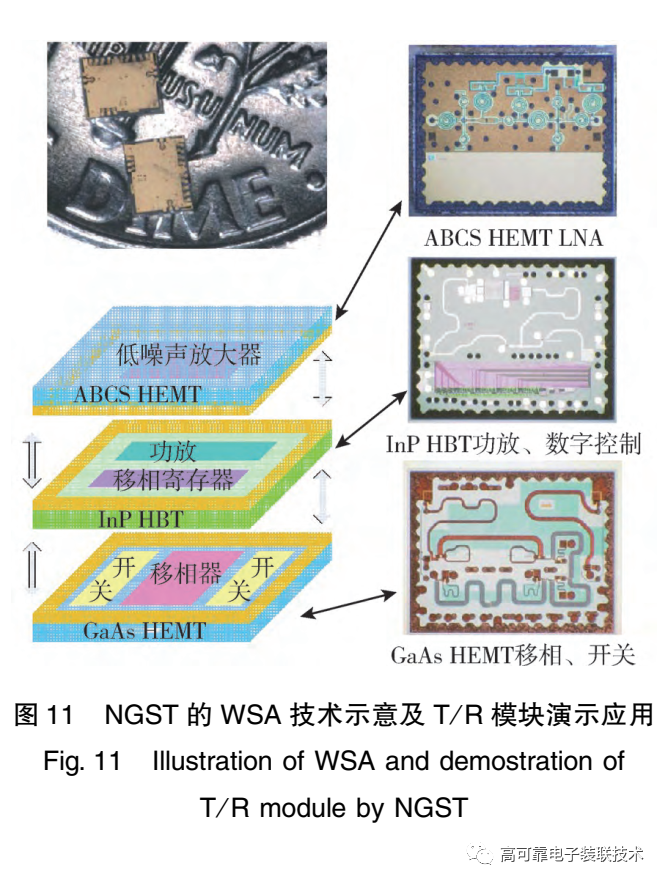

三维堆叠技术在 Z 方向上扩展 SIP的集成维度是异构集成公认的技术方向, 然而射频链路中大量的无源器件采用分布参数设计, 当芯片或封装基板紧密堆叠时, 电磁场的耦合可能导致电路性能严重下降甚至不能正常工作。因此,充分考虑射频性能的约束是RF⁃SIP 应用三维堆叠技术的关键。从堆叠互连的对象不同, 三维堆叠技术可分为芯片堆叠(3D⁃IC) 和封装堆叠(PACKAGING ON PACKA⁃GING, POP) 两大类型。 射频电路的芯片⁃芯片堆叠较早的尝试是诺斯洛普空间技术公司(NGST) 2007 年开发的晶圆级组装(WAFER SCALE ASSEMBLy,WSA) 技术[37] ,通过晶圆级 AU⁃IN 低温键合形成腔内互连(INTRA⁃CAVITy INTER⁃CONNECTIONS, ICIC ) , 实 现 了 仅 2。

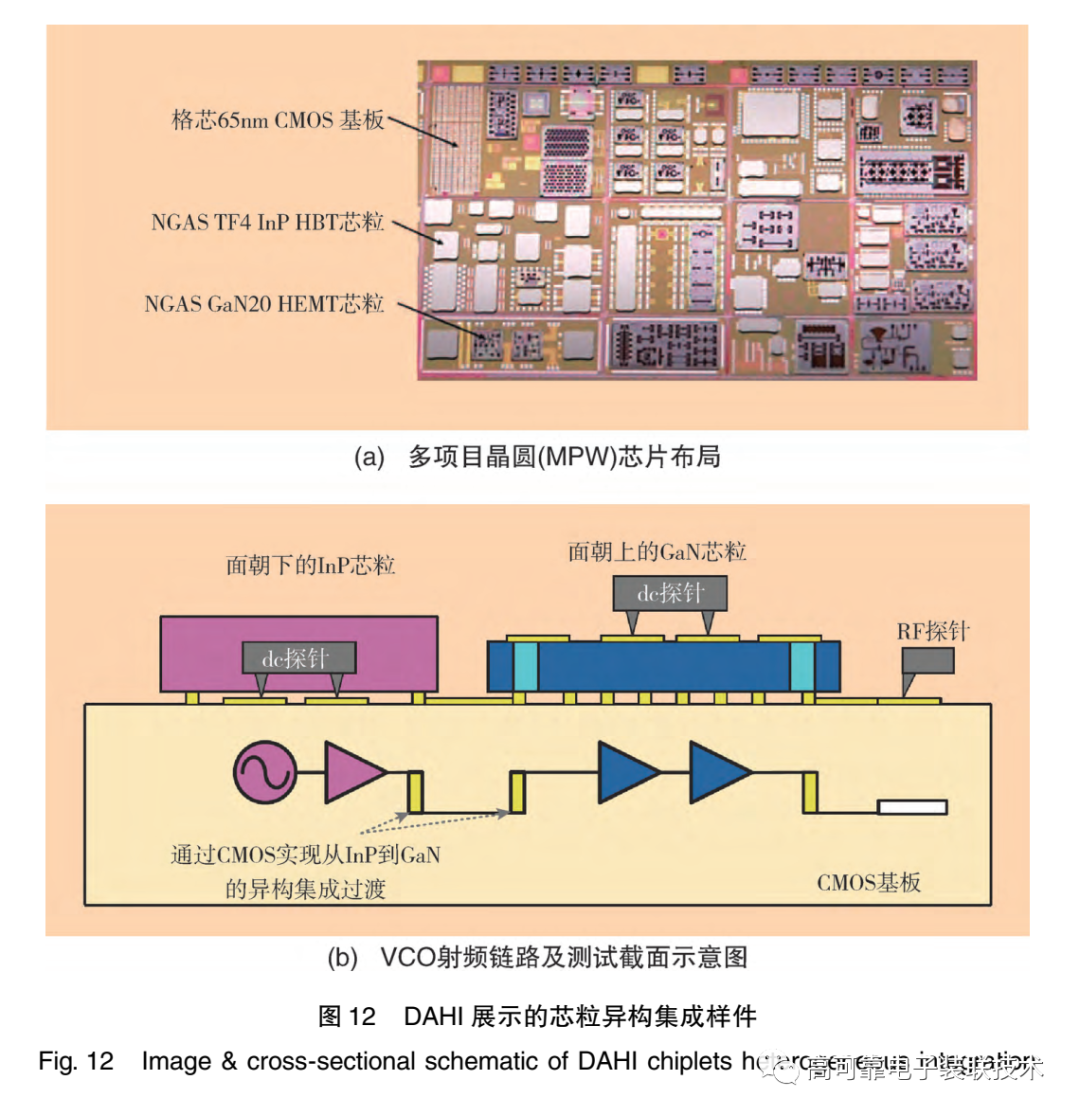

5MM× 2MM ×0。 46MM 的超小型气密封装 X频段 T / R 组件, 相比传统金属封装, 体积和质量仅为原来的 1 / 1000[38] ,如图 11 所示。NGST 进一步开发了 KU、 Q、 W 等频段的三维集成芯片, 并取得了与传统芯片几乎相同的性能,但传统芯片设计移植到新的 WSA 体系必须重新进行仿真设计, 以评估封装的空气腔对性能的影响, 并通过电路的调整优化实现预定的性能指标。为了充分利用不同材料和不同工艺的成熟半导体技术,以高性价比构建性能优越的微系统, DARPA 在 2013 年启动了多样化可用异构集成项目(DIVERSE ACCESSIBLEHETEROGENEOUS INTEGRA⁃TION, DAHI) , 采用芯粒集成(CHIPLET) 、晶圆键合以及外延转移等技术实现了例如 GAN HEMT、 INPHBT、 CMOS 等芯片间低寄生效应的紧密垂直堆叠互连, 如图 12 所示[39] 。

在 DAHI 项目所展示的集成范式下, 所集成的芯片无需更改其制程即可实现广泛来源的晶体管级集成,有关 DAHI 的研究成果已有较好的文献综述可供参考[39⁃41] 。与此类似的异构芯片堆叠集成技术在国内也得到了研究和开发,如中国电科 13 所公布的发明专利[42] 阐述了一种多通道幅相控制芯片,由上层的硅基 CMOS 译码电路芯片与下层的 GAAS 射频芯片通过直径 50μM~ 80μM 的金球键合实现垂直堆叠。射频芯片与数字芯片的直接混合堆叠无需额外的转接板, 集成密度和成本优势明显, 未来的工程应用将迅速增长。

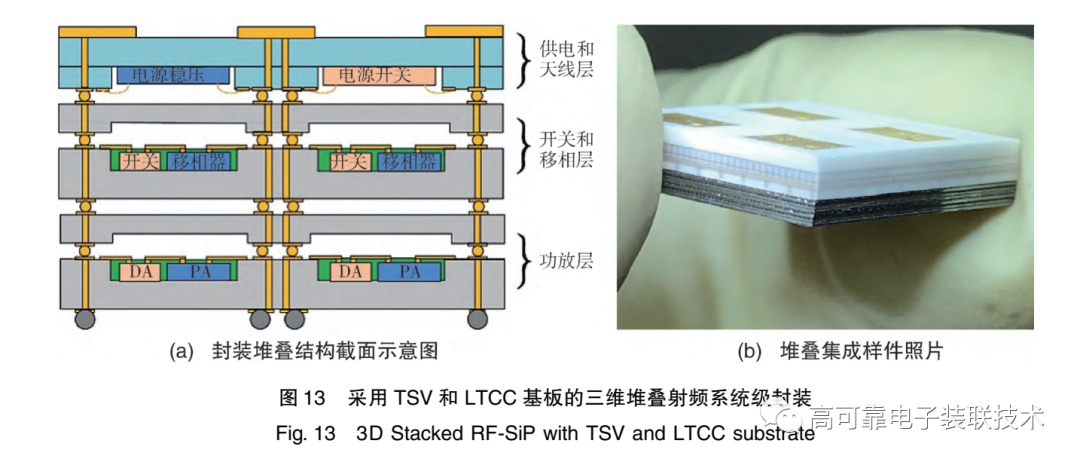

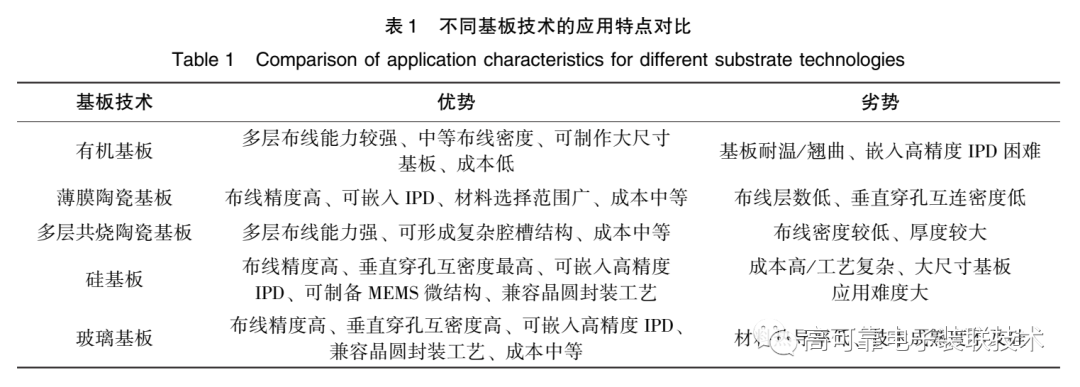

因芯片尺寸的限制, 仅通过芯片⁃芯片的三维堆叠集成难以满足电路的复杂度和集成规模需求,因此有必要在封装级的三维堆叠基础上进一步拓展集成密度,并借助封装结构提升封装内解决电磁兼容难题的灵活性。单独的封装堆叠单元由基板及装配的芯片构成, 典型的基板包括有机基板[43⁃44] 、 薄膜陶瓷基板[45] 、 共烧多层陶瓷基板[46] 、硅基板[47⁃48] 、 玻璃基板[49] 等。此外, 实现塑封穿孔互连(THROUGH MOLDING VIA,TMV) 的扇出封装[50]也可作为堆叠单元。混合基板封装的堆叠可充分发挥不同基板技术的优势, 以满足更为复杂的系统集成需求, 如图 13 所示[51] 的 4 通道发射模块, 它采用了 TSV 和 LTCC 基板混合封装堆叠方案,其中天线单元集成到 LTCC 基板上, 有效提升了系统集成度。一般来说, 不同的基板在封装中应用特点各异, 归纳如表 1 所示。但需要指出的是, 随着新的基板技术持续突破,优势和劣势对比并非一成不变。早期的堆叠互连技术多采用毛纽扣弹性互连方案[52] , 但由于毛纽扣的互连中心距和厚度均在毫米量级, 无法满足系统级封装需求。因此,封装堆叠主要采用 BGA 焊球互连[43] 、 微凸点互连[51,53] 以及晶圆键合互连[54⁃55] 等技术。

4 RF⁃SIP互连技术面临的挑战与发展方向

微电子技术已进入异构集成时代, 将系统级封装前沿技术应用到电子信息装备是一项重大的课题,如:美国国防部(DOD) 于 2019 年启动了高水平异质异构集成与封装(STATE OF THE ART HETEROGENE⁃OUS INTEGRATION ANDPACKAGING, SHIP) 项目, 正在充分整合 QORVO 等行业领先公司的最新射频异构封装技术, 满足下一代相控阵雷达系统、无人机、 电子战以及卫星通信系统在体积、 质量、 功耗和成本(SWAP⁃C) 上的需求。结合 RF⁃SIP 的需求, 应重点关注以下先进封装互连技术发展:

1)更高密度的无凸点互连技术。先进工艺节点的硅基 RF⁃IC 已经能够处理高达 300GHz的射频信号, 融合射频与数字的混合信号 SIP 将会加速发展, 并将采用 CHIPLET 集成方案低成本地实现 IP 复用, 在获得最佳系统性能的同时缩短产品开发周期。混合信号 SIP 对互连节距的要求将缩放至小于10μM 量级, 当前成熟并且广泛应用的微凸点互连很可能成为瓶颈。基于以上需求, DIE⁃TO⁃WAFER[56]或 WAFER⁃TO⁃WAFER[57] 无凸点直接键合(DBI) 可能是最优的互连解决方案。

2)高频高性能先进基板材料。在无机基板材料方面, 玻 璃/ 石 英 具 有 低 介 电 常 数 和 低 成 本 优势[58⁃59] , 随着玻璃穿孔互连工艺的成熟以及供应链的完善, 工程应用价值将逐步显现;而硅材料在MEMS 技术中得到了广泛深入的研究,在射频系统级封装领域正得到行业的密切关注[53, 55] ;碳化硅、氮化硅等材料的热导率、强度等性能突出, 有望在解决功率射频系统级封装中发挥重要价值。得益于 5G 毫米波商业化的推动, 高频低损耗有机基板材料的开发和应用发展迅速[60⁃61] , 其中作为晶圆级封装的关键材料, 介质损耗(DF) 低至 10 - 3量级的光敏介质对提升基板及 RDL 的射频性能具有重要意义。

3)热/ 电一体高性能互连技术。随着 GAN 等器件功率密度的提升, RF⁃SIP 中的热⁃电耦合更为紧密。因此, 在电互连结构中同时实现高效的热传导具有良好的前景, 如通过密集的实心填充通孔解决玻璃转接板散热性能不足的问题[62] 、 通过在TSV 转接板中引入液冷流体实现大功率散热[63] 等。宾夕法尼亚大学的 SHOEMAKER 等[64] 提出了在 GAN芯片上制作金刚石钝化层, 再用金凸点倒装集成到金刚石基板的互连架构, “结⁃封装” 热阻可低于最新的金刚石上 GAN(GAN⁃ON⁃DIAMOND) 技术。这些新兴的热/ 电一体高性能互连技术仍处于原理验证阶段, 后续亟需利用有效的热阻分析方法[65] 验证其性能, 并在工程环境下实现产品级的工艺整合。

4)芯片⁃封装的协同设计与优化技术。在高频下, 封装与芯片间存在的 “机、 电、 热、 磁” 耦合对性能的影响已不可忽略。比如应用倒装或扇出互连技术时,RF 芯片中的传输线、 电感与封装布线可能存在强烈的耦合, 底部填充材料除了提升产品可靠性, 也会改变传输线阻抗并可能使芯片性能漂移。为提高设计一次成功率,采用电磁仿真技术进行芯片⁃封装协同设计与优化是 RF⁃SIP开发中的一项关键技术[66] 。为了降低协同难度,需要针对特定的封装工艺开发组装设计套件(AS⁃SEMBLy DESIGN KITS,ADKS) , 并在此基础上建立基于模型驱动的 EDA 设计环境, 实现芯片与封装设计最大程度的解耦。

5 结论

先进封装互连技术是 RF⁃SIP 持续提升集成密度和性能的关键使能技术。芯片倒装、 芯片埋置与扇出以及三维堆叠是目前主流和最重要的先进互连技术:射频芯片倒装需要特别考虑芯片⁃封装协同设计及化合物半导体芯片的微凸点制备工艺;在射频系统级封装领域出现了多种芯片埋置与扇出技术变体,在降低传输损耗、 提升功率等方面进行了有效拓展;3D⁃IC 和 POP 两个层面的三维堆叠互连为RF⁃SIP 的技术创新打开了新的维度。为满足未来下一代电子信息装备 SWAP⁃C 的需求, 射频系统级封装的互连技术应重点关注无凸点互连、高频高性能先进基板材料、 热/ 电一体高性能互连、芯片⁃封装的协同设计与优化等技术的发展。

编辑:黄飞

电子发烧友App

电子发烧友App

评论