01

功放饱和功率处的增益讨论

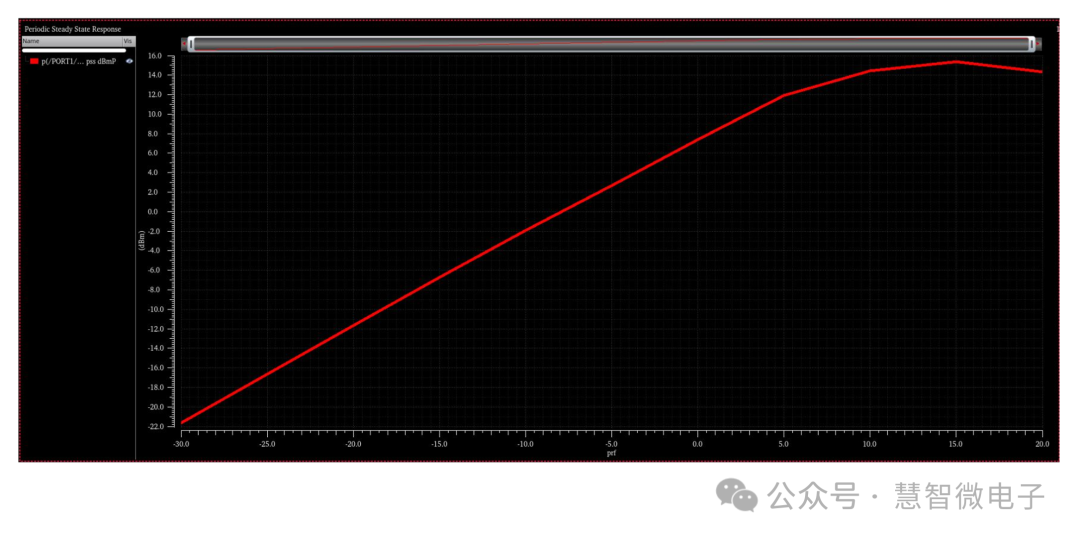

Q:大家好,我在设计仿真一个一级差分的CMOS功放,然后发现Psat为15.2dBm左右,但是对应的Pin都已经到15dBm了,几乎没有增益了。但我看一些一级的功放设计在到达Psat的时候还是有一点功率增益的,所以想问一下问题可能是在哪呢?谢谢了。

A:小信号的增益也偏小吧 差不多只有8dB。

Q:对对是的。

我的工作频率想在28GHz左右,晶体管宽度是320um,偏置在AB类,共源结构,所以是因为一级的增益太小了的关系是吗?

我看文章的确基本都是做两级或以上,但我现在还是学习仿真阶段所以暂时只设计了一级的。

A:压缩太多了,想输出高功率需要采用其他方法。

Q:好的,那如果想要一级的功放在达到Psat时仍然有功率增益,是不是要求更高的小信号增益呢?比如适当增加直流偏压等等?会不会直接设计两级的功放就不会有这个问题呢?谢谢了。

A:并不是增益越高输出功率就越高,小信号增益是看电压,功率需要同时考虑电压和电流,比如两路并联提升功率就是提升电流。两级功放是提升增益,对饱和输出功率没什么影响。

Q:好的谢谢,那么正常来说在饱和输出功率处应该要有一定的功率增益吗?像我图里那样功率增益几乎为零了是否属于不正常呢?

A:曲线没什么问题,你看看1dB压缩点在哪,压缩太多增益都会为零

Q:哦哦这样好的,我看了看输出的1dB压缩点的确比较低只有7.4dB左右,远小于Psat的值了。那这样应该是线性度不行导致增益压缩太多。

A:1dB压缩是指线性增益减小1dB,我看曲线输出也有13dBm左右,你可以把步长取小一点。

Q:好的谢谢,我试试看。我只知道如何算电流密度,比如单独一条finger流过的电流这样子,那这个功率密度是如何得知呢?

A:看PDK里有没有提供。

Q:好的,非常感谢。

02

GaN功放仿真不收敛问题如何改善?

Q:在仿真 GaN功放的时候,经常出现不收敛的问题,导致模型数据不连续,或者根本出不来数据。向大家讨教一下,有哪些方法可以改善?如果有相关资料或者经验就更好了,谢谢大家。

A:改一下HB的求解类型或者阶数。

Q:阶数我可以改小,比如改成两阶,求解类型改成那种?

A:不要用HB扫参,用SWEEP PLAN。用克雷洛夫求解。

Q:这个我也试一试,谢谢。

A:阶数低了好像不准哦。

A:知乎有一篇專門寫這個不收斂的或許你可以找找看。

Q:这个哇?https://zhuanlan.zhihu.com/p/57022677

A:是的,另外ads 的help也有專門寫不收斂的,你也可以看看。

Q:Help中是哪一篇能不能麻烦截图定位下,我查下,感谢。

A:“ 阶数我可以改小,比如改成两阶,求解类型改成那种?” 就是楼上的克雷洛夫求解 默认的是自动的。

Q:好的 谢谢 找到了 我试一下。

A:有时候微调匹配电路的参量也可以 也可收敛。

03

为什么仿真时开不开HB,小信号增益会有区别?

Q:请问一下,你们遇到过开着HB仿真和关着HB仿真,两者小信号有区别的情况吗?增益会掉两个dB,回拨也略有不同。

A:HB的小信号?

Q:就是这个HB的插件,仅把它开路,和不开路。仿真原理图。然后小信号会不一样。

A:DC有差异吗?

Q:有差异。

A:你做HB仿真,然后把HB开路掉了吗。那结果肯定不一样呀 。

Q:是的,开路了。为啥结果不一样了啊?

A:简单来说,做射频仿真,仿真器首先要找到非线性最强的点,一般就是设计的目标频率,后续所以的小信号仿真都是在这个解上做线性化分析,即小信号仿真,所以不做HB你求的不是射频解,是不对的。

04

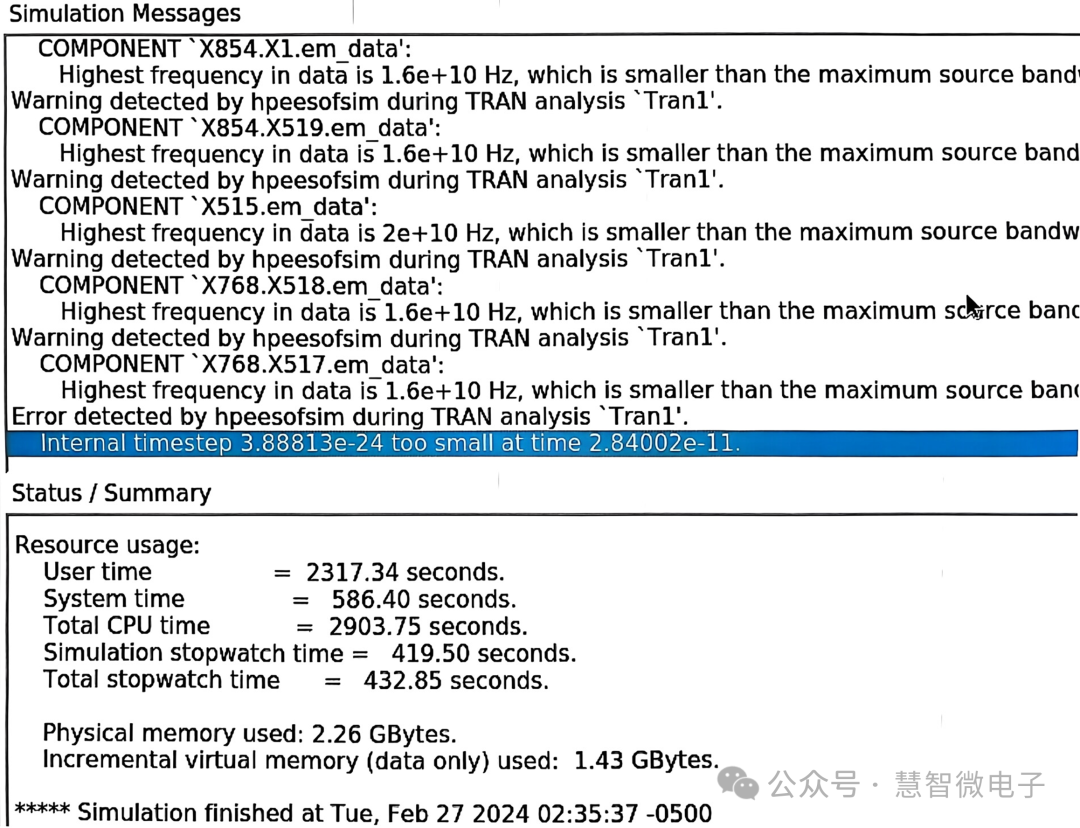

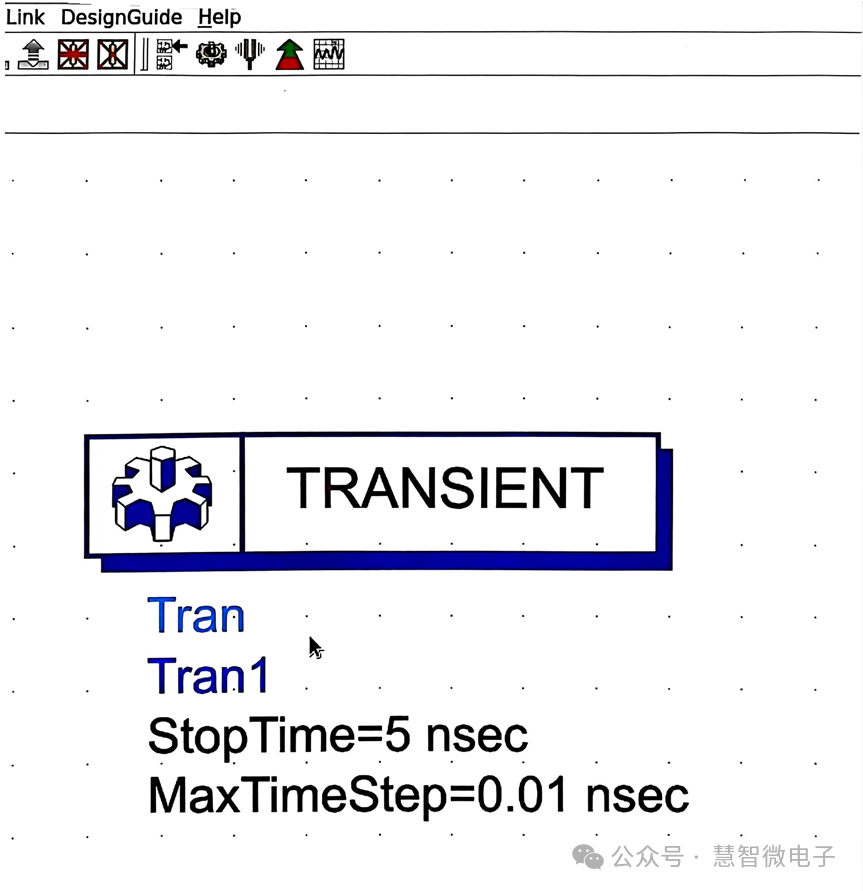

Tran 仿真时错误的处理

Q:大佬们,请问ADS跑Tran仿,出现这个错误怎么处理啊?

A:我之前都是调两个时间试,有时候就行了,感觉这俩时间要匹配。为啥出这个问题,也没搞清楚,有时候调一下电路就好了。

05

有如何确认 E8257D 信号源是否有内置隔直电容?

Q:想请教下各位大佬,E8257D信号源是否有内置的隔直电容?最近在测一个片子,没有片上隔直电容,在考虑用信号源给RF信号会不会影响管子偏置?

A:看一下help,不是在片测试的话可以在外头粘个电容。

06

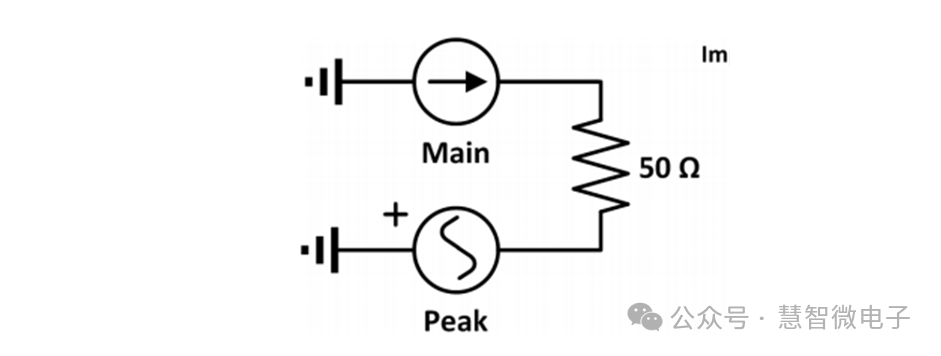

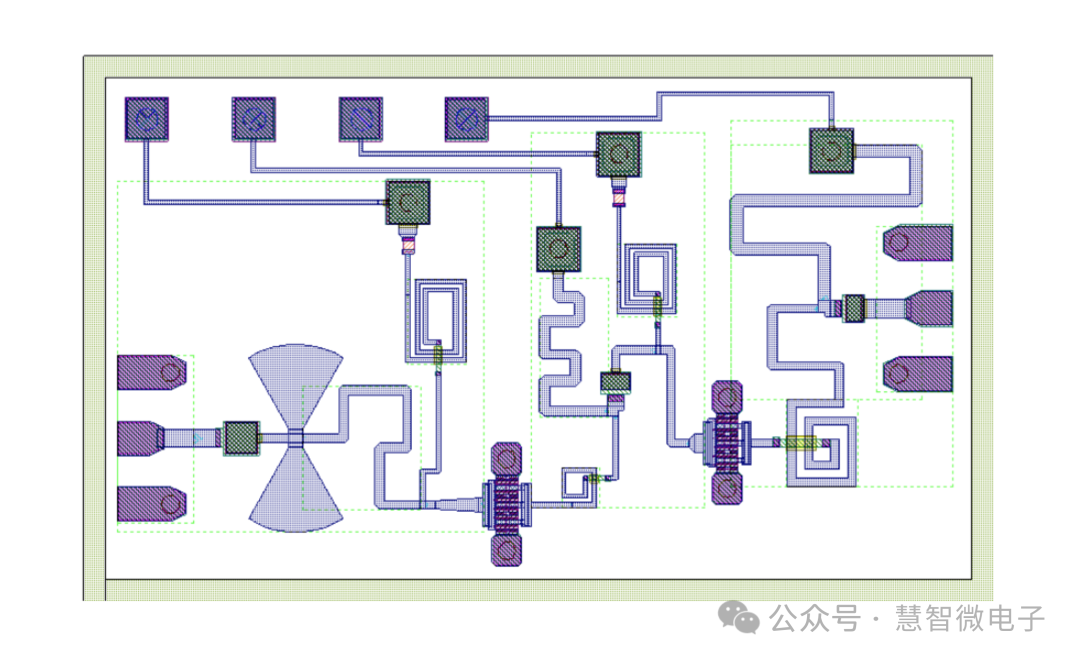

有关Doherty结构的讨论

Q:请教一下,经典Doherty的负载是和PA并联的,那像这样负载直接串联的,是怎么进行有源负载调制的呢?怎么实现Doherty的呀?

A:这是哪篇论文里的啊?

Q:这篇:

A:这本书里面有《2018 - Doherty Power Amplifiers》。

Q:感谢大佬。

07

功放调试是在调什么?

Q:家人们,请问功放调试是在调什么啊?

A:调很地方很多的啊,比如偏置,输出匹配等,仿真出来还是需要调试看看结果,国内用的仿真模型没有国外(sky qorvo)那么准,他们有自己的仿真模型。

Q:输出匹配是调阻拦吗?

A:Loadpull会调一下,看需求,比如功率或者线性度不好,需要调一调。

Q:好的,谢谢大神。

08

有关LNA级间匹配的讨论

Q:LNA做级间匹配的时候,要怎么选择第一级的输出阻抗和第二级的输入阻抗来进行级间匹配,要考虑增益,又要考虑驻波比,还有噪声,再就是匹配的时候,有没有必要先都把他们匹配到50ohm,然后再连起来,还是直接把前一级选定的输出阻抗和后一级选定的输入阻抗共轭匹配,实在迷糊的厉害,求各位大佬指点一下。

A:优先保证前级的噪声系数,后级影响根据选定的LNA结构调整,影响没有前级大。

A:级间不需要50欧吧 共轭匹配就行了。

Q:怎么选择前一级输出阻抗和后一级的输入阻抗,如果全安最大增益阻抗匹配的话,他们之间的驻波比会不会很差。

A:感觉本质上差不多,无非是zl变到zs,如果视作无源来讲,其实这部分应该是完全等效的?不知道这样理解对不对。

Q:有没有这一部分相关的资料,感觉可以找到参考的东旭太少了,很多论文都是一笔带过。

A:找找官方的文档吧,论文也就看个乐。

Q:哈哈哈,好的。

A:如果单论低噪放的话级间也不一定要共轭匹配。

LNA输入要匹配的原因是驻波太差会损坏前面的天线 输出匹配的原因是在系统做规划的时候是分模块给噪声系数 增益要求的 不同模块可能是不同的人做,如果中间不匹配,模块连在一起整个系统的增益就不能直接按dB值加 多级LNA都是你做 级间可以很灵活。

我也不认为我理解够了, 请指教。

Q:哈哈哈,好的。

A:我看原厂也就是LC直接匹的。

A:多级一般第一级优先考虑噪声,因为第一级对噪声影响最明显。级间设计主要是考虑损耗和功率。50ohm本身是空气介质同轴线功率容量和损耗平衡的结果。LNA本身都是小信号,所以我理解要不要改级间主要还是工作量和损耗的平衡。THz的mmic放大器(一般是PA)为了降低损耗有些级间就不是50ohm。但是级间不是50设计起来就很麻烦,因为级间所有被动器件都要改Zo。级间的被动器件包括传输线,测试也会变麻烦,毕竟一般探针都是校准到50ohm。然后第一级输入和最后一级输出一定都是50,中间不是50的话,一定有反射,对于LNA我感觉是得不偿失的。

A:如果是片上匹配的话,不涉及长传输线连接,做共轭匹配一般就是小信号增益最大了,此时级间驻波应该也是最好的。

Q:所以基本上,LNA一般只要做好第一级匹配就可以了吗?

A:也就是说级间匹配,最大增益阻抗和最小噪声阻抗可以基本不看,只需要把他们前后的输入输出阻抗共轭匹配就可以了。

A:“ 所以基本上,LNA一般只要做好第一级匹配就可以了吗?” 肯定不是啊,一般最小噪声和最大增益不是一个点。后级要做增益或者带宽的。

A:MMIC里面级间匹配一般用来调增益平坦度,其余的共轭匹配就好了。

A:LNA第一级负责噪声系数,第二级负责P1dB,增益之类的。

A:也就是级间匹配只要做好共轭匹配就对噪声,级间驻波比,增益没有太大影响,只需要针对增益平坦度再进行调节就好。

A:应该是。

Q:那LNA后面要是接Mixer输出的阻抗应该怎么设置呢?

A:lna的输出阻抗 与mixer的用hbsp或者psp仿真看到的大信号影响下的输入阻抗,用匹配网络将两者做共轭匹配,然后根据带宽再做一些微调。

Q:感谢老哥。

09

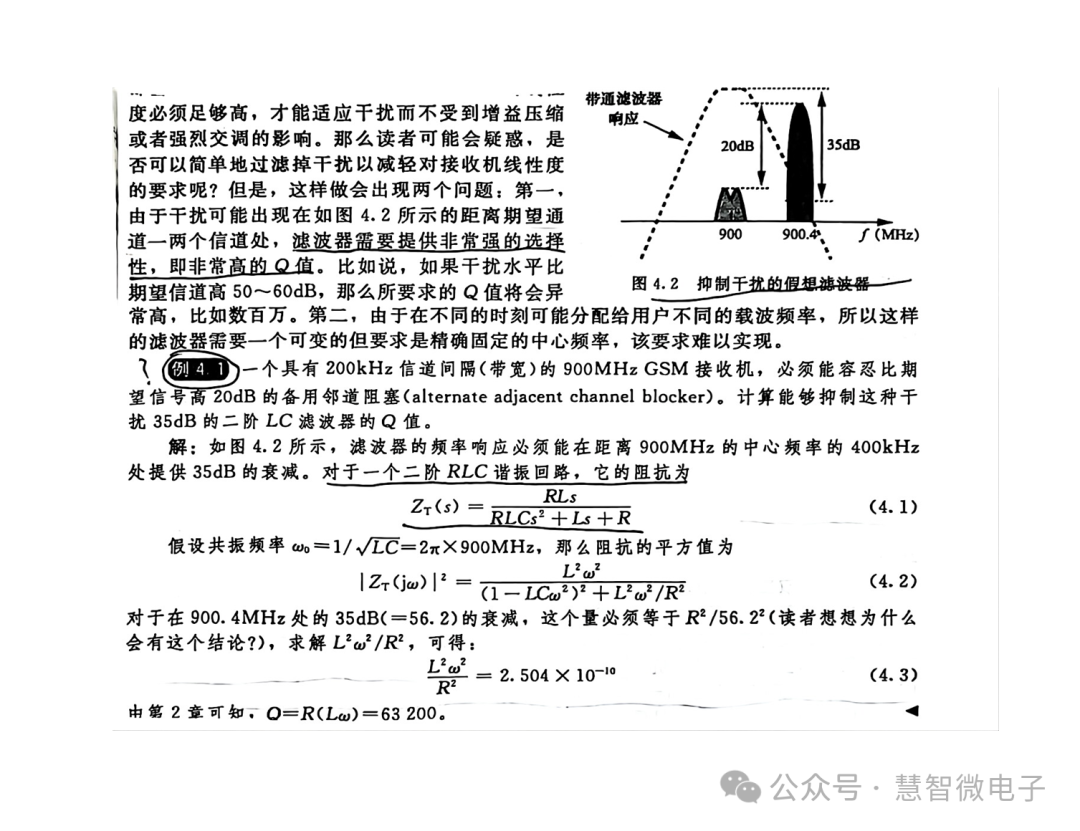

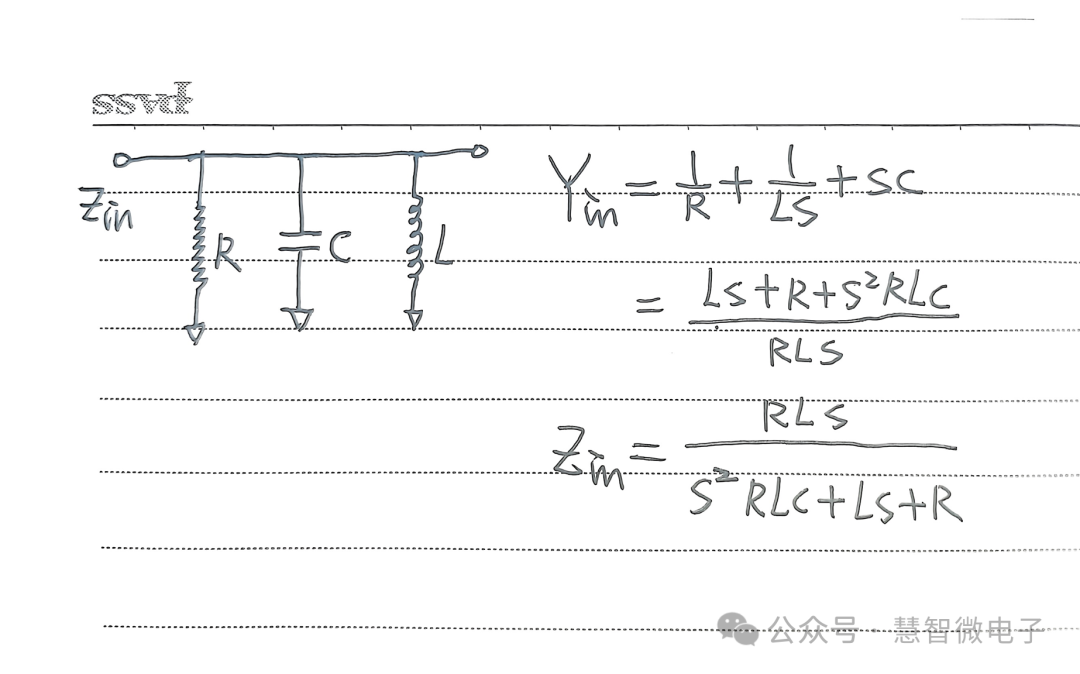

有关RLC谐振回路阻抗计算的讨论

Q:这道例题有没有好心人可以看看,《射频微电子学》第二版。

A:参考锁相环传递函数。

Q:感谢解答。

A:基本功啊,老哥。

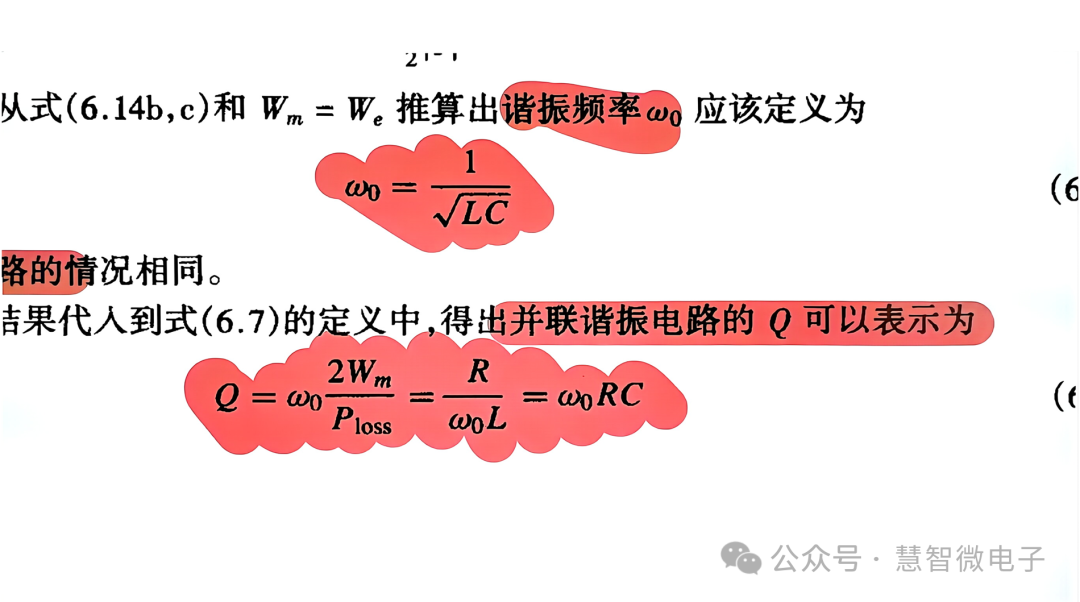

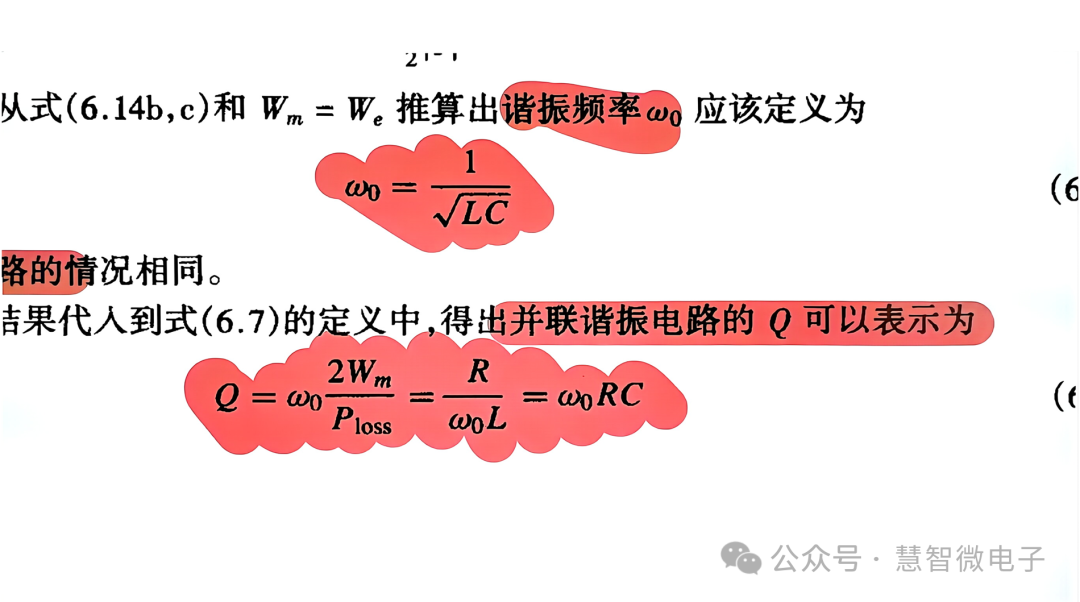

Q:哥 为什么默认认为是并联RLC,还有最后的这个Q值的公式,也有点不明白。

A:看公式一次项就知道了,另外滤波网络很少看到串联的,滤波网络需要将谐振能量锁住,一般是要有个回路。去翻书,高频电子线路第一章。

Q:这个

A:就这个。

A:这个w不是谐振频点,这个是抑制频点,需要用detw去替换吧。

Q:是不是需要重新从能量损耗的角度 用w算一下?

A:去转换一下。

Q:收到 感谢您不厌其烦的解答。

感谢您不厌其烦的解答。

A:都是从学生过来的,知识是开源的。

10

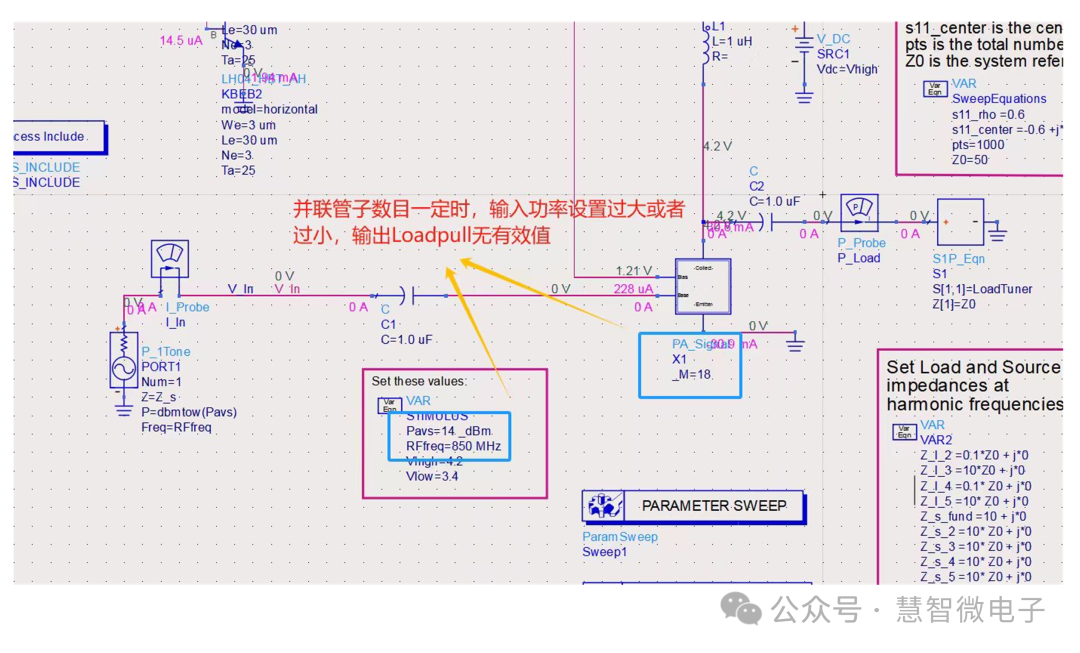

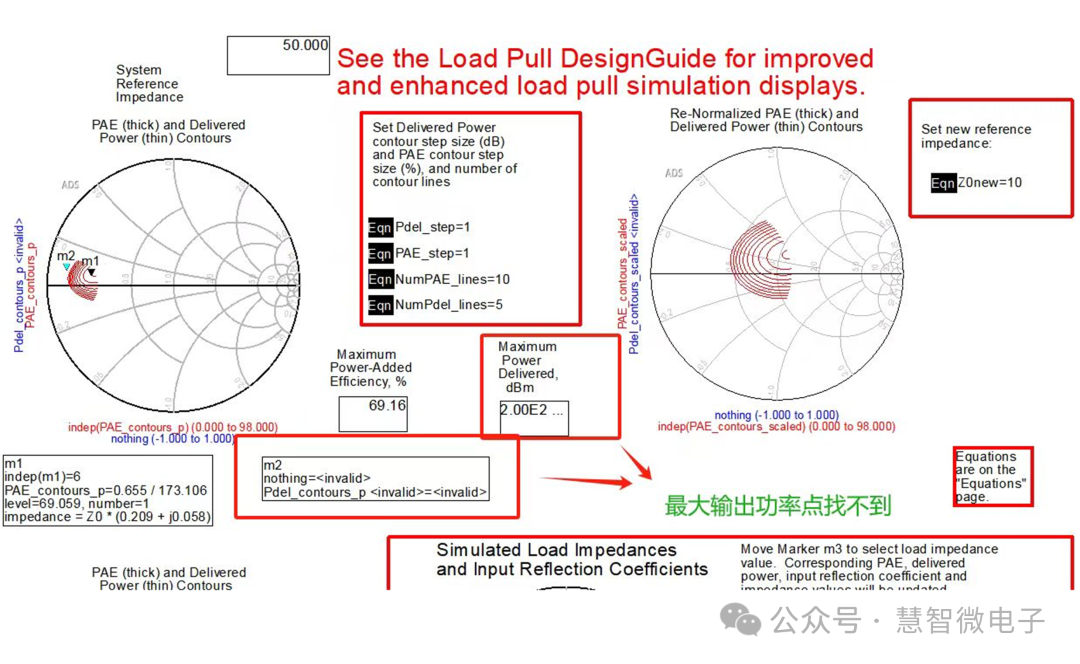

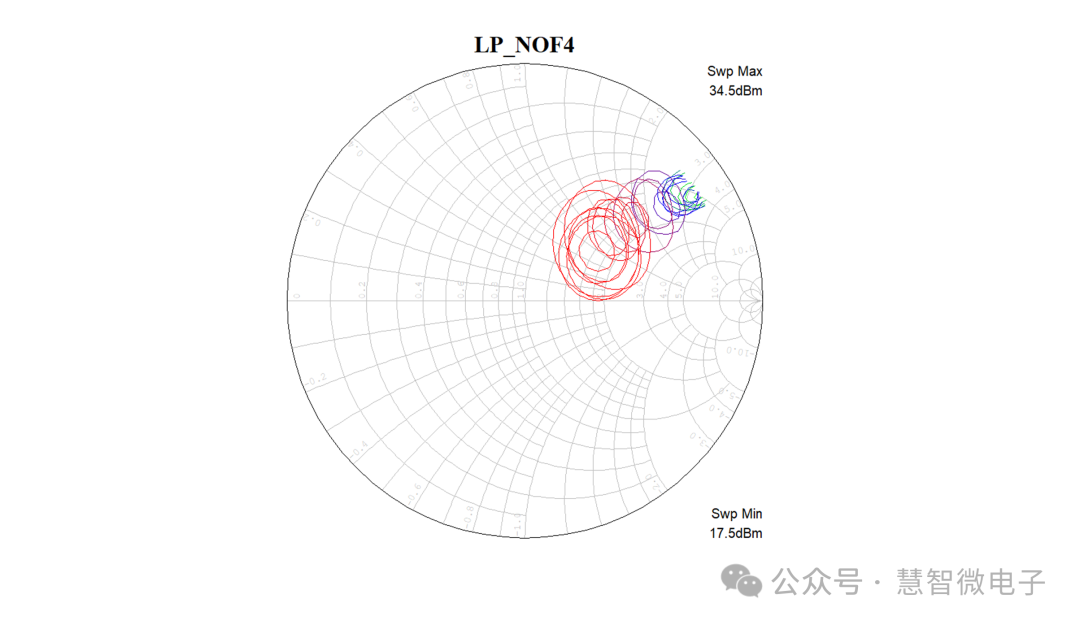

为什么Loadpull仿真时,输入功率过高过低都不会收敛?

Q:请教大家一个pa设计的问题,为什么Loadpull这里输入功率设置过高或者过低都会出现Loadpull不收敛的情况?修改收敛半径和收敛中心可以变收敛,但是具体原因方面不是很了解。

A:小功率的时候,圆跑到了阻抗点外面了吧。

Q:为啥小功率圆会跑?

A:因为传统理解的Ropt是饱和时的最佳阻抗,而不是小信号时的。Loadline不一样,所以一般其实是看P3dB的ZL。

11

MMIC电路中,走线过长有代替方案吗?

Q:调出来电路性能对的,但是线长都很长,能不能等效得缩短线长呢?全都走带线了,线宽改窄试了试影响不大。

A:你说的等效是?

Q:就是想办法把带线尺寸调小。

A:调的电路是什么?

Q:一个二级的驱放,GaAs的,才13dBm。

A:你把你管子合成那点微带调一调,或者串个电容,把匹配点拉过去,尽量微带走短。

A:应该频率不高,如果频率不高可以用集总参数的电容电感等效,频率高的话不行,要考虑Q值。

A:MMIC,输出匹配微带走3000um长,正常吗?功放。

A:满足要求就正常。

Q:我的是6.5G的,我算了下1000多μm带线电长度才50多度我算了下1000多μm带线电长度才50多度。

A:带宽要求不高就集总呗。

Q:啥意思?

A:没有带宽要求的话,就电容电感呗。

A:尺寸太大,成本吃不消,面积就成本,

A:你工艺介电常数多少?

Q:13,砷化镓的。

A:我9.6更离谱,90° 5000。

Q:那你更不好排了。

A:我都不用1/4波长了,直接搞个7 800参与匹配。

Q:多加电容电感替代带线匹配,是这个意思吗?

A:嗯。

A:高频电容电感可能不好找,主要是集总电容电感的模型不是纯电容电感,不过先试试吧。

Q:好的,多谢。

12

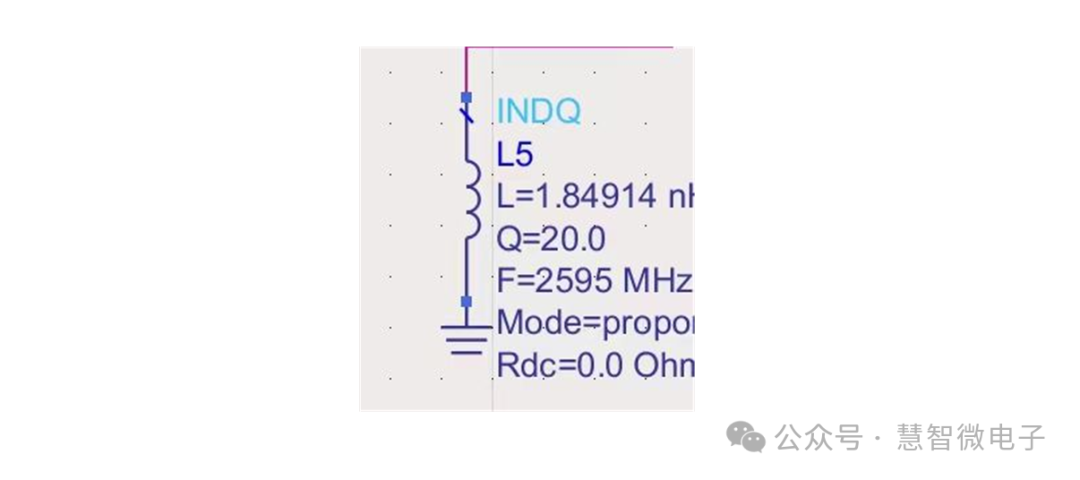

带Q值的电感,会产生寄生电容吗?

Q:请问下带Q值电感,会产生寄生电容吗?

A:Q值是衡量电感储存射频电磁能量的物理量,和寄生电容不太想关,这个就是一个电感,有可能随频率电感感值会有些许偏移。

如果想验证,你用ADS仿真S参数,查看结果那里提取它的电感值就好了,另外或者用一个理想同感值的电感跑S参数对比就行了。

Q:感谢。

13

有关ADS模板中gm计算公式的讨论

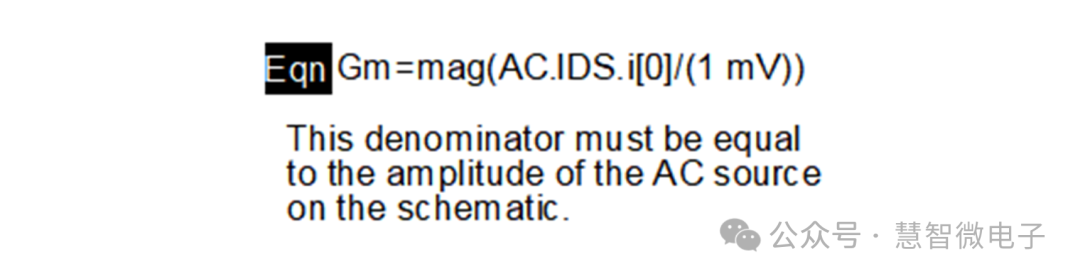

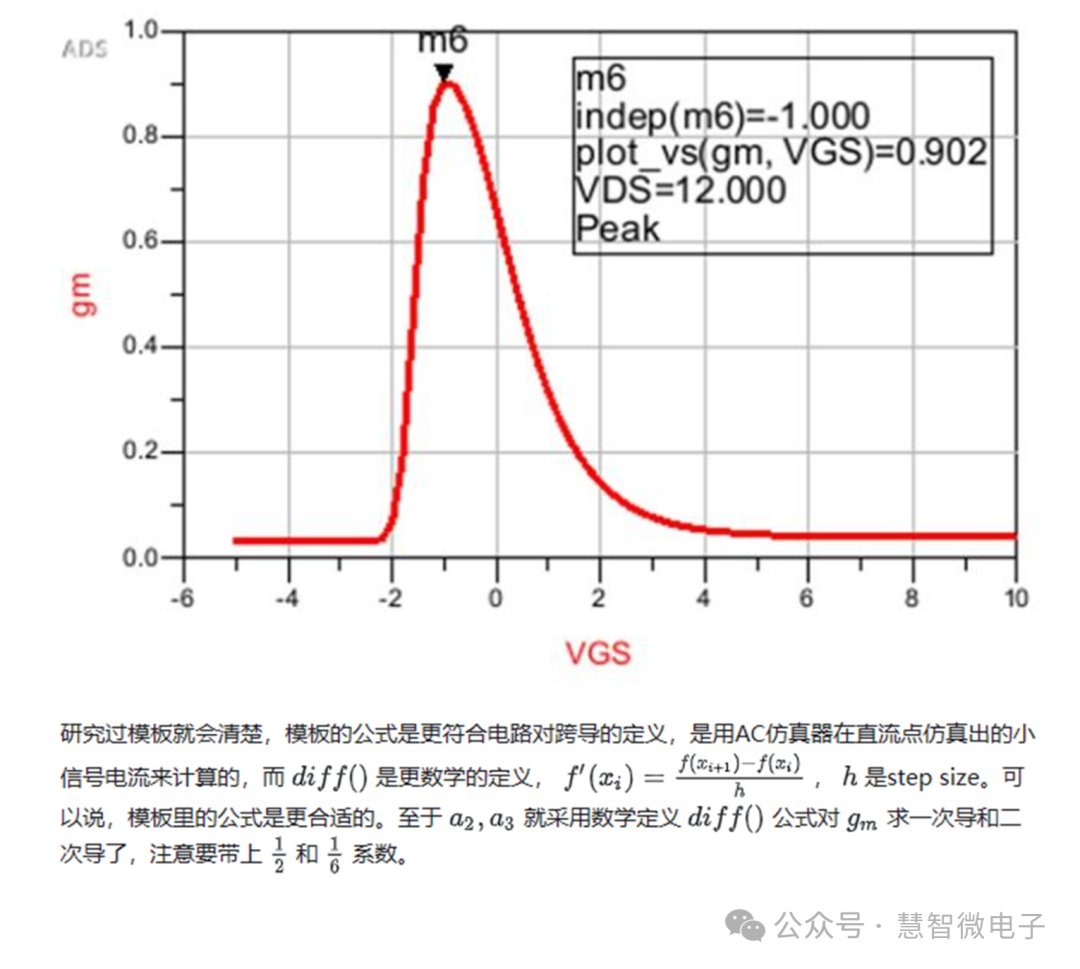

Q:各位大佬,ADS模板中计算gm的时候公式为什么是这样的?这个AC.IDS.[0]为什么表示了1mv的VGS变化引起的ID变化呀?

A:电流默认是毫安了?

Q:电流确实是mv单位,但是为什么这个可以表示▲ID呢?

A:MOS是电压控制电流,跨导gm不就是d IDS/dV?

图片来源于网络

Q:谢谢,谢谢,明白啦。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论