关键词: 显示板

摘要:目前,所有顶尖视频显示板生产商都在使用不同色彩像素尺寸的LED视频显示模块,结构相似但又各具特色。Maxim将其独特的技术应用于这一领域,推出了MAX6974 LED驱动器,并结合低成本、中等规模的FPGA芯片提供了一个基于LED的视频显示板参考设计。

概述

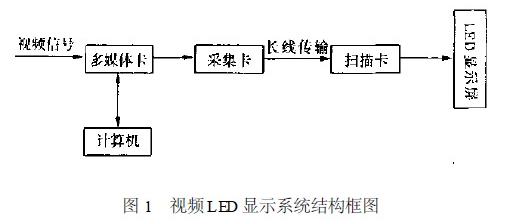

粗略估计,全球安装的大型LED视频显示板已经达到数万台。随着整体系统价格的下降,显示板操作流程的简化,LED视频显示板必将得到进一步的普及。本应用笔记介绍了一种基本的低成本LED视频显示模块。这一新型设计利用廉价的FPGA芯片完成数字视频比特流的分配,由MAX6974 LED驱动器构成QVGA (320 x 240)分辨率的LED视频显示器。该显示板可通过PC控制,用作辅助监视器显示任意文本、图表或多媒体信息。

目前的LED显示板架构

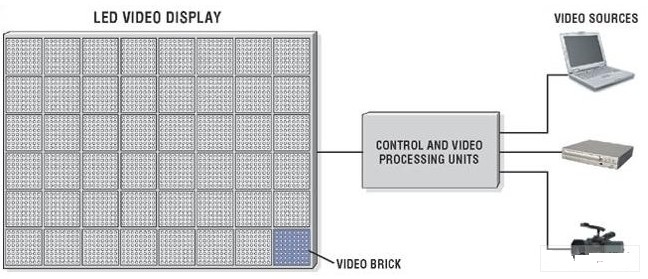

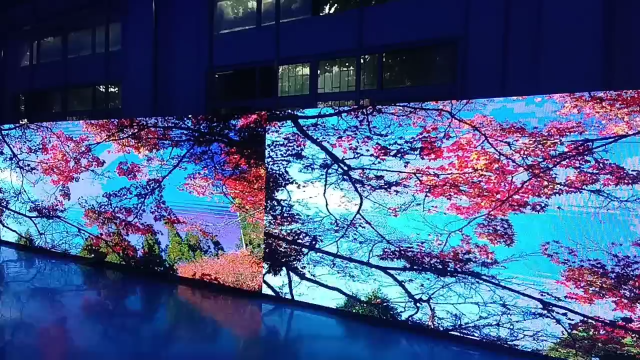

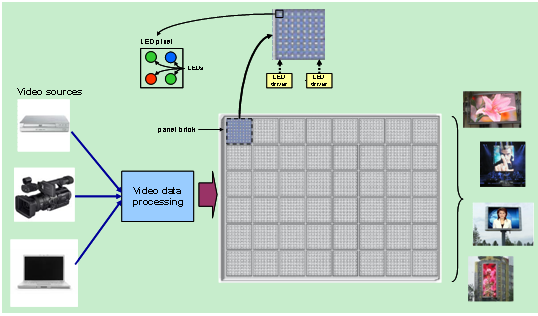

目前,所有顶尖视频显示板生产商都在使用不同色彩像素尺寸的LED视频显示模块,结构相似但又各具特色。视频显示模块像素尺寸大约在256至15552范围内,由厂商决定。将视频显示模块拼接在一起可以构成边长达到数米的视频墙(图1)。每块视频显示模块带有不同的PCB,PCB上安装了LED及其驱动器。另外,安装LED驱动器的PCB上还安装有FPGA和视频缓存芯片。

对于一个视频墙,视频显示模块之间通常采用同轴电缆连接。视频墙通过光纤连接到控制和视频处理单元。控制单元用于配置这些视频显示模块、正确选择视频源。视频处理器接收所选择的视频信号,进行格式转换后把正确的数据信息发送到相应的像素位置。视频处理器还需要进行数据缓存和比例调节。该应用的控制器和视频处理器单元属于专业设备,价格可能非常高。

图1. 目前LED视频显示板的系统架构

Maxim方案

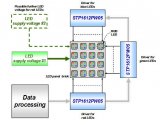

利用MAX6974 LED驱动器的独特功能,可以结合一片低成本、中等规模的FPGA构建一块LED视频显示板,通过PC控制整个系统(图2)。利用一块额外的视频接口PC卡可以支持不同的视频信号源,从而组成完整的LED视频显示板,只需要很少的电子元件,无需专业设备。

图2. 基于MAX6974的LED视频显示板系统架构

MAX6974 LED驱动特性

MAX6974 LED驱动器专为LED视频显示板应用而设计。每个LED驱动器包含24路同等的恒流、PWM LED驱动器端口,可驱动8或16个(双模) RGB像素。为适应视频或静态图片,消除黑屏现象,芯片的PWM速率非常高。当视频刷新速率为60fps (每秒帧)时,PWM速率约为7680Hz。MAX6974的数据输入接口包含一个LVDS时钟和一对LVDS数据,也可以通过数据输出接口串联MAX6974 LED驱动器,以提供更高的数据位,同样包含LVDS时钟和LVDS数据对。根据视频刷新速率和时钟频率,可以将数百片MAX6974器件通过LVDS接口连接在一起。利用这个接口,LED驱动器和视频显示模块PCB之间可以通过几英尺长的双绞线电缆连接在一起。

MAX6974可通过三种方式控制每个LED的亮度。首先,每个独立的LED (红、绿或蓝)都有一个12位的PWM亮度控制器,远远高于DVI?接口规定的每种颜色8位的分辨率,其余位可用于对比度调整,以适应不同的环境光条件;其次,7位PDM亮度控制用于调节所有LED驱动端口,这些PDM位可用于亮度控制。最后,每组LED驱动端口都带有步长为256的恒流控制(6mA至30mA)。这些校准步长用于配置不同温度下所要求的视频颜色。

基于MAX6974的LED视频显示板架构详细设计

该LED视频显示板参考设计采用一片FPGA实现视频数据为的分配,它还可以捕获控制帧,直接将它们转发到每片MAX6974 LED驱动器内部相应的寄存器。图3所示为QVGA分辨率(320 x 240)的参考设计框图,采用了TFP401A DVI接收器、用于存储EDID的AT24C02 EEPROM、EP2C20 FPGA和9600片MAX6974 LED驱动器,用于驱动76,800个OVSRRGBCC3 RGB LED。

图3. 参考设计功能框图

框图左侧的DVI信号由TFP401A DVI接收器接收,AT24C02 EEPROM提供EDID给Windows?操作系统。解串后的信号和TMDS解码信号发送到EP2C20。重新编排视频位,通过5个LVDS通道以32Mbps的速度传递到LED视频模块PCB列。每路LVDS包含2个差分对、CLKI(O)±、DIN(OUT)±、一个LOADI(O)引脚和一个GND (地)引脚,共6条线。每个LED显示模块PCB包含64片MAX6974 LED驱动器和512个OVSRRGBCC3 RGB LED。

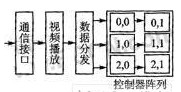

视频流分配和视频帧控制

DVI最低分辨率是VGA,该QVGA参考设计可用于隔行扫描的奇数或偶数像素。TFP401A DVI接收器的半像素时钟速率为12.5MHz。消隐期占用大约40%。由于MAX6974接口只用于奇数或偶数行,无需考虑消隐期,串行转换(24位RGB) QVGA数据速率为12.5/2/1.4 × 24 = 107.142857Mbps。考虑到DVI每种颜色8位分辨率,相应于MAX6974每种颜色的12位转换器,有效数据速率为107.142857/8 × 12 = 160.714286Mbps。FPGA缓存来自TFP401A DVI接收器的像素数据流,数据流划分成5组,然后将其发送到相应的LVDS通道。每个LVDS通道的数据速率为160.714286/5 = 32.1428571Mbps。

TFP401A DVI接收到的每个像素按照每行从左到右、每帧从上到下依次传递。MAX6974每个PWM帧格式要求相同的颜色信息,以8像素为一组传输(表1)。需要一个至少存储8个像素数据的缓存器支持这一格式转换。考虑到隔行扫描以及消隐,为了保持LVDS通道固定的传输速率,参考设计中用缓存器存储一帧视频数据。缓存器可能够将多片MAX6974器件在PCB的两端连接起来,避免从右到左使用较长的LVDS链路。

表1. MAX6974单个PWM数据帧格式

除传递每个端口的PWM信息外,帧头CMD位为010101、101010和111111的三个数据帧通过MAX6974 LVDS接口传送CALDAC、全局亮度PDM和配置信息(表2)。每个帧头包含24位,第一字节为同步模板11101000,随后是6位CMD和10位计数器值(CNTR)。每个端口PWM数据帧的CMD位是000000。

表2. MAX6974数据帧头格式

除PWM信息外,数据帧也利用基于PC的GUI通过DVI接口发送。数据帧类型由FPGA内部的相应电路识别。与PWM信息无关的数据帧格式如表3所示,HDR代表帧头。注意,每个端口PWM信息的视频帧不包括帧头。

表3. 视频显示参考设计,数据帧屏幕格式

表3介绍了320列像素和96行像素视频帧控制。1至5 LVDS通道分别传输0至63列、64至127列、128至191列、192至255列以及256至319列的视频和控制信息。在一个控制视频帧内,0至1行的每个像素都包含24位帧头配置信息(HDR);第32行和33行包含全局亮度PDM的帧头信息,第64行和65行包含CALDAC的帧头信息。本参考设计中,每组2行帧头之后的30行数据对应于LED显示模块PCB的30行信息。每个特定的LVDS列提供每行64像素的信息,用于传输每块LED显示模块PCB上64片MAX6974 LED驱动器的信息。每片MAX6974器件的每个像素包括24位控制信息,视频帧控制中不使用95行以上的数据。

视频显示板控制GUI

GUI (图4)用于配置参考设计中所有MAX6974的全局亮度PDM和CALDAC寄存器。GUI包括一个全局设置选项,用于调节视频显示板上所有芯片的相关参数,还包含一个器件制表符,用于调节每个芯片的参数。所有寄存器和MAX6974 LED驱动器的设置可以存储到一个文件,当视频显示板运行时下载数据。提供一个初始化设置文件,其中包括典型的寄存器参数的初始设置,大大简化了视频显示板的初始化过程。

图4. MAX6974视频显示板的GUI

GUI作为一个独立的操作窗口出现在Windows操作系统。一旦使能GUI上的Write按钮,它将创建一个视频控制帧并将其发送到视频显示板。视频控制帧只能按照60Hz的视频刷新率显示。视频控制帧也会占据视频显示板的整个屏幕;而FPGA会检测控制帧头行并将相应的信息发送到MAX6974寄存器。因此,视频控制帧的内容不会显示在视频显示板上。虽然视频帧刷新时也会传递控制信息,但人眼不会注意到这些更新。

方案实施

DVI接收板包括TFP401A DVI接收器和AT24C02 EEPROM,另外还有几个旁路电容(图5)。TFP401A DVI接收器实现串并转换和TMDS解码,并保证在半像素时钟速率下同时得到RGB位的奇、偶像素。因为DVI决定屏幕的最小分辨率是VGA,参考设计消除了每个邻近像素,支持隔行扫描。半像素时钟对于FPGA非常便利,允许其挑选所需要的像素。

在Windows操作系统识别显示器之前,通过DDC按照I?C协议检测显示器。然后,该显示器响应其EDID,包含制造商信息和操作信息。同样,AT24C02 EEPROM用于储存LED视频显示板的EDID信息。制造商ID必须从视频电子标准协会(VESA)获取,本参考设计中,借用DVI LCD显示器的EDID,储存在AT24C02 EEPROM中。当所有的三个地址引脚接地时,AT24C02 EEPROM的I2C地址是0xA0,这是操作系统将要搜索的地址。

图5. DVI接收机PCB (2.25" x 4")

FPGA板(图6)主要包括两个SRAM和一片Altera? FPGA器件。FPGA内部具有LVDS接口和存储器读取功能。该参考设计中,FPGA主要用于DVI数字视频信息的输出分配。FPGA的另一重要作用是识别数据帧配置、全局亮度PDM和CALDAC信息。当识别到视频控制帧时,这些数据帧,除了独立的PWM信息外,都被接收下来并直接发送到相应的MAX6974寄存器。

图6. FPGA PCB (7.5" x 9.5")

图7给出了FPGA的内部功能电路,一帧像素的数据位存储在SRAM缓存内。FPGA内部的行缓存器用于连接TFP401A DVI接收机和LVDS通道。两行缓存器,一行用于接收TFP401A接收的数据位,连接SRAM的另一行缓存器用于接收TFP401A DVI接收机的数据。同样,两行缓存器用于每个LVDS通道。FPGA提供完整的逻辑电路使DVI和LVDS数据吞吐率保持一致,并提供所要求的SRAM数据、地址以及控制信号的时序。因为SRAM为单端口,同时进行读、写操作时需要在FPGA内部配置存储器访问。

图7. FPGA内部功能模块

每片MAX6974驱动8个RGB LED,每个显示模块包含64个MAX6974 LED驱动器(图8),按照8行、8列分布,另外还有8行、64列的512个RGB LED。所有LED安装在PCB的一侧,LED中心距离为8mm (上、下、左、右间距),显示模块电路板尺寸为512mm x 64mm。所有MAX6974器件都安装在PCB的另一侧。在安装MAX6974器件侧,铺设电源和地线,包括1 x 6接头,共需2组1 x 6接头:一个用于左上角的LVDS输入接口,另一个用于左下角的LVDS输出接口。显示模块电路板可以嵌在视频显示板框架上,所有互联板都安装在框架内。邻近LED显示模块PCB之间的LVDS接口不需要额外引线。

图8. LED显示模块PCB (64mm x 512mm)和LED一起装配在一侧,MAX6974 LED驱动器装配在另一侧(PCB分为左侧(a)和右侧(b))。

/图8.pdf

图9给出了通用带有DVI接收机、FPGA和150个LED显示模块PCB的QVGA LED视频显示板。这些PCB排成5列、30行。DVI接收机和FPGA PCB如图所示,安装到视频显示板的上方,可以很容易地隐藏到LED显示模块PCB的后面。

图9/视频显示板装配图.pdf

.功耗

3.3V VCC供电时,每片MAX6974的工作电流为28mA (CALDAC关闭)或54mA (CALDAC使能)。一个LED显示模块PCB上包含64个MAX6974 LED驱动器,工作电流为1.8A或3.5A。采用5V VLED供电时,MAX6974每个端口提供的最大LED电流为30mA。512个RGB LED显示模块的最大电流为46A,需要多个3.3V和5V电源为整个视频显示板供电。

80 x 64 LED视频模块

图10所示9个LED PCB安装在一个框架内(可安装10块PCB),FPGA和DVI接收机的PCB安装在背面(图11)。整个QVGA显示板安装在15个(3 x 5)这样的框架上。

图10. 一块可安装10块LED PCB的框架

图11. 框架背面

电子发烧友App

电子发烧友App

评论