关键词: MPEG-4 , SoC , 加速器 , 视频解码

随着MPEG-4应用的普及, 符合MPEG-4标准的视频在手持设备上的应用越来越广泛, SoC技术可以在完成其它功能的同时, 在手持设备上低成本低功耗的实现MPEG-4视频解码。而基于SoC的解码方案可以有多种, 例如采用CPU 内核软件解码,也可引入DSP核, 或者设计专用的硬件加速电路。但是, 软件解码在系统繁忙时难以满足实时性要求,引入DSP核会使SoC的芯片成本大为增加, 所以本文将MPEG-4的解码电路作为SoC芯片中的一个硬件加速模块来实现。

在手持设备应用中, MPEG-4 视频简单层(Simple Profile) 最为常用, 而其中计算量最大的部分是反离散余弦变换( Inverse Discrete CosineTransform ) , 所以反离散余弦变换的实现是加速MPEG-4 解码的关键。有很多优秀的设计专门以处理IDCT为目标.本文描述的MPEG-4解码加速器基于AMBA 总线, 作为高速总线(AHB) 上的一个主设备, 对四个亮度块(block) 和两个色差块组成的宏块(macrob lock) 一起做IDCT 运算, 并根据配置完成IDCT前的反量化和IDCT后运动补偿的图像叠加, 最终将结果写回显存。整个过程高度并行处理。

本文第1部分主要介绍IDCT快速算法的选择和优化, 第2部分讨论硬件结构和设计技巧, 第3部分介绍仿真验证和综合结果。

1 二维DCT?IDCT 算法描述及快速算法的选择和优化

1.1 算法描述

对于输入矩阵f (x , y ) {0≤i, j2次乘法, 一个块有N2 个象素点, 总共需要N4 次乘法计算, 因此计算量相当大。

1.2 快速算法的选择

二维IDCT 可以写成:

上式括号内是对F (u, v ) 的一行作一维IDCT 变换, 括号外是对行IDCT 的结果做一维列IDCT变换。如不考虑系数2/N , 二维的IDCT 就分解为对矩阵F (u, v ) 先做行IDCT 再做列IDCT 的2N 次一维IDCT 变换。(本文中取N = 8)。

对于一维IDCT 有许多优秀的快速算法。其中一种是将IDCT 原始的变换矩阵分解成几个利于计算的变换矩阵, 然后逐步计算。还有一种是利用了IDCT的奇偶对称性以及余弦函数的和差化积性质最大程度的共用乘法器。虽然后一种的乘法次数为12次, 少于前一种的16次,但由于前一种的乘法集中在输入附近, 也就是说绝大部分乘法的其中一个乘数是输入F(k ) , 因而可以通过提前判断输入F(k ) 中是否有较多的0 元素从而直接跳过一部分的乘加运算, 达到加速的目的。MPEG-4 解码的IDCT 输入中, 有大量的0, 所以前一种的算法更有利于MPEG-4 解码。其算法流程如图1。

图1 chen 算法流程Ci= cos( iπ/16)

1.3 算法的优化

1.3.1 长乘法的处理

在图1的虚线中, 前一级乘加运算的结果要与C4相乘, 如果输入数据F(k ) 和系数Ci都是16位数据, 为了保证精度就要使用32 位乘16 位的乘法器,这必然成为整个电路中的关键路径, 影响其性能。若用下面的式(4) 对虚线内的条路径做变换, 虽然增加了乘法数目, 但是不仅去除掉32 位乘16 位的乘法器, 而且有利于下文将要提及的OnlyDC 和Halfzero情况的加速。

变换后的虚线内的算法流程如图2 所示。

图2 chen 算法变换Ci= cos( iπ/16)

1.31. OnlyDC 和Halfzero

本文将F(k )分为三种情况:

(1) F(k )只有F(0)为非零数据, 我们称这种情况为OnlyDC;

(2) F(k )中F(0) , F(1) , F(2) 和F(3) 为非零数据, 其他四个数据都为零, 这种情况称为Halfzero;

(3) 其它情况都归入普通情况。我们用软件直接解码的方法对典型素材作了统计(见表1) , 发现OnlyDC 和Halfzero的情况占了很大比例, 加速这两种情况的计算对加速整个视频解码的IDCT 运算有重要意义。

由一维IDCT 式(5) 可以看出, 对于OnlyDC 情况, f ( i) 就是F (0)/1.414 。

其中c (0) =1/1.414 ,c ( i) = 1, i= 1, 2....N - 1。如果我们把每次行和列的一维IDCT 结果放大2 倍得到f ′( i) , 对于 OnlyDC, F(0) 就是f ′( i) , 不需任何计算。这样两次一维IDCT 运算后得到的结果f ′(x , y ) 将为f (x , y ) 的2 倍, 故只要将f ′(x , y ) 右移一位就可以得到正确的f (x , y )。由图1 和图2 可以看出, 在所有的F (k ) 到f ( i) 的计算路径上, 都出现了且仅出现一次F (k ) 乘Ci, 这样我们对常数Ci 取值时直接取2cos( iπ/16), 就达到了将一维IDCT结果放大1.414倍的目的。

对于Halfzero 的情况, 可简化图1 和图2 中的F(4)、F (5)、F (6)、F (7) 的相关路径, 得到Halfzero 的算法流程(如图3)。此时时乘法总数为10 次。

图3 Halfzero 的算法流程 其中Ci = 2cos( iπ/16)

对于一般的情况, 根据图1 和图2 的流程计算,取C i = 2cos( iπ/16) 。乘法总数22 次。

2 硬件结构和设计技巧

2.1 整体结构的选择

MPEG-4 加速器的的整体框图如图4 所示。其中slave 模块负责模式配置, 接收数据, 反量化并判断OnlyDC 和Halfzero。写向slave 的数据经过反量化操作后进入Xmem。MPEG-4 加速器的Cont rol模块控制整个解码流程。Idct8x1从Xmem 中读出原数据做一维IDCT 并写回Xmem。

由于Xmem 的带宽限制IDCT 8x1只使用两个乘法器, 把乘法排列紧凑后, 普通情况一维IDCT 需要20个周期, Halfzero 需要14个周期。Master 负责取运动补偿图像数据, 并在完成IDCT 变换和叠加后将结果放回显存。每次数据写回显存后, Control 模块会将Xmem 清零, 这样下次解码操作只需将非零数据写入Xmem , 减少了数据的写入时间。

双端口片上存储器Xmem 负责存放IDCT 的中间数据和计算结果, 其中数据通过A端口进行IDCT 变换, IDCT 结果通过B 端口进行叠加, IDCT 计算和运动补偿叠加可以通过A、B 两个端口并行处理。单端口Ymem 负责存放MA STER取回的运动补偿数据。Xmem 和Ymem 是零等待的片上存储器, 而且在外部总线上是可见的, 所以在MPEG-4 加速器不使用时, 它们还可以作为整个芯片高速的缓冲区使用。

图4 M PEG-4 加速器的整体框图

2.2 OnlyDC 情况的处理

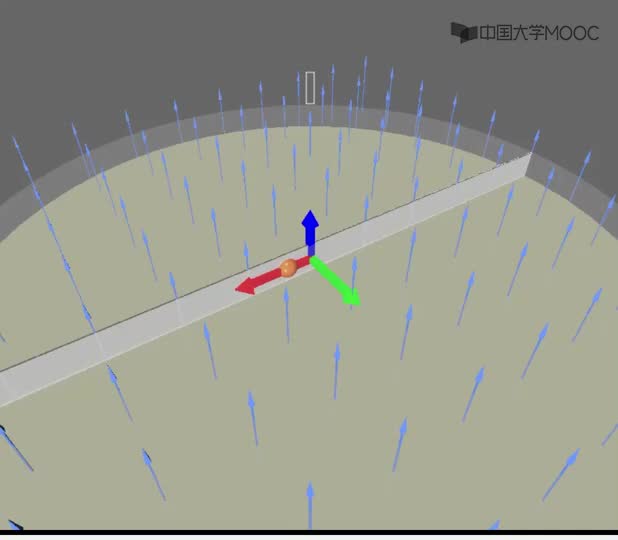

在进行二维IDCT 的行变换时, 一般情况和Halfzero情况都会向Xmem 写回8个计算结果; 如果是OnlyDC 则不对Xm em 做任何读写, 所以在做列IDCT时必须对idct8x1 发出的地址进行重新映射, 使其指向这一行的第一个数据。如图5 所示,IDCT发出的地址指向当前要进行IDCT变换的列中的数据, Control 模块中的Address Remap 逻辑会根据On lyDC 状态将地址转换为指向第一列的有效数据。对于列IDCT 我们直接按照一般情况计算。

图5 地址重映射

3 仿真验证和性能分析

本文的设计流程是首先确定IDCT算法, 并用其C语言描述作为设计规范。然后根据设计规范用verilog RTL 描述硬件, 用verisity公司(已被Cadence公司收购)的E语言搭建验证环境, 并将C语言的设计规范嵌入E验证环境中, 通过E语言产生随机激励, 同时发给verilogRTL和C设计规范, 并将两者的结果作比较。这样既保证了硬件实现和C设计规范完全一致, 又通过C设范的重用缩短了验证周期。

我们使用SYNOPSYS 的Design Compiler 对本设计进行了综合, 综合采用SMIC的0.8um的标准单元库。结果显示本设计的关键路径在反量化处, 因为此处直接使用了一次乘加操作。表3给出了本设计的特性。本设计完成更多解码功能, 主频更高, 乘法器更少, 而且引入了可与系统复用的片上内存。

我们分I帧和非I帧两种情况分析本设计的处理时间。在处理I 帧时要进行反量化, 不需要运动补偿叠加。由于反量化是在数据输入的同时进行的, 所以处理时间由非零值的写入时间Tinput , IDCT 计算间Tidct和写回显存的时间Toutput三部分组成。这三部分如图6 (a) 所示的并行处理。在处理非I 帧时, IDCT的结果需要与运动补偿的结果叠加, 所以处理时间时由非零值的写入时间Tinput , IDCT 计算时间Tidct,取运动补偿数据时间Tfetch , 叠加并写回显存的时间Toutput四部分组成。如图6 (b) 所示的并行处理。

(a)I 帧处理时间 (b) 非I 帧处理时间

图6 处理时间

其中取运动补偿的结果和最后写回现存都要占用总线接口, 所以要依次进行。从这两幅图可以看出, 并行处理使得这两种情况总的处理时间是相同的。以行IDCT一般情况15% ,OnlyDC情况70% , Halfzero情况10% 计算, 一个block 的IDCT 所需的周期Tidct为:

T idct = (0 × 70%+ 14 × 10%+ 20 × 20% ) × 8 + 20 × 8 = 203.2 (个周期)

如不考虑回写时由显存造成的延时,M PEG24加速器处理的处理时间T 为:

T = Tinput + 6 × Tidct + Toutput = 6 × 64 × 15%+ 6 × 203 + 64 = 1340.8 (周期/宏块)

4 结论

本文给出了一种应用于嵌入式系统芯片的MPEG-4 解码加速模块。本设计面向MPEG-4 简单层, 将四个亮度块和两个色差块一起并行处理, 使流水线更加紧凑; 由于内部存储器的带宽有限, 我们只使用两个乘法器完成IDCT , 并使用较小面积的代价将于IDCT密切相关的反量化和运动补偿叠加一起实现, 这样进一步减少了数据在总线上的传输, 更有利于提高速度和减小功耗。本设计在以北京大学微处理器研究中心UN ITY-1为内核的SoC-UN ITY805+ 中, 已经得到应用。实验表明可以实现MPEG-4简单层CIF格式的视频解码。

电子发烧友App

电子发烧友App

评论