利用语音编码技术可有效降低信息存储量、提高信道利用率。混合激励线性预测(MELP)语音编码算法能在较低码率下提供较高的语音质量、自然度和清晰度,已成为美国国防部新的2.4 Kb/s的语音编码标准。语音编码技术在当今数字通信尤其在无线系统中发挥着越来越重要的作用。

Nios II处理器是Intel公司为Altera公司推出的32位精简指令处理器软核。在Altera公司推出的软件SOPC中加载Nios II软核和相应的外围接口以及与定义相应的自定义指令,对设计进行综合,下载到FPGA中就可以方便地实现一个具有高速DSP功能的嵌入式处理器[1]。

由硬件实现复杂的算法通常比软件实现更高效。利用Altera公司的Nios II嵌入式处理器的定制指令,可以把用户自定义的功能直接添加到Nios II CPU的算术逻辑单元(ALU)中,以加快专项任务的执行速度。自定义指令的优势就在于可以将程序代码中的瓶颈部分改用硬件指令支持,用自定义的指令使程序得到加速。

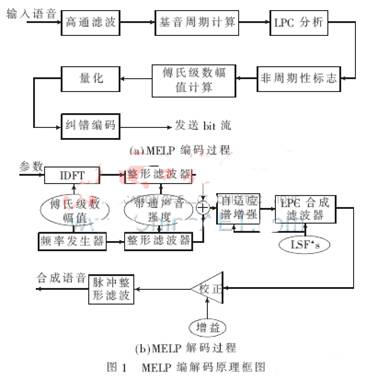

1 MELP的构成

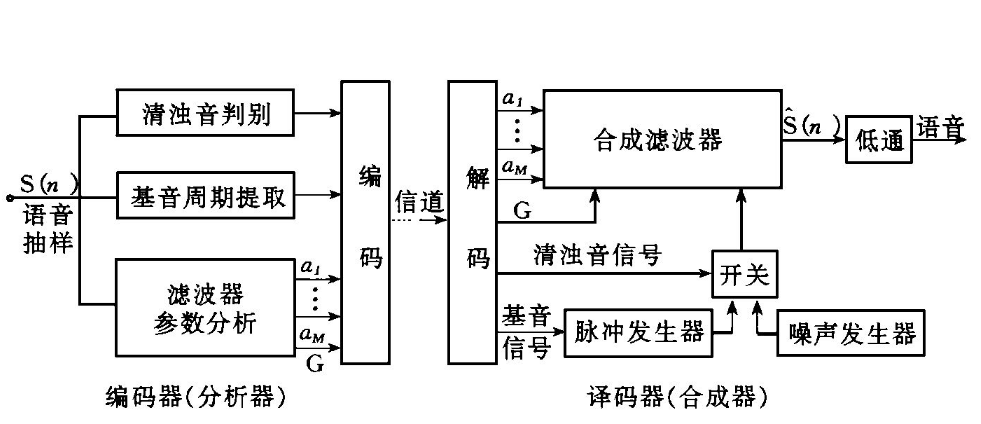

MELP声码器的采样率为8 kHz,每个样点值用16 bit量化,每180个样点为1帧,帧长22.5 ms,每帧量化bit数为54 bit,总的速率为2.4 Kb/s。

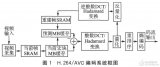

MELP声码器是建立在传统的二元激励LPC模型基础上,采用了混合激励、非周期脉冲、自适应谱增强、脉冲整形滤波和傅氏级数幅度值等5项新技术,使得合成语音能更好地拟合自然语音。图1所示为MELP编解码原理框图[2]。

2 Nios II可嵌入软核的特点

Nios嵌入式处理器是用户可配置的通用RISC嵌入式处理器,是一个非常灵活、强大的处理器,因此已成为世界上最流行的嵌入式处理器[3];采用改进的哈佛存储器结构,CPU带有分离的数据和程序存储器总线控制。SOPC Builder系统开发工具允许用户容易地指定系统中Avalon控制器和从属设备之间的连接,这些从属设备可以是存储器或外围设备。

Nios指令总线为16位,用于从存储器中读取指令。Nios数据总线宽度为16位或32位,分别用于Nios CPU的16位或32位配置。

2.1 指令系统

Nios指令系统支持C和C++程序编译,包括算术和逻辑运算、位操作、字节读、数据传送、流程控制和条件转移等指令。指令系统包含丰富的寻址方式以减少代码长度和提高处理器性能。

2.2 寄存器组

Nios CPU有1个大容量的窗口化的通用寄存器组、8个控制寄存器、1个程序计数器和1个用于指令前缀的K寄存器。通用寄存器在16位Nios CPU中是16位,在32位Nios CPU中是32位。寄存器组可配置为包含128、256或512个寄存器。软件可以通过包含32个寄存器的滑动窗口存取这些寄存器,滑动窗口的移动间隔是16个寄存器,且允许快速地进行寄存器切换,加速子程序的调用和返回。

2.3 高速缓存

可配置的Nios CPU可以有选择地包含指令和数据高速缓存。高速缓存通常通过提供局部存储系统提高CPU的性能,这个局部存储系统可以快速地响应CPU产生的总线事件。Nios高速缓存的实现是采用简单的直接映射的连续写入结构,这种结构设计能够用最少的器件资源获得最大的性能[4]。

2.4 中断处理

Nios处理器允许多达64个矢量中断。中断源有三类:外部硬件中断、内部中断和软件中断。Nios中断处理模式能够准确地处理所有内部中断。

用户可以有选择地禁止TRAP指令软件中断、硬件中断和内部中断。这项选择能够减少Nios系统的大小,但只用于处理器不运行复杂软件的系统。

2.5 硬件加速

Nios指令系统可以利用硬件提高系统性能。特殊的周期密集型软件操作可以用硬件显著地提高系统性能,这种特性通过修改指令系统提供[5]。

Nios处理器有2种指令系统修改方法:自定义指令和标准CPU选项[6]。

2.5.1 自定义指令

开发者可以通过向Nios处理器指令系统中添加自定义指令加快时间要求严格的软件算法,也可以用自定义指令在单周期和多周期操作中执行复杂的处理任务。另外,用户添加的自定义指令逻辑电路可以访问Nios系统外的存储器和逻辑电路。

复杂的操作序列可以在硬件中简化为单指令的执行。这种特性允许开发者为数字信号处理(DSP)、分组标题处理和计算密集操作优化自己的软件。

Altera公司的SOPC Builder软件提供了一个图形用户界面(GUI),开发者利用GUI可以向Nios嵌入式处理器中添加多达5个自定义指令。

2.5.2 标准CPU选项

Altera公司提供单独的预定义指令来提高软件性能。MUL和MSTEP指令就是与其他硬件一起实现的预定义指令。当用户在SOPC Builder中选择这些CPU选项时,相关逻辑被增加到算术逻辑运算单元(ALU)。例如,如果用户选择执行MUL指令,整数乘法器被自动地添加到CPU的ALU中,并在2个时钟周期内完成16位与16位的乘法操作(相同的操作若用循环的软件程序实现需要80个时钟周期)。

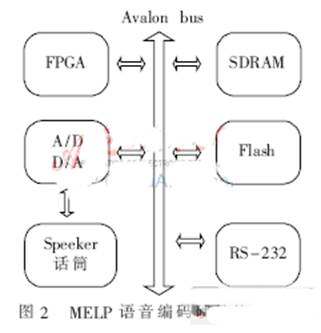

3 MELP语音编码的硬件构成

硬件电路板由Altera公司的FPGA芯片EP2C8作为主控芯片,此外还包括:8 MB容量的SDRAM、2 MB容量的Flash、WM8731音频芯片,自带音频D/A、A/D,为方便调试,另带有串口。MELP语音编码硬件构成如图2所示。

为便于程序的调试,扩充了RS-232串口,可与计算机串口直接互联。8 MB容量的SDRAM可为Nios II软核处理器运行嵌入式操作系统提供所需的存储空间,2 MB容量的Flash也可为MELP的软件编制提供存储空间。WM8731音频芯片提供快速的音频编解码数据码流,并向扬声器传输解码后的数据流。

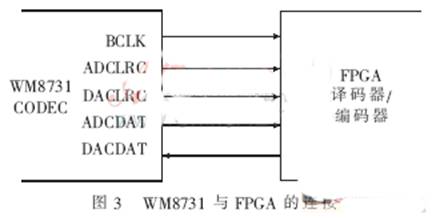

WM8731是一个低功耗的立体声Codec芯片,内部集成了耳机放大功能,因此,WN8731也可以应用于MD、DAT等设备[7];内建了24 bit(multi-bit)Σ-Δ三角模数转换和数模转换,ADC和DAC都使用了超采样数字插值技术;支持数字音频的位数可以是16 bit~32 bit,采样率从8 kHz~96 kHz;立体声音频输出带有数据缓存和数字音量调节,WM8731通过2~3根的串行接口进行控制,可工作于主从模式。在3.3 V信号电压时ADC可以达到90 dB的信噪比,1. 8 V信号电压时ADC可以达到85 dB的信噪比。3.3 V信号电压时的DAC信噪比可以达到100 dB,1.8 V信号电压时DAC信噪比也有95 dB。ADC和DAC的频率响应都在8 kHz~96 kHz之间,可以有选择地使用ADC的高通滤波。一般情况下,WM8731都是在专业声卡领域中使用。

各芯片之间的互联通过引线连接到FPGA的IO脚。Nios II处理器的内部总线通过定义引脚连到IO,这样需要连接到Avavon总线的芯片可通过IO脚连到总线上。图3所示为WM8731CODEC芯片与主芯片FPGA的连接。

串口方面,SDRAM及Flash使用Nios II自带的基于Avalon总线的软IP。

本文讨论了MELP混合线性码激励的FPGA实现的硬件构成,介绍了硬件主要组成芯片及MELP编解码的主要框架,可以用于下一步软件程序的编制。

低码率语音编码MELP声码器的SOPC实现

- 语音编码(9205)

- MELP(9571)

相关推荐

一种很简单的增量调制(DM)编码

本文是该系列的第19篇。语音编码压缩的目的是在尽量不损失信息的情况下降低码率,从而节省存储空间和通信带宽。To Multimedia File这个block就提供几种语音压缩方式:CCITT

2020-12-31 12:17:00 6823

6823

6823

6823DM365 H264编码时怎么控制码率大小?

在dm365平台上,如何设置h264编码器输入参数,以控制h264编码的码率?目前我在运行dvsdk_2_10_00_17\dm365_codecs_01_00_06\packages\ti\sdo

2020-04-17 10:32:21

DM368 低帧率 H.264编码 码率控制问题

专家:

我们使用DM368 编码 1080P30的视频信号。

将rcalgo 设为0,设置定码率模式。

将targetbitrate目标码率设为

2018-06-21 00:16:35

TD-SCDMA中AMR语音编码器的设计方法

TD-SCDMA中AMR-NB的实现。此编码器运用了代数码本线性预测(ACELP)混合编码方式,也就是数字语音信号中既包括若干语音特征参数又包括部分波形编码信息,再运用这些特征信息重新合成语音

2009-07-29 08:30:15

TI DAVINCI的商业级H.264 视频编码器源码供应

/davinciedu.html成都宇鸿科技是一家在TI DAVINCI 平台专注3G和视频编解码算法优化和实现的公司,是国内少数能整体提供嵌入式3G, H.264超低码率编码器,基于VPN的视频联网传输平台的公司之一

2009-12-02 14:10:03

一种符合ITU-T指标要求的嵌入式立体声语音频编码方法

Transform,MLT)编码技术对输入信号的中值与边带信息进行分层编码,形成具有嵌入式结构的码流.编码器可处理宽带和超宽带的立体声信号,宽带立体声信号编码的最大码率为48kb/s,超宽带立体声

2011-03-09 20:25:23

为什么TI8148的h264编码码率总是超过设置的参数?

Hi all,

测试TI8148(DVRRDK4.0)编码效率的时候发现,实际传输的码率最大值普遍超过设置的码率,

低码率下平均值也经常超过设置的码率参数。编码方式使用的H264 HP

2018-05-25 06:07:22

什么是编码效率或码率?

什么是编码效率或码率信道编码的实质是在信息码中增加一定数量的多余码元(称为监督码元),使它们满足一定的约束关系,这样由信息码元和监督码元共同组成一个由信道传输的码字。一旦传输过程中发生错误,则信息

2008-05-30 15:58:22

在SoPC上实现的波形发生器

在SoPC上实现的波形发生器摘要:可编程片上系统(SoPC)设计是一个崭新的、富有生机的嵌入式系统设计方向。嵌入式集成化设计已成为电子领域发展的一个重要方向。Xilinx提供的EDK正是用于创建

2009-06-25 08:12:37

基于TMS320VC5509的基音周期实时检测系统的设计

之一,其描述了语音激励源的一个重要特征。基音周期信息在多个领域具有广泛的应用,如:语音识别、说话人识别、语音分析与综合以及低码率语音编码、发音系统疾病诊断、听觉残障者的语言知道等。传统的基音检测方法有自相关函数法、平均幅度 [hide]全文下载[/hide]

2010-04-22 11:55:46

如何实现低码率语音编码MELP声码器?

语音编码技术在当今数字通信尤其在无线系统中发挥着越来越重要的作用。利用语音编码技术可有效降低信息存储量、提高信道利用率。混合激励线性预测(MELP)语音编码算法能在较低码率下提供较高的语音质量、自然度和清晰度,已成为美国国防部新的2.4 Kb/s的语音编码标准。

2019-08-19 07:34:48

如何采用通用法实现MELP声码器算法?

本文采用通用法实现MELP声码器算法,选择TI公司的TMS320VC5416 DSP芯片作为主处理器,完成声码器的主要功能。

2021-06-07 07:02:50

嵌入式DSP教学实验箱_数字信号处理教程:3-5 AAC音频编码实验

,HE-AAC,HE-AACv2三种主要的编码。其中LC-AAC就是比较传统的AAC,相对而言,主要用于中高码率,HE-AAC主要用于中低码,而新近推出的HE-AACv2主要用于低码率。事实上大部分

2023-09-05 11:02:20

怎么实现基于DSP和SOPC数字信号发生器的设计?

为了比较DSP和SOPC技术在电子设计领域的应用,采用泰勒展开法和DDFS技术,分别给出设计方案的硬件电路结构和软件流程图,并通过集成开发环境CCS和DE2开发板实现正弦信号发生器。结果表明,采用

2021-05-12 06:15:43

怎么实现高速G.729ab声码器的设计?

在纯汇编并行优化的基础上设计了高效的G.729ab声码器;利用TMS320C6203的在片外设McBSP实现了连接PSTN的标准E1接口;设计了用于分组数据收发的RTP协议接口,利用TMS320C6203的HPI接口方式与上层处理器连接,使声码器可灵活应用于媒体网关。

2021-06-03 07:04:33

怎么设计基于DSP的H.264编码器电路?

许多全新的编码技术和网络适配层NAL的概念,从而拥有更高的编码效率和更好的网络适配性。为从低码率的实时通信系统或无线环境到高码率的HDTV和数字存储系统提供一个优良的视频压缩编码通用工具。但H.264

2019-09-04 06:19:09

海思芯片资料,Hi3518A处理器参数说明 精选资料分享

Hi3518A作为新一代HD IP摄像机SOC,集成新一代ISP,优化后的编码前图像处理算法和新一代H.264编码器,同时采用先进低功耗工艺和内部的低功耗架构设计,这一切将使得Hi3518A在低码率

2021-07-23 10:03:28

视频码率很大,请问有没有好方法来控制码率?

运动量很大时,图像的码率会很大,会达到10M左右,视频可能会卡顿或者花屏,CBR与VBR均不能降低码率。请问:有没有好方法来控制码率?谢谢。

2018-05-31 05:31:11

请教关于TMS320DM8148音视频编解码器应用

hi,各位我们想使用TMS320DM8148芯片来作一款音视频编码器,要求如下:1)H.264视频压缩,要求实现低延时,低码率编解码,不知TMS320DM8148低延时的性能怎样,编解码延时要求低于

2018-07-25 06:00:09

采用FPGA和NiosII实现实时H264视频编码器

H.264标准作为新一代视频编码标准,是面向多比特率的视频编码标准,也称JVT/AVC标准,既可用于高码率的HDTV和数字存储系统,也可用于低码率的实时通信系统。在相同的图像质量情况下,H.264比

2019-07-29 06:52:57

基于音频点播平台的保密语音隐秘传输

提出一种基于音频点播系统的保密语音隐秘传输实现方案。采用ITU G.729A编码算法对保密语音低码率压缩编码,将保密语音码流通过改进LSB数据隐藏算法嵌入到公开音频中,利用音频

2009-04-13 09:37:30 12

12

12

12自动语音记录系统(AVRS)的SOPC设计与实现

本文基于Altera 公司的高性能Stratix 器件,利用SOPC Builder、DSP Builder、Matlab 和Simulink等软件设计实现了一种新型的自动语音记录系统(AVRS),实现了对多路电话的通话进行同期监控录

2009-06-06 15:56:09 24

24

24

24在SoPC上实现的波形发生器设计

在SoPC上实现的波形发生器:可编程片上系统(SoPC)设计是一个崭新的、富有生机的嵌入式系统设计方向。嵌入式集成化设计已成为电子领域发展的一个重要方向。Xilinx提供的EDK正

2009-06-25 08:12:54 19

19

19

19TD-SCDMA中AMR语音编码器的实现

语音编码方案的选取对移动通信系统的通话质量、信道容量等有重要影响。本文讨论了TD-SCDMA系统中AMR语音编码的自适应机制,同时分析了AMR中代数码本线性预测(ACELP)算法及实现

2009-07-29 08:27:38 18

18

18

18基于DSP芯片的MELP声码器的算法实现

论文对MELP 编解码算法的原理进行了简要分析,讨论了如何在定点DSP 芯片TMS320VC5416 上实现该算法,并研究了其关键技术,最后对测试结果进行了分析。关键词:MELP;语音编码;

2009-08-06 08:46:47 20

20

20

20SOPC系统建立及uClinux移植实现

本文通过具体实现一个可以运行uClinux 操作系统的最小SOPC 系统,较为完整地介绍了构建SOPC 系统以及构建Nios II 软核处理器的方法及步骤,并详细描述了uCLinux 操作系统在该SOPC 系统

2009-08-13 11:13:24 28

28

28

28基于DSP TMS320DM642的H.264视频编码的实现

阐述了低码率视频编码国际标准H.264的主要内容,重点讨论了H.264编码在DSP TMS320DM642上的实现和优化。关键词: H.264;TM320DM642;代码优化 &

2009-09-11 10:54:02 26

26

26

26基于NiosII的低码率实时H264视频编码器

笔者基于NiosII 设计了一种低码率实时应用的编码系统。该系统充分利用FPGA 的并行设计结构,对视频数据采用高压缩比的H.264 标准编码,能很好地满足低码率实时编码的要求

2009-11-26 15:22:18 35

35

35

35基于SOPC的SPWM电路设计与实现

介绍了一种基于SOPC 的SPWM 波形原理方法,阐明了应用SOPC 的设计思想。叙述了应用该技术产生SPWM 波以及对波形控制的实现过程。该方案具有载波比可调、精度高等优点,实验结果表

2009-11-30 14:10:18 38

38

38

38G.726语音编解码器在SoPC中的实现

在对G.726 语音编解码标准分析的基础上给出了基于FPGA 的DSP 设计流程,利用MATLAB/Simulink、DSP Builder 和SOPC Builder 工具设计了G.726 语音编解码器,通过仿真实验验证了所设计的编解码器模

2009-11-30 14:59:24 12

12

12

12基于单片机软核的SOPC系统设计与实现

基于单片机软核的SOPC系统设计与实现:本文设计就是采用 SOPC 技术,在一块FPGA 芯片上,实现一个水文测报通信系统。该系统是专门为国家防汛指挥系统项目而开发的实时多任务的前

2010-01-16 13:25:35 19

19

19

19EN5930 MPEG-4 AVC SD编码器编码解决方案

在最低码率实现最佳图像质量使运营商能在数字有线、卫星和地面电视网络其可用带宽内通过广播更多的频道——使此宝贵资源的投资回报最大化。对于在xDSL网络上提供电视服务的

2010-07-08 00:46:25 17

17

17

17G.726语音编解码器在SoPC中的实现

在对G.726语音编解码标准分析的基础上给出了基于FPGA的DSP设计流程,利用MATLAB/Simulink、DSP Builder和SOPC Builder工具设计了G.726语音编解码器,通过仿真实验验证了所设计的编解码器模型

2010-07-16 15:06:52 18

18

18

18GSM手机基本原理

语音编码一语音编码采用波形编码和声码器合一的混合编码器。语音编码器全称为规则脉冲激励一长期预测编码器一, 其中为波形编码器, 为声码器, 两者输出经复用后

2010-10-30 16:20:25 217

217

217

217低码率语音编码MELP的SOPC实现

讨论了低码率语音编码MELP的编解码过程,有效降低了语音编码码率并能使说话者个人语音特征减弱,特别适合需要弱化说话者语音特点的场合。给出了其FPGA的硬件实现框图,据此

2010-12-01 16:57:14 33

33

33

33混合激励线性预测低速率语音编码研究

为了满足数字通信及其他商业应用的需求,语音压缩编码技术得到迅速发展。近年来主流的低速率语音编码方案主要基于LPC-10,混合激励线性预测(MELP),多带激励编码(MBE),正弦

2011-01-04 10:20:37 16

16

16

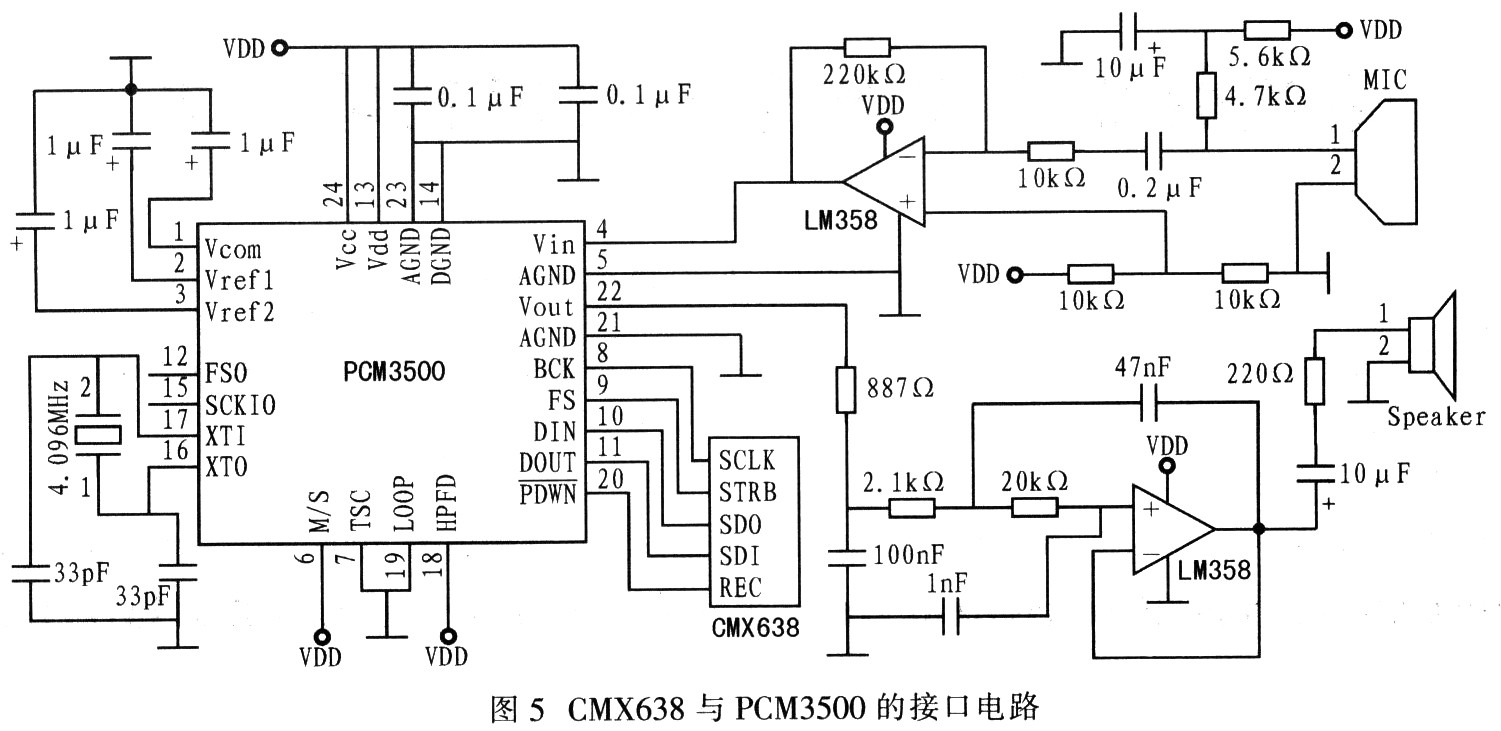

16CMX638新型声码器的应用设计

CMX638新型声码器的应用设计

语音编解码技术的迅速发展,使中低速率语音编码技术广泛应用于现代移动通信。初期的脉冲编码调

2009-07-06 18:55:43 1144

1144

1144

1144

一种输出格式可控的多码率LDPC编码器实现

一种输出格式可控的多码率LDPC编码器实现

0 引 言

目前,LDPC码已广泛应用于深空通信、光纤通信、数字音视频广播等领域。由于有着较Turbo码更优秀的性能,

2009-11-25 09:56:43 1379

1379

1379

1379采用DSP芯片的MELP声码器的算法设计方案

采用DSP芯片的MELP声码器的算法设计方案

摘要:论文对MELP编解码算法的原理进行了简要分析,讨论了如何在定点DSP芯片MS320VC5416上实现该算法,

2010-03-06 14:20:11 1207

1207

1207

1207

G.723.1算法在DSP上的优化

G.723.1算法在DSP上的优化

1 引言

G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标

2010-04-12 15:19:35 721

721

721

721语音编解码算法G.723.1在DSP上的优化

1 引言G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。G.723.1主要用于对语音及其它多媒体声音信

2010-06-03 09:23:41 705

705

705

705分绍了G.723.1标准的DSP代码优化

G.723.1是删组织于 1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。

G.723.1主要用于对语音及其它多媒体声音信号的

2010-07-02 09:06:57 946

946

946

946AMBE-2000TM语音压缩编码电路分析

1 引言语音压缩编码技术一直是在尽可能低的数码率下获得尽可能好的合成语音质量的矛盾中发展的。数码率实质上反映的是频带宽度,降低数码率实质上就是压缩频带宽

2010-07-06 09:27:31 2396

2396

2396

2396

基于语音合成芯片MSP50C30和MELP的电子语音导游机

1 前言

TI公司新近推出的语音合成芯片MSP50C30并采和MELP语音压缩算法,通过外接64M位存储器对语音信号进行了压缩存储和合成。经过这样处理合成后的语音音质良好,放

2010-09-03 17:32:39 1001

1001

1001

1001

AMBE-1000声码器芯片在语音通信系统中的应用

AMBE-1000是美国DVSI公司研制、Lucent公司生产的一款成熟的双工声码器芯片。该芯片采用AMBE语音编码算法,编码

2010-10-26 11:38:19 4900

4900

4900

4900

MELP语音编码的FPGA实现的系统框架

本文讨论了MELP混合线性码激励的FPGA实现的硬件构成,介绍了硬件主要组成芯片及MELP编解码的主要框架,可以用于下一步软件程序的编制。

2011-12-29 09:38:13 1089

1089

1089

1089

基于SoPC系统的红外解码IP核的设计与实现方法研究

电子发烧友网核心提示:本文主要介绍了红外解码IP核在SoPC系统中的设计与实现方法,重点研究红外系统的数据编码和传输机制、红外解码电路的HDL设计、IP核的制作及在SoPC系统中的应

2012-11-30 10:56:40 2010

2010

2010

2010MELP声码器的算法设计方案

1 引言 1996年3月,美国政府数字语音处理协会(DDVPC)选择了2.4kbps混合激励线性预测(MELP)语音编码器作为窄带保密语音编码的产品以及各种应用的新标准由于MELP具有良好的音质

2017-10-24 10:59:25 2

2

2

2基于DSP的语音编解码算法G.723.1优化分析

1 引言 G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。G.723.1主要用于对语音及其它多媒体声音信号的压缩,目前

2017-10-25 11:13:56 0

0

0

0适用于多种声码器算法调制方法

类语音调制的目的是将输入数据比特流调制成具有类似语音的波形信号,以便于在话音通道上传输,实现数据抗声码器压缩传输。,本文针对话音通道端到端的数据通信,提出了一种适用于多种声码器算法的类语音调制算法

2017-10-30 17:36:07 5

5

5

5混合激励线性预测(MELP)声码器算法的原理解析

1 引言 1996年3月,美国政府数字语音处理协会(DDVPC)选择了2.4kbps混合激励线性预测(MELP)语音编码器作为窄带保密语音编码的产品以及各种应用的新标准由于MELP具有良好的音质

2017-11-01 15:44:00 3

3

3

3语音编解码算法G.723.1在DSP上的优化

1 引言 G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。G.723.1主要用于对语音及其它多媒体声音信号的压缩,目前

2017-11-01 16:03:40 0

0

0

0混合激励线性预测(MELP)声码器算法解析

1 引言 美国政府数字语音处理协会(DDVPC)选择了2.4kbps混合激励线性预测(MELP)语音编码器作为窄带保密语音编码的产品以及各种应用的新标准由于MELP具有良好的音质、极低的码率,以及

2017-11-02 10:21:40 1

1

1

1采用通用法实现MELP声码器算法

1 引言 1996年3月,美国政府数字语音处理协会(DDVPC)选择了2.4kbps混合激励线性预测(MELP)语音编码器作为窄带保密语音编码的产品以及各种应用的新标准由于MELP具有良好的音质

2017-11-02 10:51:16 4

4

4

4基于PRBS的8B/10B编码器误码率为0设计

基于减少8B/10B编码器占用的逻辑资源和保证该编码器误码率为0的目的,采用查表法和组合逻辑实现相结合的方法设计实现了符合嵌入式互连规范Rapidl0协议的8B/10B编码器,通过伪随机二进制序列

2017-11-06 17:04:21 7

7

7

7H.265/HEVC码率控制优化算法

在视频通信中,视频压缩效率和编码视频质量,以及传输带宽与编码码率的适配性始终是研究者们最关注的问题。为了解决这一问题,在目前的主流视频编码标准H.264/AVC( Advanced Video

2017-12-09 11:18:36 0

0

0

0多带激励语音编码SA5.0C-BPDF资料的实现

直在努力通过降低语音编码速率来扩大通信系统的容量。在我国,对低速率语音编码技术也有迫切的需要,如保密通信、短波信道、水声信道等对码率要求严格的应用场合。但现有语音编码的国际标准传输速率都较高(一般

2018-06-01 13:37:00 1197

1197

1197

1197

利用FPGA的并行设计结构实现低码率实时应用H.264标准编码系统设计

H.264标准作为新一代视频编码标准,是面向多比特率的视频编码标准,也称JVT/AVC标准,既可用于高码率的HDTV和数字存储系统,也可用于低码率的实时通信系统。在相同的图像质量情况下,H.264比H.263和MPEG一4可以节省20%~50%的码率。

2018-11-19 09:40:00 2141

2141

2141

2141

高速G.729ab声码器设计及其在媒体网关中的应用

关键词:媒体网关 , 声码器 在VoIP媒体网关设备中,语音压缩编码是其关键技术之一。在ITU-T发布的应用于VoIP的语音压缩编解码标准中,G.729是应用较为广泛的一种。G.729采用“共轭结构

2018-12-02 18:30:01 308

308

308

3081000声码器在语音通信系统中的应用

关键词:AMBE-1000 , 声码器 , 语音通信 AMBE-1000是美国DVSI公司研制、Lucent公司生产的一款成熟的双工声码器芯片。该芯片采用AMBE语音编码算法,编码速率为2.4

2018-12-17 14:45:01 294

294

294

294基于NiosII的低码率实时H.264视频编码器

关键词:NiosII , 视频编码 引言 H.264标准作为新一代视频编码标准,是面向多比特率的视频编码标准,也称JVT/AVC标准,既可用于高码率的HDTV和数字存储系统,也可用于低码率的实时通信

2019-02-27 07:04:01 338

338

338

338

AP280语音编解码芯片的数据手册免费下载

AP280是深圳市硅传科技有限公司(以下简称硅传)自主研发的一款低码率(2.0kbps~8.0kbps)语音编解码芯片。该芯片采用多带激励的方法,在编码时首先对语音进行分帧处理,每帧时长20ms

2019-08-21 08:00:00 11

11

11

11AP680语音编解码芯片的数据手册免费下载

AP680 是深圳市硅传科技有限公司(以下简称硅传)自主研发的一款极低码率(2400bps/600bps)语音编解码芯片。该芯片采用多带激励的方法,在编码时首先对语音进行分帧处理,每帧时长

2019-12-11 08:00:00 4

4

4

4关于SqueezeWave声码器的改进措施

自动语音合成对于众多智能应用十分重要,其中声学特征转换为音频输出的声码器在语音合成过程中具有十分重要的作用。虽然WaveGlow可以实现并行化的语音合成,但其庞大的计算量使得本地和边缘设备无法承受,基于云计算的语音合成使得网络延时和用户隐私问题无法有效解决。

2020-08-07 11:42:24 460

460

460

460

采用数字信号处理器实现G.729语音编解码系统的优化设计

,提出了一些非常有效的处理方法,如混合编码。这种算法克服了原有波形编码器与声码器的弱点,而结合了它们各自的长处,在4kb/s~16kb/s速率上能够得到高质量合成语音,而在本质上也具有波形编码的优点

2020-09-07 10:03:00 773

773

773

773

基于32位浮点DSP芯片TMS320C6713实现语音编解码系统的设计

本系统使用TI公司浮点型DSP TMS320C6713实现G.723.1等语音编解码,为G.723.1、G.729等常用的低码率语音压缩标准提供运行及测试硬件平台。有别于大多数编解码系统,本设计采用

2020-09-21 09:58:07 3122

3122

3122

3122

使用FPGA实现MELP语音压缩编码器的详细资料说明

基于CPU软核模块算法IP的方法对一个1.6Kb/s类MELP语音压缩编码算法进行了实现,并将整个语音压缩编码器在FPGA上进行了整体验证,实验结果说明本文给出的语音压缩编码器的实现结构是可行

2021-01-22 15:08:38 17

17

17

17如何使用moviepy来分割音频流并降低码率

本文主要介绍如何使用moviepy来 分割音频流并降低码率 。 1.准备 开始之前,你要确保Python和pip已经成功安装在电脑上,如果没有,可以访问这篇文章: 超详细Python安装指南 进行

2023-10-16 11:19:56 342

342

342

342AVS3P10实时语音编码标准获得重要进展

传统的语音编码器,包括AVS、ITU-T等标准语音编码器,在16-20kbps左右码率时,能够恢复出高质量宽带语音;在30-35kbps,可以恢复出高质量超宽带甚至全带语音。然而,当码率进一步降低(如:降到10kbps以下时),传统语音编码器恢复的质量下降明显,影响用户体验。

2023-12-20 10:02:52 230

230

230

230

为什么监控设备会有主码率和子码率之分呢?

为什么监控设备会有主码率和子码率之分呢? 监控设备主码率和子码率的区分是为了满足不同监控场景下的需求和性能要求。主码率和子码率之间的差异主要体现在编码质量、带宽占用、存储空间和图像细节等方面。 首先

2024-01-09 11:35:36 183

183

183

183 电子发烧友App

电子发烧友App

评论