KC-201为FM立体声收音模块,配合单片机最小系统电路或本公司单片机实验板够完成 88MHz--108MHz频率的调频广播接收。模块采用TEA5767/CL5767 专用FM芯片,接收稳定可靠。板载TDA2822功放电路,同时有左右声道音量调节电位器。

模块主要参数和特点:

A、采用通用的102BC模块的封装。

B、兼容TEA5767及CL3767软、硬件(软件搜索使用IF中频功率判断方式,如原机型使用立体声判断方式的只需少做软件改动即可)。

C、灵敏度高、噪声小、搞干扰能力强、外接元件极少、使用极其简单,板子尺寸为 47mm*48mm 。

D、I2C串行数据总线接口通讯。

E、采用先进的SEEK硬件搜台方式,全频段搜索只需4~5Sec,在幅提高搜台速度。

F、内置LDO调整、低功耗、超宽电压使用范围(2.7~5.5VDC)。

G、内置噪声消除、软静音、低音增强电路设计。

H、FM及MPX立体声采用DSP处理器。

I、应用简便、成本低,性价比高。

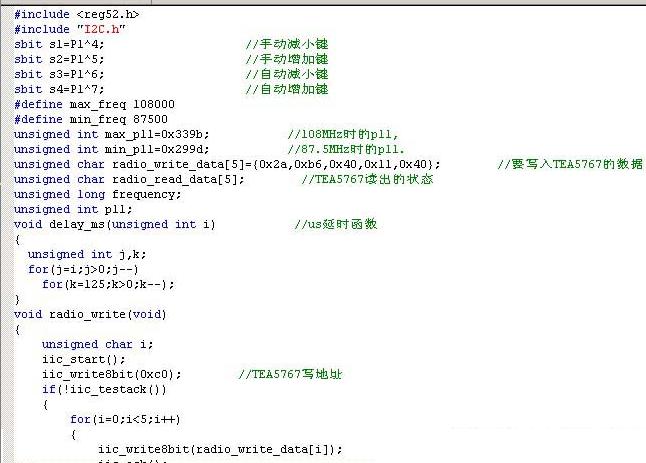

KC-201 FM立体声收音模块接口说明:

模块左侧“J1”是与单片机连接的IIC总线接口,分别为:SDA(数据)、CLK(时钟)、GND(地)、VCC(电源)

模块右侧“J3”是音频输出口:R+(右声道输出线+)、R-(右声道输出线-)、L+(左声道输出线+)、L-(左声道输出线-)

模块左下侧“J2”为外置耳机插孔,插上耳机后,左右声道音频输出自动切换到耳机上,拔掉耳机后,左右声道输出自动切换到J3输出端。

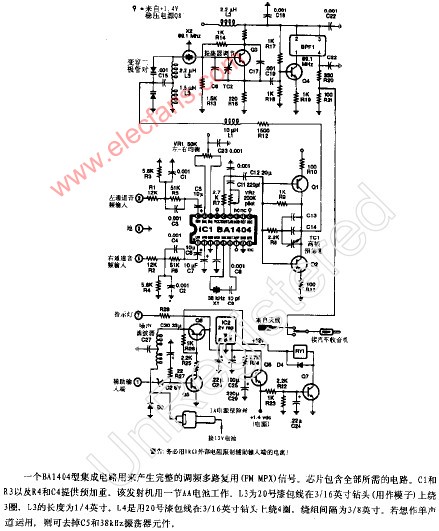

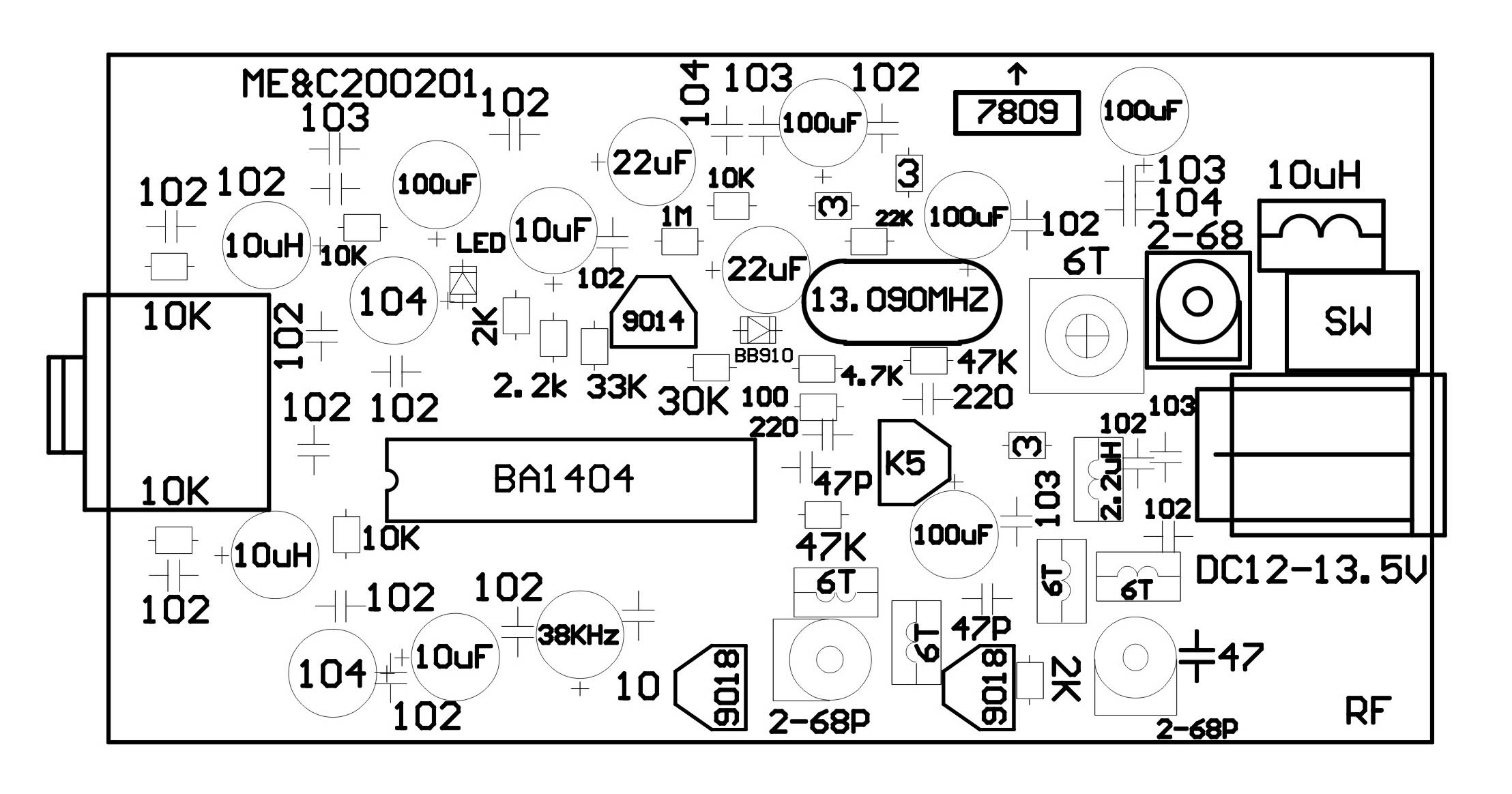

以下是我们在完成FM收音模块开发中使用分立元件搭焊的试验过程:

我们用5767收音模块通过搭焊与实验板相连,做成了整个收音实验,TDA5767和CL5767的指令完全兼容,可以直接代换。其实TEA5767的控制也不算很难,只要看懂了TEA5767.pdf(这个在我们的网站上可以下载到),然后用C51就可以控制它,实现FM收音功能。下面就来谈谈TEA5767的编程思路,希望对有兴趣弄这个芯片的朋友有些帮助。

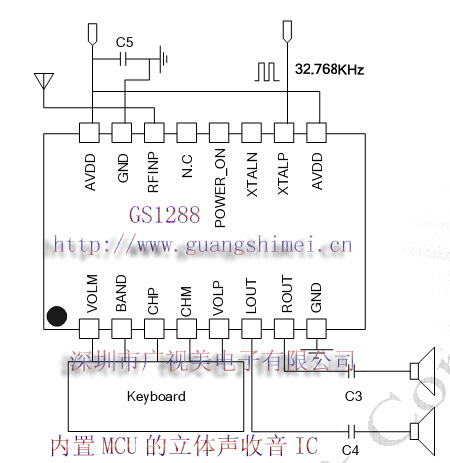

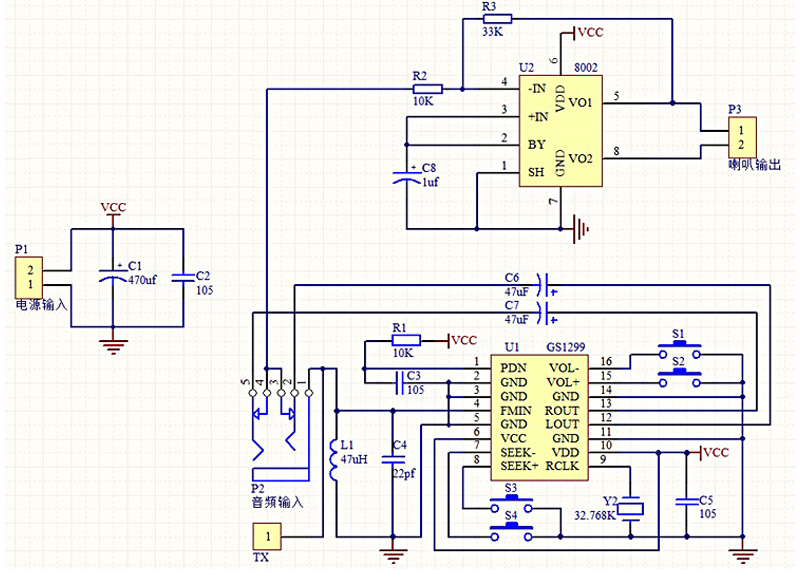

(1)首先选择好你硬件的晶振,这在输入模式的相应位设置,只有两种晶体选择!一种是32.768KHz,一种是13MHz。通过字节4的XTAL可以控制:当XTAL=1时,用的是32.768KH,而当XTAL=0时,用的是13MHz。当然大家应该要清楚,这个晶振外接的哦。

(2)选择好收音的制式,有日本和欧洲两种模式,其频率覆盖范围不同。

(3)将输出模式选择立体声,不要使能全体静音和左右静音。这个可以通过字节3控制,具体请看TEA5767.pdf。

(4)其它几个音效控制位可以不理会!如HCC,SNC。其实,我初始化是将date[2]=0x20, date[3]=0x11, date[4]=0x00,当然具体的还得看你的硬件部分这么接的拉。

(5)有两个扩展输出端口,可以做指示和其他控制,但是PORT1可以兼职做内部状态指示,由SI控制。

下面我们来分享一下试验全过程,我们使用搭焊的方式来完成,因为外围电路很简单,只要接上天线、电源和音频输出就可以了:

]

]

[page_break]

KC-201 FM立体声收音模块 元件分布说明:

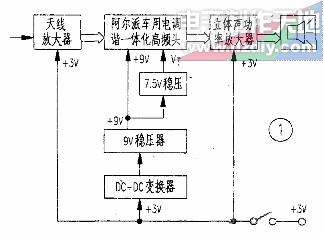

模块相关背景知识介绍:

FM模块知识:

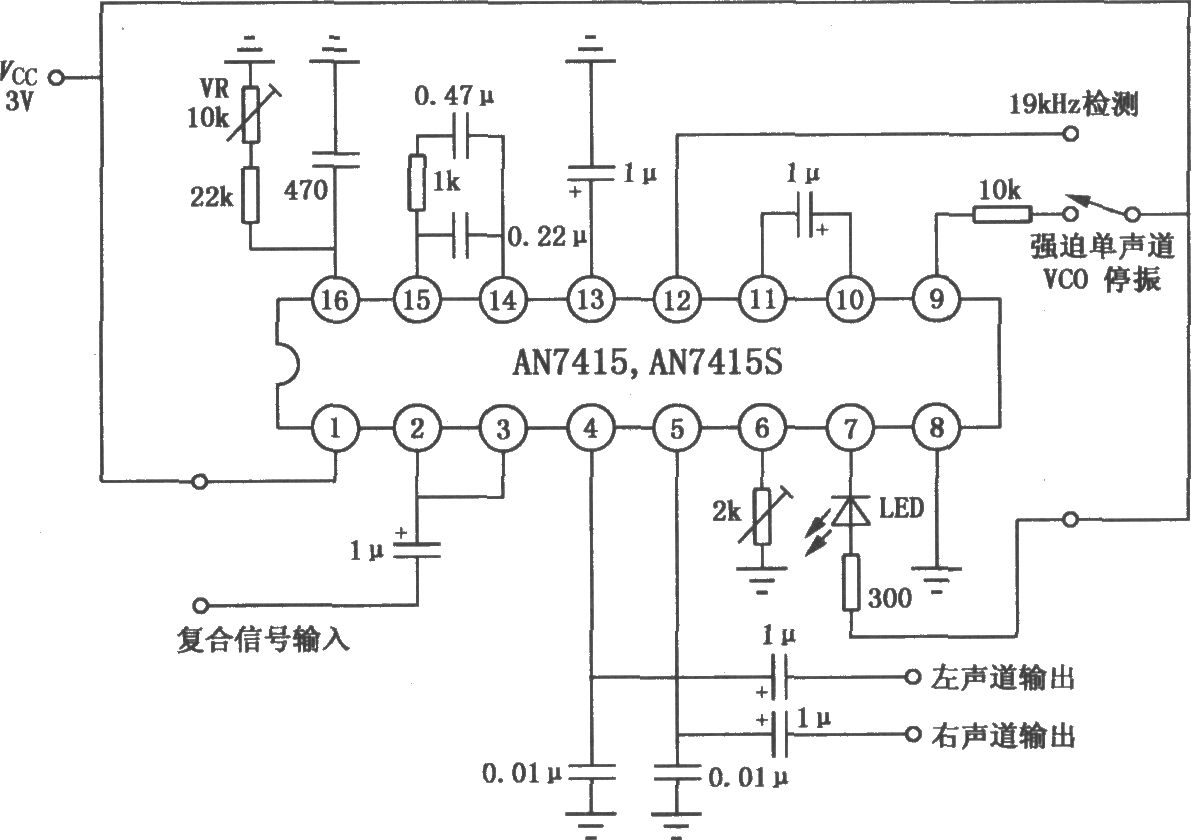

CL3767是一片低功耗电调谐调频立体声收音机电路,其内部集成了中频选频和解调网络,可以做到完全免调,因此只需要很少量的小体积外围元件。CL3767HN可以应用在欧洲、美国和日本不同的FM波段环境。该产品具有如下特点:

高灵敏度(使用低噪声射频输入放大器)

兼容美国/欧洲(87.5 to 108 MHz)和日本(76 to 91MHz)调频波段

预调谐接收日本电视伴音至108 MHz

高放自动增益控制(AGC)电路

LC调谐振荡用低成本固定芯片

调频中频选择在内部完成,中频免调

三种振荡基准频率输入32.768K、13M、6.5M

锁相环调谐系统

由总线模式管脚来选择I2C总线模式或三线模式

由总线输出7位中频计数,由总线输出4位电平

软静音,立体声消噪(SNC),高电平切割(HCC)

软静音,立体声消噪(SNC),高电平切割(HCC)能通过总线关断

免调谐立体声解码器,自动搜索调谐功能

待机模式

两个软件可编程端口,总线输入,输出线三态模式

自动调节温度范围(在VCCA, VCC(VCO) 和VCCD = 5 V)

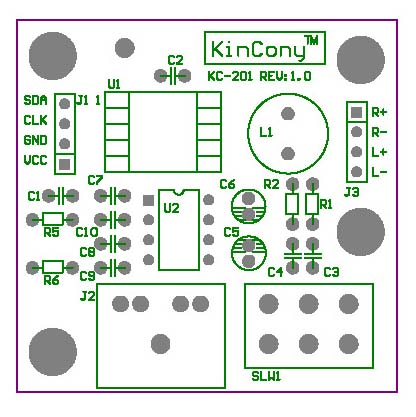

软件编程说明:

(1)I2C-总线说明

I2C 总线是通过二根I2C 总线是通过二根线(串行数据线和串行时钟线)来连接器件之间通信的总线,并根据地址识别每个器件。启动总线后的第一个字节的高七位是从器件的寻址地址。

IC 的地址为C0:1100000 。

I2C 总线的逻辑结构:收发机。

最低位未使用。

最大低电平和最小高电平分别限定在0.2VCCD和0.45VCCD。

总线模式(BUSMODE)引脚必须接地时工作在I2C-总线模式

注:总线工作在最大时钟频率为400KHz,不能连接IC到一个正工作在高时钟的总线上。

(2): 数据传输数据顺序:地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。地址最

低位为“0”,表示写操作到CL5767。 每个字节的第七位被认为是最高位,并作为字节的第一位传送。 在时钟的下降沿,数据变为有效信号。在每一字节后面的停止信号可以缩短传送时间。

在整个传输完成之前发送一个停止条件: 保留的字节将包含以前的信息。 如果一个字没有传送完,新的字节将被使用,但新的调谐周期不会开始。 通过standby位设置,芯片可以工作在省电的待机模式;总线仍然激活。屏蔽总线界面可以减小待机电流。如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离总线。软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(3):上电复位在上电复位时,静音位置“1”,其他所有位置“0”。为了初始化集成块所有位必须重新设定。

(4): I2C-总线协议表1:写模式 ![]()

注意:1:S 为启动条件。

- 2:A 为应答信号。

- 3:P 为停止条件。

表2:读模式 ![]()

注意:1:S 为启动条件。

2:A 为应答信号。表3:IC 地址位

|

|

|

|

IC 地址 |

|

|

模式 | |

|

1 |

1 |

0 |

|

0 |

0 |

0 |

R/W |

注:1:读或者写模式

a) 0 对CL5767 写操作。

b) 1 对CL5767 读操作。

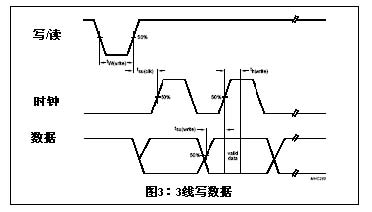

(5): 3-线说明3-线控制:写/读,时钟和数据线;工作在最大时钟频率为1MHz。提示:通过standby位设置,芯片可以工作在省电的待机模式。在待机模式下芯片必须设置在写模式。在待机期间,当芯片设置为读模式时,芯片会保持数据。屏蔽总线界面可以减小待机电流。如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离时钟和数据线。

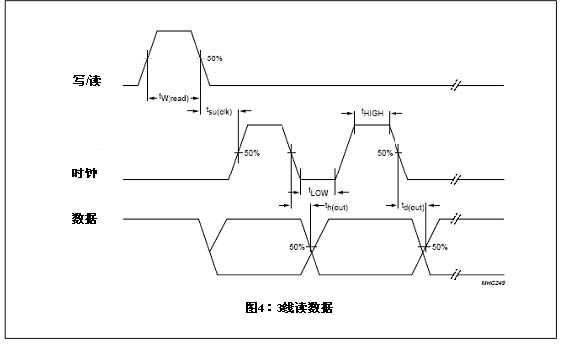

(6):数据传输数据顺序:地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。 在写/读控制的上升沿可以写数据到芯片。在时钟的上升沿之前,数据必须为有效信号。当时钟为低时可改变数据信号,在时钟的上升沿时数据被写入芯片。在以开始二字节或每个字节之后,如果有新的开始信号,数据传输被停止。 在写/读控制的下降沿可以从芯片读数据。当时钟为低时,写/读控制改变。在写/读控制的下降沿数据端出现第一个字节的最大有效位。在时钟下降沿移存数据,在上升沿读数据。要实现两个连续的读或写操作,写/读必须固定在最少一个时钟周期。当一个搜索调谐请求被发送时,芯片将自动开始搜索,搜索方向和搜索停止电平可以设置。当搜到一个强度等于或大于停止电平时,调谐系统停止且准备好标志位为高。在搜索期间,当一个制式已经符合时,调谐系统停止且制式标志位为高。在这种情况下准备好标志位也为高。 软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(7): 上电复位在上电复位时,静音位置“1”,其他所有位任意设置。为了初始化集成块所有位必须重新设定。

(8):写数据

表4:写模式 ![]()

表5 数据字节1 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

MUTE |

SM |

PLL13 |

PLL12 |

PLL11 |

PLL10 |

PLL9 |

PLL8 |

表6 数据字节1 的各个位描述

位号 |

符号 |

描述 |

|

7 |

MUTE |

如果MUTE=1,则左右声道被静音;MUTE=0,左右声道正常工作。 |

|

6 |

SM |

如果SM=1,则处于搜索模式;SM=0,不处于搜索模式。 |

|

5 到0 |

PLL[13:8] |

设定用于搜索和预设的可编程频率合成器。 |

表7 数据字节2 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

PLL7 |

PLL6 |

PLL5 |

PLL4 |

PLL3 |

PLL2 |

PLL1 |

PLL0 |

表8 数据字节2 的各个位描述 ![]()

表9 数据字节3 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

SUD |

SSL1 |

SSL0 |

HLSI |

MS |

ML |

MR |

SWP1 |

表10 数据字节3 的各个位描述

位号 |

符号 |

描述 |

|

7 |

SUD |

SUD=1,增加频率搜索;SUD=0,减小频率搜索。 |

|

6 和5 |

SLL[1:0] |

搜索停止标准:见下表1。 |

|

4 |

HLSI |

高/低充电电流切换:HLSI=1,高充电电流; HLSI=0,低充电电流。 |

|

3 |

MS |

立体声/单声道:MS=1,单声道;MS=0,立体声。 |

|

2 |

ML |

左声道静音:ML=1,左声道静音并置立体声,ML=0,左声道正常。 |

|

1 |

MR |

右声道静音:MR=1,右声道静音并置立体声,MR=0,右声道正常。 |

|

0 |

SWP1 |

软件可编程端口1:SWP1=1,端口1 高电平;SWP1=0 ,端口1 低电平。 |

表11:搜索停止标准设定

SSL1 |

SSL2 |

搜索停止标准 |

|

0 |

0 |

在搜索模式下禁止 |

|

0 |

1 |

低:ADC 输出大小为5 |

|

1 |

0 |

中:ADC 输出大小为7 |

|

1 |

1 |

高:ADC 输出大小为10 |

表12:数据字节4 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

SWP2 |

STBY |

BL |

XTAL |

SMUTE |

HCC |

SNC |

SI |

表13:数据字节4 的各个位描述

位号 |

符号 |

描述 |

|

7 |

SWP2 |

软件可编程端口2:SWP2=1,端口2 高电平;SWP2=0,端口2 低电平。 |

|

6 |

STBY |

等待:STBY=1,处于待机模式,STBY=0,退出待机模式。 |

|

5 |

BL |

波段制式:BL=1,日本调频制式;BL=0,美国/欧洲调频制式。 |

|

4 |

XTAL |

如果XTAL=1 ,那么fxtal=32.768KHz; 如果XTAL=0 ,那么fxtal=13MHz。 |

|

3 |

SMUTE |

软件静音:SMUTE=1,软静音打开;SMUTE=0,软静音关闭。 |

|

2 |

HCC |

白电平切割:HCC=1,高电平切割打开,HCC=0,高电平切割关闭。 |

|

1 |

SNC |

立体声噪声去除:如果SNC=1,立体声消噪除打开,如果SNC=0,立体声消噪除关闭。 |

|

0 |

SI |

搜索标志位:SI=1,SWPORT1 输出准备好信号;SI=0,SWPORT1 作为软件可编程端口1 用。 |

表14:数据字节5 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

PLLREF |

DTC |

|

|

|

|

|

表15:数据字节5 的各个位描述

位号 |

符号 |

描述 |

|

7 |

PLLREF |

若PLLREF=1,6.5MHz 的锁相环参考频率启用;若PLLREF=0,6.5MHz 的锁相环参考频率关闭。 |

|

6 |

DTC |

若DTC=1,去加重时间常数为75us; 若DTC=0,去加重时间常数为50us。 |

|

5 到0 |

|

未用,状态不必考虑。 |

(9):读数据

表16:读模式表17:数据字节1 的格式 ![]()

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

BLF |

PLL13 |

PLL12 |

PLL11 |

PLL10 |

PLL9 |

PLL8 |

表18:数据字节1 的各个位描述

位号 |

符号 |

描述 |

|

7 |

RF |

准备好标志:RF=1, 有一个频道被搜到或者一个制式已经符合;RF=0, 没有频道被搜到。 |

|

6 |

BLF |

波段制式:BLF=1,一个制式已经符合;BLF=0,没有制式已经符合。 |

|

5 到0 |

PLL[13:8] |

用于搜索和预设后的可编程频率合成器设定结果。 |

表19:数据字节2 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

PLL7 |

PLL6 |

PLL5 |

PLL4 |

PLL3 |

PLL2 |

PLL1 |

PLL0 |

表20:数据字节2 的各个位描述 ![]()

表21:数据字节3 的格式

|

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

STEREO |

IF6 |

IF5 |

IF4 |

IF3 |

IF2 |

IF1 |

IF0 |

表22:数据字节3 的各个位描述

位号 |

符号 |

描述 |

|

7 |

STEREO |

立体声标志位:STEREO=1,立体声接收;STEREO=0,单声道接收。 |

|

6 到0 |

IF[6:0] |

中频计数器结果。 |

表23:数据字节4 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

LEV3 |

LEV2 |

LEV1 |

LEV0 |

CI3 |

CI2 |

CI1 |

0 |

表24:数据字节4 的各个位描述

位号 |

符号 |

描述 |

|

7 到4 |

LEV[3:0] |

ADC 的输出。 |

|

3 到1 |

CI[3:1] |

芯片验证号。 |

|

0 |

|

该位内部置0。 |

表25:数据字节5 的格式

位7(高位) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0(低位) |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

表26:数据字节5 的各个位描述 ![]()

(10): 总线传输时间表27:数字电平和传输时间

符号 |

参数 |

条件 |

最小值 |

最大值 |

单位 |

|

数字输入 |

|

|

|

|

|

|

VIH |

输入高电平 |

|

0.45VCCD |

V | |

|

VIL |

输入低电平 |

|

0.2VCCD |

V | |

|

数字输出 |

|

|

|

|

|

|

Isink(L) |

低电平吸收电流 |

|

500 |

μA | |

|

VOL |

低电平输出电压 |

IOL = 500 μA |

450 |

mV | |

|

传输时间 |

|

|

|

|

|

|

fclk |

时钟输入频率 |

I2C总线 |

400 |

kHz | |

|

3-线 |

1 |

MHz | |||

|

tHIGH |

时钟高电平时间 |

I2C总线 |

1 |

μs | |

|

3-线 |

300 |

ns | |||

|

tLOW |

时钟低电平时间 |

I2C总线 |

1 |

μs | |

|

3-线 |

300 |

ns | |||

|

tW(write) |

写操作脉冲宽度 |

3-线 |

1 |

μs | |

|

tW(read) |

读操作脉冲宽度 |

3-线 |

1 |

μs | |

|

tsu(clk) |

时钟建立时间 |

3-线 |

300 |

ns | |

|

th(out) |

读操作数据输出控制时间 |

3-线 |

10 |

ns | |

|

td(out) |

读操作输出延迟时间 |

3-线 |

100 |

ns | |

|

tsu(write) |

写操作建立时间 |

3-线 |

100 |

ns | |

|

th(write) |

写操作控制时间 |

3-线 |

100 |

ns |

电子发烧友App

电子发烧友App

评论