如果要将其录音以数字形式的数据保存,则应将其模拟录音信号变换成数字形式的数据,这就给原始数据的保存带来诸多不便。因此,笔者按G.723标准设计了一种数字录音机,它以ADSP-2181作为语音处理器和系统控制器,取消了普通录音机的机械部分和磁带,以大容量的闪速存储器(Flash RAM)作为数字语音数据存储器。该样机体积很小,录音时间长,没有机械噪声及机械故障,很有实用价值。

1 G.723标准简介和系统结构框图

1.1 G.723标准简介

G.723是ITU-T在1996年制订成型的一种多媒体语音编解码标准。其典型应用包括IP电话服务、H.324视频电话、无线电话、数字卫星系统、数电倍增设备(DCME)、公共交换电话网(PSTN)、ISDN及各种多媒体语音信息产品。G.723标准传输码率有5.3kb/s和6.3kb/s两种,在编程过程中可随时切换。该标准主要包含了编码算法和解码算法。原理是:从采集的语音信号中解析出声道模型参数,构造一个合成滤波器,采用合适的激励源激励,编码传输的参数主要是激励源与合成滤波器的参数。5.3kb/s的编码器采用代数码线预测激励(ACELP);6.3kb/s的编码器则采用多脉冲最大似然量化(MP-MLQ)激励。根据传输编码参数,可重构激励源与合成滤波器进行解码,还原出来的数字语音信号经D/A转换器转换成模拟语音信号。关于G.723的编码和解码的详细说明见参考文献[2]。

G.723算法对语音信号有很好的编解码效果,同时也可处理音乐和其它声音信号,典型输入是64kb/s(8k%26;#215;8)或128kb/s(8k%26;#215;16)的A律或μ律的PCM采样语音信号。每次处理一帧语音信号,每帧240个采样点(30ms)。在5.3kb/s的码率下,每帧语音被压缩成20个字节传输;在6.3kb/s的码率下,每帧语音被压缩成24个字节传输。

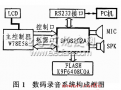

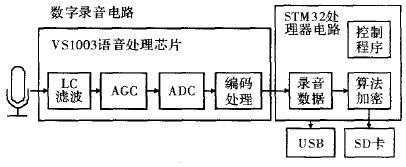

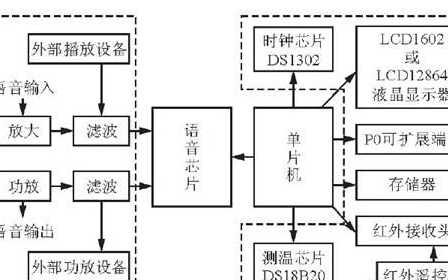

1.2 数字录音系统的结构框图

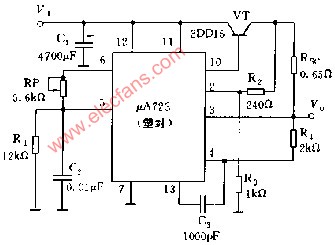

系统框图主要由图1所示的五部分组成。

AD73311用来进行A/D和D/A转换,它集成了模/数和数/模转换功能,而且可编程控制,使用极其方便;ADSP-2181为系统的核心数字处理器[3],时钟频率为33MHz,其功能强大;KM29N32000为闪速存储器(Flash RAM),用来存储已压缩的语音数据;AT27C010(EPROM)用来存放控制ADSP-2181工作的程序;LCD用来显示系统当前的工作状态。系统的工作流程是:模拟语音信号经AD73311采样并经A律或μ律压缩后转换成PCM数据,通过ADSP-2181的串行口送到ADSP-2181,ADSP-2181再将数据进行编码和压缩后送到闪速存储器KM29N32000中存储起来;录音回放时,从KM29N32000读取压缩数据,送回ADSP-2181进行解码,再送到AD73311进行D/A转换,输出模拟语音信号。整个过程都是由存放在AT27C010中的DSP程序控制,有条不絮地工作。LCD显示系统当前的工作状态。

2 系统各主要部分的原理与接口

2.1 AD73311与ADSP-2181的接口电路及编程控制

2.1.1 AD73311与ADSP-2181的接口电路

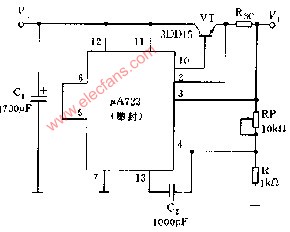

AD73311具有A/D和D/A转换功能,采样频率为8kHz~64kHz,可以编程控制,采样字长为16位。AD73311具有大信噪比、输入输出增益可编程控制、低工作电压(2.7~5.5V),并且一片两用的特点,是一种很受欢迎的芯片。AD73311与ADSP-2181的接口电路如图2所示。 AD73311完成模拟语音信号的采集和数字语音信号的回放工作。从图2中看出,信号从VIN处输入,在VOUT处输出回放语音信号。VIN处接麦克风,VOUT处接扬声器。与ADSP-2181的通信通过串口进行,从SDO引脚向ADSP-2181输出数据,从SDI引脚接收ADSP-2181数据,发送和接收可同时进行。时钟信号由ADSP-2181的SLCK引脚接入。编程时必须先初始化AD73311的工作状态,依次设定采样率、输入输出增益、提前时间等,再让其工作在数据传输模式下就可正常工作。AD73311进入数据传输模式后一直进行A/D或D/A转换。在编程控制中,应让ADSP-2181的串口一直工作在接收中断方式,这样可使数据发送与接收的速率保持一致。要改变工作模式可将其RESET引脚置低,再置高,这样就可重新设定了。

2.1.2 AD73311的编程

AD73311是一种可编程的数据转换器,内含五个8位控制寄存器CRA~CRE,用于设定工作状态,控制输入输出。AD73311通过串行口与处理器接口,传送的是16位数据,有五种工作模式,分别为:程序模式、数据模式、混合模式、模拟环路模式、数字环路模式。其中前三种是正常的工作模式,后两种是调试模式,仅在调试时使用。五种工作模式由内部的控制寄存器A中的四位(CRA0~3)控制。

程序模式:AD73311启动或重置后即工作于程序模式,此时AD73311串行口输入的数据将作为命令字以初始化内部控制寄存器组,之后AD73311根据初始化命令字进入相应的工作模式,在此之前AD73311串行口输出的码字是无效的。数据模式:此时AD73311串行口输出的是A/D转换的16位数据,输入的是D/A转换的16位数据。AD73311一旦进入数据模式,就不能再得到控制信息,所以就永远处于这一模式,除非重启动。这时硬件上可采用发送接收帧同步信号同步方式。混合模式:此时16位码字可能是控制字,也可能是数据。码字的最高位MSB用来标识这个码字是控制命令字(MSB=1)还是数据(MSB=0,低15位是有效数据)。在混合模式下,ADSP-2181可以根据系统的运行状况适时改变AD73311的工作参数,如放大器的放大倍数等。这时硬件上可采用发送接收帧同步信号异步方式,便于ADSP-2181的自主控制。

AD73311控制采样率由时钟分频电路完成。时钟分频电路将从DMCLK引脚输入的外部时钟频率MCLK通过主频时钟因子分频为内部时钟频率DMCLK,MCLK有五种频率选择,由内部控制寄存器B中的CRB4~6三位控制。DMCLK决定了AD73311的采样频率,它也是AD73311串行口的帧同步频率。DMCLK再经串行时钟分频因子分频为串行时钟频率SCLK,DMCLK有四种选择,由内部控制寄存器B中的GRG2~3两位控制。

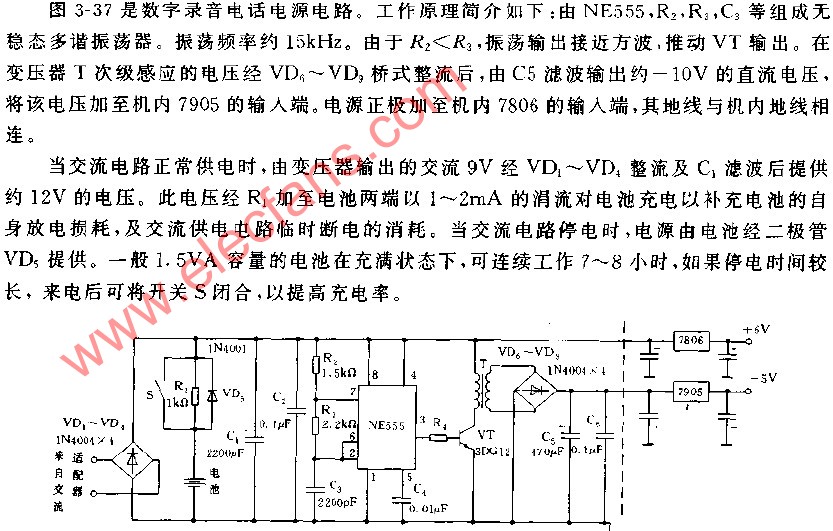

通过编程控制寄存器D,可控制输入输出的增益。输入增益IG可在0~38dB之间调整,输出增益OG可在-15~6dB之间调整。AD73311的具体编程流程图如图3所示,控制程序如下: AX0=DM(0x3fe5); {For 2181-PF0 connect with AD73311-RESET} AR=AX0 AND 0XFFFE; {PF0 pin reset} DM(0x3fe5)=AR; {RESET AD73311 to program} NOP; {Delay} NOP; NOP AX0=DM(0x3fe5); AR=AX0 or 0X0001; {2181-PF0 SET} DM(0x3fe5)=AR; {ready to program} ax0=0x82f9; {写控制寄存器CRC,5V电源,使能ADC和DAC} tx0=ax0; IDLE; ax0=0x811b; {写控制寄存器CRB,分频,设置8K采样率} tx0=ax0; IDLE; ax0=0x8320; {写控制寄存器CRD,输出输入增益为0} tx0=ax0; IDLE; ax0=0x8400; {写控制寄存器CRE,DAC延迟量为0} ax0=ax0; IDLE; ax0=0x8001; {写控制寄存器CRA,进入数据传输模式} tx0=ax0; IDLE; 2.2 闪速存储器与ADSP-2181的接口电路闪速存储器采用韩国三星公司生产的KM29 N32000,容量为4M%26;#215;8=32Mbit,分成512块,每块有16页,每页528个字节。可进行100万次擦写,数据保存时间为10年,通过编程可自动进行擦写。这里用于保存录音数据,其数据保存不需要充电维持。

从理论上说,如果采用G.723标准算法,在8kHz的采样率下,采用5.3kb/s的码率,录音时间最大值约为100分钟;在6.3kb/s码率下最大录音时间约为83分钟,比常用的录音磁带略长,可以满足般的录音要求。如果采用KM29V64000(8M%26;#215;8=64M bit),录音时间可增加一倍。如果需要更长的录音时间,可选择容量更大的闪速存储器。有关KM29N3200的详细特性见参考文献[4]。

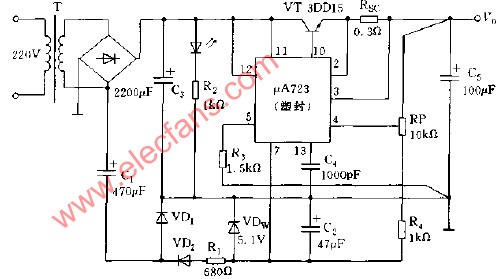

KM29N32000与ADSP-2181的接口电路如图4所示,它的读写及擦除操作说明如下: (1)读操作首先让CLE置高,进入命令模式。此时ALE置低,从I/O口输入00H(表示读操作控制命令字),接下来CLE置低,ALE置高,进入地址加载模式,将要访问的24位地址(A0~A23)分三次由低到高从I/O口磅入。适当延迟后,将ALE置低,就可连续地进行读操作,每次读取一帧数据。得到的数据是加载地址开始的。整个过程CE必须保持低电平。 (2)写操作写操作过程与读操作类似,开始控制命令字是80H,将加载地十分三次送入后,适当延迟,就可连续地向闪速存储器写入一帧数据。数据写完时,CLE置高,送入10H命令字,进行写操作。 (3)擦除操作 保存数据时,如果对应存储区已经有数据,就必须先擦除掉原来数据。每次擦除一次,每块8K字节。首先输入控制命令字60H,接着把块地址分两次送出,再输入D0H命令字进行块擦除。擦除完后,输入命令字70H,可读取擦除状态。如果接下来读取的数据的LSB位为"0"则表示擦除成功,为"1"则表示产生了错误,可重新进行擦除操作。如果再次错误,可能是对应单元出错了。在访问Flash RAM的内存操作中,最重要的是要注意各个信号的时序。必须严格按照说明书的时序图进行操作才能实现正常的功能。

2.3 LCD显示及接口电路

在本系统中用LCD显示当前系统处于的状态,如录放状态、进行的时间等。可由ADSP-2181进行控制,设定显示方式及内容。所用的是点阵式液晶显示器,为日立公司的HD44780A00LCD。里面有专用集成电路作为点阵的控制驱动,只要直接送入数据和指令就可实现所需的显示。在本系统中,由于LCD使能信号脉宽较大,无法直接由DSP产生,因此通过触发单稳触发器74LS123来产生LCD使能信号。接口电路如图5所示。通过调节连接74LS123的R和C值可控制输出Q的脉宽tW。当C≥1000pF时为: tW=K%26;#183;R%26;#183;C 其中K为常数,与外界温度及外接电容C有关,在0.2~0.6间选择。 当C≤1000pF时,tW估计值如下: tW=6+0.05C(pF)+0.45R(kΩ)C+11.6R 当74LS123引脚A出现一个下降脉冲时,输出Q产生一个高电平脉冲,脉宽由R和C决定,驱动LCD工作。录音时LCD上面一行显示RECORD,下行则显示进行的时间;放音时上面一行显示PLAY,下行也显示进行的时间。时间的显示通过ADSP-2181里面定时器中断进行。

3 系统控制软件设计

ADSP21XX系列提供了一整套软件开发工具及相应的仿真器开发平台,给系统的调试与仿真提供了极大的方便。软件开发系统包括系统建造器、带运行时时间库的C编译器、汇编器、连接器、PROM划分器等。通过编译连接汇编源程序,可以生成EXE文件。此文件是存储映像文件,可以加载到仿真器上进行仿真;调试成功后,通过PROM划分器和EPROM烧制设备可以写入EPROM,系统复位时DSP加载EPROM程序便可自动运行,控制整个系统的工作。系统软件设计采用自举和中断控制两种方式。自举方式系统一上电,ADSP-2181读取EPROM中的程序,自动运行程序去控制整个系统工作。

中断控制利用了ADSP-2181的两个中断,即sport0接收中断和timer中断。ADSP-2181的sport与AD73311相连。当得到一个采样数据时,产生一个接收中断,ADSP-2181读取便得到采样数据。由于sport0是全双工的,当产生接收中断时,同时可以发送数据,一方面在录音时可以得到回放效果;另一方面则在播放时可直接发送数据,而对采样数据置之不理,这样便于解码数据以固定的码率回放。Timer中断定时检测外部控制引脚状态,包括录音、放音、快放及码率转换4个引脚,每个引脚的0/1状态对应两种控制,即开始录音/停止录音、开始放音/停止放音、5.3kbps/6.3kbps码率转换及快放状态,共有七个状态。 DSP汇编语言的结构与ASM汇编语言类似,其开头部分对应中断向量表。工作在中断方式时,则向量表对应中断处一般为一条跳转语句;产生中断时,则跳到相应语句执行中断控制功能。主程序的中断设置部分如下: JUMP start;NOP;NOP;NOP; {reset start interrupt} RTI;NOP;NOP;NOP; {IRQ2} RTI;NOP;NOP;NOP; {IRQL1} RTI;NOP;NOP;NOP; {sport0 transmit} JUMP sportReceive;NOP;NOP;NOP; {sport0 receive} RTI;NOP;NOP;NOP; {IRQE} RTI;NOP;NOP;NOP; {BDMA} RTI;NOP;NOP;NOP; {sport1 transmit} RTI;NOP;NOP;NOP; {sport1 receive} JUMP settimer;NOP;NOP;NOP; {timer interrupt} RTI;NOP;NOP;NOP; {PowerDown} sporto和timer中断控制说明如下: (1)sporto接收数据中断在程序中,数据处理集中在此进行。主要过程是:在录音时,每收到240个采样数据,就进行G.723编码,将编码结果保存到闪速存储器中;在播放时,每次读取24个数据,将读取的数据进行解码,再通过串行口发送出去,经扬声器还原成语音信号。其流程如图6所示。(2)timer中断 timer中断用来检测用户的控制信息及显示运行时间信息。用户控制有4个,即码率选择、录音控制、放音控制及快退控制。对应这4个控制引脚,初始设定为输入态,然后通过检测各个引脚的电平设定工作态。其流程如图7所示。

4 系统调试

系统调试要使用AD公司提供的ADSP21XX系列的整套软件开发工具和仿真器。笔者使用ADSP-2181-EZ-ICE仿真器进行调试。仿真器上自带33MHz的2181,调试支持20个断点,可单步、设断点和全速运行,可随时观察和修改寄存器和存储单元的值。仿真器上提供了一个14针的仿真接口,仿真器通过此接口仿真控制目标系统。仿真器与计算机间有一个RS-232接口,通过数据进行连到计算机的串行口上,在仿真器开发平台上就可以进行软件调试。系统调试时遇到的主要问题是存储器读写及LCD的显示问题。开始时发现写进闪速存储器的数据与读出的数据不符。经仔细分析,发现是由于没有严格按照闪速存储器的读写操作时序进行编程,或是延迟量不够,或是两个信号的先后次序弄反了,数据可能根本没有写进去,读出的数据当然是错的。在严格按照其说明书的时序进行编程控制后,数据的读写擦除操作完全正常。在播放录音数据时,曾出现声音跳变不连续的问题,经分析发现原因在于地址定位时出错。因为对闪速存储器担任时每次读写都是一帧数据,而编解码时一次操作的数据为20/24个字节,两者长度不一样,需要进行转换操作。

本系统中ADSP-2181处理器的机器周期为30ns,经设定最大的等待周期为7机器周期后也才有240ns,而LCD的工作使能脉宽至少要300ns。因此在硬件上增加了一单稳延迟电路,这样便解决了此问题。

电子发烧友App

电子发烧友App

评论