如何将数字电位器的带宽从10倍提高到100倍

本文介绍了一种简单电路,能够将数字电位器的带宽从10倍提高到100倍。利用这一方法,数字电位器可以用于视频带宽的高频应用。

数字电位器(digital pot或digipot)被广泛用于控制或调整电路参数。一般而言,由于数字电位器本身的带宽限制,它只能用于直流或低频应用。其典型的-3dB带宽在100kHz至几MHz内,具体与型号有关。然而,通过使用下面介绍的简单方法,可以将电位器的信号带宽从10倍提高到100倍,获得4MHz的0.1dB带宽以及25MHz以上的-3dB带宽。采用这一方法,数字电位器可用于视频或其他高速应用。

有限的调整范围

该方法利用了这一事实——在很多数字电位器应用中,电位器用于对信号进行微调,并不需要从0%到100%的满量程调整,例如:一次性工厂校准等。在这些例子中,数字电位器一般提供10%以下的调整范围。我们正是借助这一有限的调整范围来提高数字电位器的带宽。

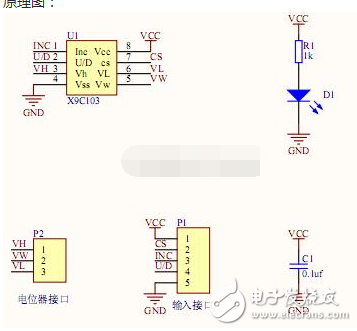

典型应用电路

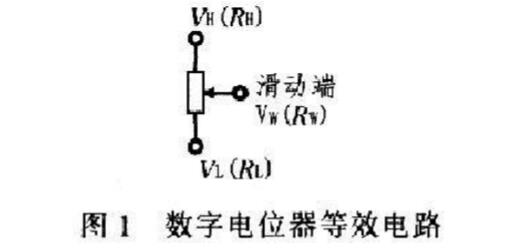

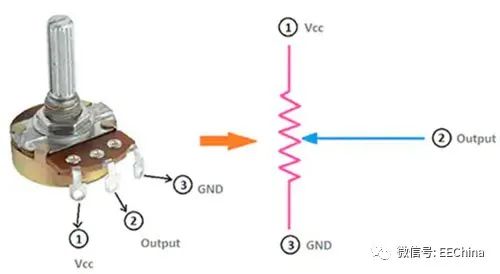

典型的电位器电路配置如图1所示。这里,数字电位器用于改变信号的衰减量。R2为数字电位器,图中还标出了寄生电容(Cwiper)。该电容是所有数字电位器固有的,它限制了电路带宽。电位器在0至满量程之间摆动时,R1和R3用于限制由数字电位器引起的信号衰减。

图1. 典型的数字电位器电路配置

注:由于采用了运算放大器,该电路可以用于放大和衰减。当然,以下介绍的提高带宽的方法与所选择的电路拓扑无关。

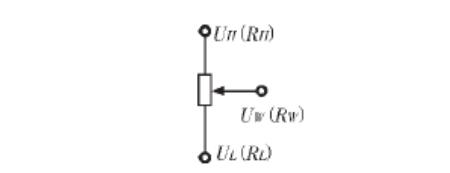

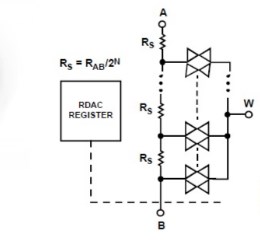

为计算电路的传输函数(VOUT/VIN),可以使用不同模式的电位器—参见图2。图中,R2被分成了R2top和R2bottom,其中,R2top是电位器触点以上的电阻,R2bottom是电位器触点以下的电阻。假设我们使用的电位器具有10kΩ的端到端电阻(忽略触点电阻的影响),R2top和R2bottom相对于数字编码的理想传输函数如图3所示。下面介绍了传输函数的两个端点和中点:

- (1) 当电位器编码 = 0时,R2top = 10kΩ,R2bottom = 0kΩ

(2) 当电位器编码 = 中间位置时,R2top = R2bottom = 5kΩ

(3) 当电位器编码 = 满标位置时,R2top = 0kΩ,R2bottom = 10kΩ

图2. 数字电位器,R2分成了R2top和R2bottom

图3. 数字电位器的理想传输函数

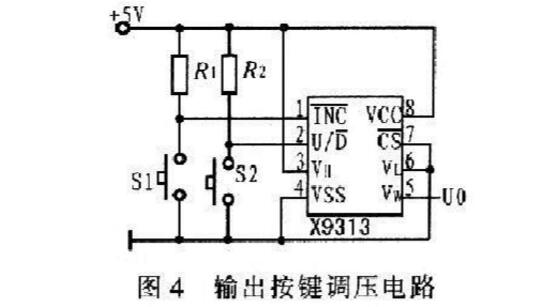

从图4可以得出VOUT/VIN的直流传输函数:

- (4) VOUT/VIN = (R3 + R2bottom)/(R1 + R2 + R3),其中R2 = R2top + R2bottom

图4. 典型数字电位器的电路配置,数字电位器采用新模型

下面,让我们做一些假设:

假设

假设R2 = 10kΩ (常用的数字电位器电阻值),如果希望把输入信号衰减到任意电平,例如,输入值的70% ±5% (输入值的65%到75%)。

然后,使用式(1)–(4),可以看到有65%到75%的调整范围,标称值(中间位置)为70%:

- (5) R1 = 24.9kΩ并且R3 = 64.9kΩ

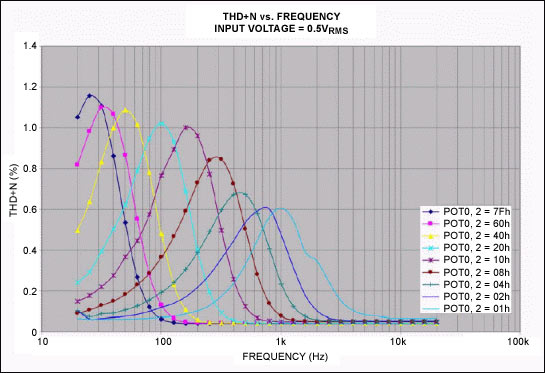

典型应用电路的带宽

利用式(5)的电阻值,假设Cwiper = 10pF,可以获得表1所列出的带宽。实际触点电容在3pF在80pF范围内,与触点电阻、步长数、所采用的IC工艺以及电位器体系结构等因素有关。3V至5V供电、32至256步长的10kΩ电位器的典型电容值为3pF–10pF。

注意,本文分析基于的假设是:触点电容与电位器电阻并联,由此限制电位器的带宽。这种方法是最直接的电位器使用方式,如果采用更复杂的电位器配置,可能会进一步限制带宽。因此,下面对提高带宽的讨论非常有用,即使实际得到的带宽没有达到预期目的。

表1. 图1电路的带宽,采用式5电阻

| Condition | Cwiper = 10pF* | ||

| -0.1dB bandwidth | -0.5dB bandwidth | -3dB Bandwidth | |

| Pot at 0 Code | 106kHz | 245kHz | 702kHz |

| Pot at Mid Scale | 115kHz | 265kHz | 760kHz |

| Pot at Full Scale | 130kHz | 296kHz | 852kHz |

对于视频等应用,这些带宽还是过低。

提高电路带宽

使用低电阻电位器

一种提高电路带宽最明显的方法是选择具有较低阻值的数字电位器,例如,1kΩ电位器,按比例调整R1和R2 (1kΩ电位器与10kΩ电位器相比,阻值减小10倍)。然而,低阻值数字电位器(1kΩ)一般占用较大的裸片面积,意味着较高的成本和较大的封装尺寸,出于这一原因,1kΩ电位器的实际应用非常有限。

如果某一电位器能够满足设计要求,上面提到的10kΩ电位器的带宽会随着电阻的减小而线性提高,例如,提高10倍(假设杂散触点电容没有变化)。

例如,使用1kΩ电位器,设置R1 = 2.49kΩ, R3 = 6.49kΩ,触点电容为10pF,电位器设在中间位置,可以获得1.15MHz的-0.1dB带宽,以及7.6MHz的-3dB带宽。这要比表1所列出的带宽提高10倍。

使用10kΩ电位器,改变电路拓扑

使用高精度电位器,限制编码范围

与1kΩ电位器相比,选择5kΩ和10kΩ电位器可能是更好的方案–可以获得更小封装的电位器,从中可以选择易失或非易失存储器,也有更多的数字接口选择(up/down、I²C、SPI™)以及调整步长(32、64、128、256等)。出于这一原因,下面的设计实例选择了具有10kΩ端到端电阻的电位器。

假设由于成本、体积、接口以及电位器调整步长等因素的限制,需要使用10kΩ端到端电阻电位器,这种情况下如何提高图1电路的带宽呢?

提高带宽的一种方法是去掉电阻R1和R3,使用步长数多于图1电路要求的电位器。例如,32步长电位器获得10%的调整范围,按照上述介绍,可以选择替换这一步长的电位器,而使用256步长电位器,去掉R4和R6,限制电位器的调整范围在达到要求衰减的编码之内—我们继续上面的设计目标,65%到75%。这种方法在图5给出了解释。所使用的编码是从0.65 × 256 ( = 166.4,使用166)到编码0.75 × 256 ( = 192)。这个例子中使用了一个256步长的电位器;由于有限的编码将可用步长数限制在26 (即,10%的调整范围,仅用了256步长的10%)。26步长可用范围对应于上例中的32步长范围。

图5. 只使用高精度(256步长)电位器的部分编码以获得0.65到0.75的调整范围

与32步长的电位器相比,这一方法的一个缺点是:256步长电位器的成本要高得多,可以选择的电位器封装尺寸较大(额外的精度需要额外的开关—例如,256步长和32步长相比,需要占用额外的裸片面积,而且,这些开关并不利于改善Cwiper)。假设Cwiper为30pF,VOUT/VIN = 0.70—在调整范围的中点,图5电路有384kHz的-0.1dB带宽,879kHz的-0.5dB带宽,2.52MHz的-3dB带宽。与表1结果相比,带宽提高了3倍。

一种成本更低、性能更好的方案是在图1电路中加入一些分立电阻,如图6所示。

图6. 在最初电路中使用两个并联电阻(R4和R5),与图1和图2相比,带宽增大100倍

使用并联电阻降低电路阻抗

图6中的电路在图1基础上增加了并联电阻(注意,使用了图2中引入的数字电位器模型)。并联电阻降低了电路阻抗(从而提高了带宽),通过设置电路增益,限制由数字电位器在0编码到满标编码之间摆动时导致的衰减,可以达到双重目的。

设置电位器电路增益,使用并联器件限制其调整范围(R4和R5,而不是简单使用串联器件R1、R2和R3),电路带宽优于图1带宽。

还需要注意,电阻R1、R2和R3还会影响电路增益,但是由于其串联电阻要比R4和R5大得多,这种影响非常小。

可以通过几个简单的示例来说明R4和R5对图6电路的影响。在图7中,电路上部的电阻采用了图中方程给出的电阻组合值。注意,由于R4是与R1和R2top并联,它降低了电路阻抗。

图7. 简化电路“上部”电阻

在图8中,电路下部的电阻采用了图中方程给出的电阻组合值。注意,由于R5与R3和R2bottom并联,它也降低了电路阻抗。正是较低的电路阻抗使得带宽大大体高,达到设计目标的要求。

图8. 简化电路“下部”电阻

图9结合了前面图中的简化示例,给出了VOUT/VIN传输函数。从该图中可以清楚看到,通过降低电路阻抗(Rtop小于R1 + R2top,Rbottom小于R2bottom + R3),提高了电路带宽。

图9. 图7和图8的简化电路

实际值

实际设置R1、R3、R4和R5的阻值,可以对比图1电路得到的带宽,从而确定R4和R5对电路性能的影响。

使用图9中的方程,可以得出R1、R3、R4和R5的阻值,然后计算最终带宽。

使用表格,可以找到满足图9方程的元件值:

- (6) R1 = 3.48kΩ、R2 = 10kΩ、R3 = 4.53kΩ、R4 = 1kΩ和R5 = 2.8kΩ

采用这些元件值得出了表2列出的带宽。注意,这些结果比图1电路改善100倍,其数据列在表1中!!

表2. 图6电路的带宽,采用式6电阻

| Condition | Cwiper = 10pF* | ||

| -0.1dB bandwidth | -0.5dB bandwidth | -3dB Bandwidth | |

| Pot at 0 Code | 4.1MHz | 9.3MHz | 26.3MHz |

| Pot at Mid Scale | 4MHz | 8.9MHz | 25.1MHz |

| Pot at Full Scale | 4.3MHz | 9.6MHz | 27.3MHz |

总结

本文介绍了在窄带数字电位器中简单加入几个并联电阻以提高系统带宽的方法,可以显著提高系统性能(带宽可提高100倍)。设计前提是假设实际应用允许降低电位器的控制范围,以提高带宽。带宽提高后,数字电位器可以用于以前无法涉及的高频领域,例如视频信号链路控制等。

电子发烧友App

电子发烧友App

评论