MAX9217/MAX9218串行器和解串器芯片组通过一对儿双绞线LVDS链路实现视频数据传输,广泛用于汽车和工业应用领域。视频信号的每一帧总是存在消隐周期,可以利用这些周期“承载”音频数据。在本应用笔记中,我们讨论音频数据的传输格式,视频链路发送数据的方法以及系统实现的具体实例。

Introduction

MAX9217/MAX9218芯片组[1]是一个收发器对儿,发送器(MAX9217)将并行数据转换成串行数据,发送给接收器(MAX9218);接收器再将串行数据转换成并行数据。该芯片组设计用于通过一对儿低成本双绞线电缆(如,以太网中常用的UTP-CAT5电缆),将视频和控制信号从图形控制器(处理器)传输到LCD或等离子平面显示器。传输距离可超过10米。

该芯片组链路结构简单,所使用的传输线为低成本电缆,是汽车、仪表、医疗设备等视频显示的理想方案。 该芯片组不仅可以在两点之间传送视频信号,有时,人们还希望其同时传送音频信号。在本应用笔记中,我们将讨论如何利用视频信号的消隐期,通过控制信号通道将音频数据传送到显示器。我们还将解释怎样把数字音频数据转换成模拟音频信号,并给出了显示面板端扬声器驱动的系统结构。

MAX9217/MAX9218链路功能和视频数据格式

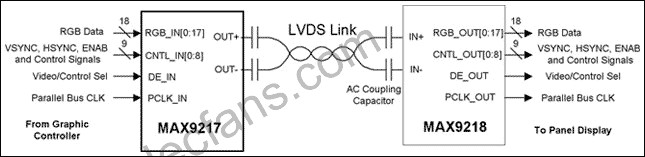

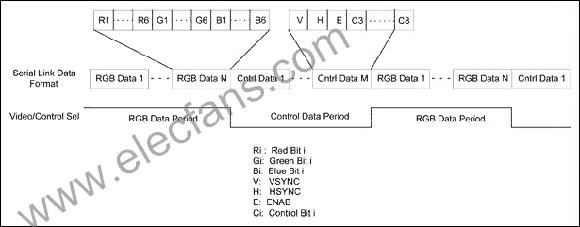

MAX9217串行器具有27位并行输入,总线速率高达35Mbps。在这27位中,18位是视频RGB数据:3基色各占用6位,其余9位是控制信号。9位控制信号中的前3位指定为垂直、水平和RGB数据同步:VSYNC (C0)、HSYNC (C1)和ENAB (C2)。剩下的6个控制位(C3至C8)用于其他控制信号。本例中,我们使用6个控制位中的一部分传输音频数据。MAX9217可以将18位RGB数据或9位控制数据转换为串行数据,然后通过LVDS链路对其进行传输。在视频显示的消隐期内发送控制数据,由RGB数据使能信号(ENAB)指示。

MAX9218接收到串行数据后,将其转换成与MAX9217输入格式相同的并行数据。同样,当MAX9218输出并行数据时,根据串行LVDS链路的时序重新生成总线时钟。图1所示为MAX9217和MAX9218之间视频、控制数据链路设置和连接的结构图。图2所示为视频数据和控制数据的时序。根据视频格式、显示器分辩率和链路速率,RGB数据的控制占空比在1%至5%之间。

数字音频数据类型和传输格式

数字音频数据有多种不同格式。我们讨论3种最常用的格式:采样数字音频(PCM)、MPEG层3音频(MP3) 和ATSC数字音频压缩标准(AC3)。

PCM数字音频是CD ROM或DVD采用的数据格式。对左右声道的音频信号采样得到PCM数字信号,采样率为44.1kHz,精度为16位或32位。因此,精度为16位时,PCM音频数据速率为1.41Mbps;32位时为2.42Mbps。一张700MB CD可保存大约60分钟的16位PCM数据格式的音乐。

MP3是MP3播放器采用的音频格式,对PCM音频数据进行压缩编码。立体声MP3数据速率为112kbps至128kbps。对于这种数据速率,解码后的MP3声音效果与CD数字音频的质量相同。AC3是数字TV、HDTV和电影数字音频编码标准。立体声AC3编码后的数据速率为192kbps。

为了恢复音频信号,可将编码后的音频数据送入音频解码器芯片,该芯片生成PCM数字数据,传送至音频DAC,最终恢复成模拟音频信号。相反,没有编码的数字音频数据可以直接送入音频DAC。(下面详细说明这种类型的系统实现。)

编码或解码音频数据的常用串行音频数字接口是Inter-IC音频总线(I2S) 。图3所示为I2S接口配置和时序图。每个音频字的边界由信号WS标识。在我们的应用中采用配置模式1。在SCK信号的上升沿,数据被锁存至接收器,但是当SCK保持低电平时,不接收数据。

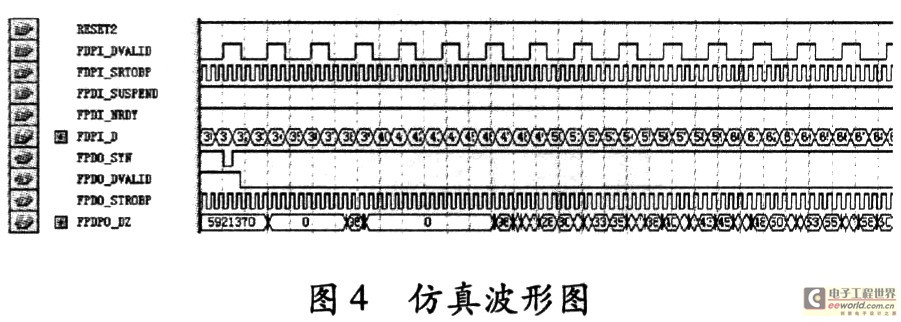

使用MAX9217和MAX9218之间的串行链路仿真I2S接口,可以将音频数据从图形控制器一端传送至远端。我们将控制位C3和C4分别分配给SD和WS信号。对于SCK时钟,如果要发送PCM数字音频,可以直接使用MAX9218恢复的像素时钟PCLK_OUT。对于传送MP3或AC3音频,可采用控制位C5为SCK时钟生成一半或较低速率的像素时钟。图4显示了这两种情况的时序波形。

为防止接收器溢出,大部分I2S接口需要进行节流控制,连续发送数据时,可以将SCK置低,直接实现节流控制。图4中Case 1,工作期间SCK信号无法置低,可以使用片选引脚/CS关闭接收器。在这种情况下,图4中的Case 1将C6分配给/CS信号。

消隐比和音频数据吞吐率

由于音频数据是通过视频信号的消隐周期传输的,我们需要确定给定像素频率fP下行消隐比和场消隐比。图5所示为显示面板上的行消隐和场消隐周期。

以RL表示行消隐比,RF表示场消隐比,由图5所示,我们可以按以下各式计算这些比值:

RL = (I1 + I2) / L 和 RF = (f1 + f2) / F

由此得到音频数据吞吐率RA ,即:

RA = (RF F + (1 - RF) RL

F + (1 - RF) RL L) fP

L) fP

其中 F和

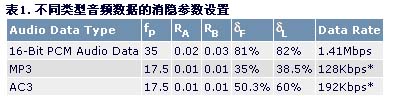

F和 L是消隐周期中的音频数据传输利用率。利用率是指整个消隐周期中,音频数据传输所占的比例,是节流控制的结果。作为一个实例,表1所示参数为3种类型的音频数据设置数据速率。

L是消隐周期中的音频数据传输利用率。利用率是指整个消隐周期中,音频数据传输所占的比例,是节流控制的结果。作为一个实例,表1所示参数为3种类型的音频数据设置数据速率。

注:MP3和AC3音频数据都含有头文件。考虑到这些信息后,实际的编码数据速率会稍高一些[2, 3]。

系统实现

要在面板端播放音频信号,我们需要将PCM数据送至音频DAC或解码MP3和AC3数据,然后将其送至音频DAC。由于没有反向通道将握手信号回送给控制器,解码器主机时钟必须与像素时钟同步,以防止数据上溢或下溢。图6所示为编码和未编码数据音频重放的系统结构图。

在上述结构图中,采用了3次I2S接口。从左边开始,第一和第二个I2S接口的数据速率相同,能够达到35MHz。第三个接口——MAX9850 DirectDrive耳机放大器[5]接口,速率固定为音频采样率的倍数。时钟SCK2送入MAX9491多路时钟发生器[6],它产生解码器、FIFO和MAX9850的同步时钟。MAX9491提供包含OTP的两个可编程PLL,是本应用的理想频率合成器。Case 1适用于提供解码PCM音频数据的图形控制器,Case 2用于面板端压缩数据的解码。Case 1的节流控制由/CS引脚实现,Case 2中通过空闲SCK时钟实现。对比这两种实现方式,我们看到PCM音频数据的Case 1不需要占用太多的消隐时间(表1),不需要使用音频解码器芯片,成本低于Case 2。因此,如果图形控制器能够从MP3或AC3等编码音频数据流中生成PCM数据,建议直接在链路上传送这些数据。

Introduction

MAX9217/MAX9218芯片组[1]是一个收发器对儿,发送器(MAX9217)将并行数据转换成串行数据,发送给接收器(MAX9218);接收器再将串行数据转换成并行数据。该芯片组设计用于通过一对儿低成本双绞线电缆(如,以太网中常用的UTP-CAT5电缆),将视频和控制信号从图形控制器(处理器)传输到LCD或等离子平面显示器。传输距离可超过10米。

该芯片组链路结构简单,所使用的传输线为低成本电缆,是汽车、仪表、医疗设备等视频显示的理想方案。 该芯片组不仅可以在两点之间传送视频信号,有时,人们还希望其同时传送音频信号。在本应用笔记中,我们将讨论如何利用视频信号的消隐期,通过控制信号通道将音频数据传送到显示器。我们还将解释怎样把数字音频数据转换成模拟音频信号,并给出了显示面板端扬声器驱动的系统结构。

MAX9217/MAX9218链路功能和视频数据格式

MAX9217串行器具有27位并行输入,总线速率高达35Mbps。在这27位中,18位是视频RGB数据:3基色各占用6位,其余9位是控制信号。9位控制信号中的前3位指定为垂直、水平和RGB数据同步:VSYNC (C0)、HSYNC (C1)和ENAB (C2)。剩下的6个控制位(C3至C8)用于其他控制信号。本例中,我们使用6个控制位中的一部分传输音频数据。MAX9217可以将18位RGB数据或9位控制数据转换为串行数据,然后通过LVDS链路对其进行传输。在视频显示的消隐期内发送控制数据,由RGB数据使能信号(ENAB)指示。

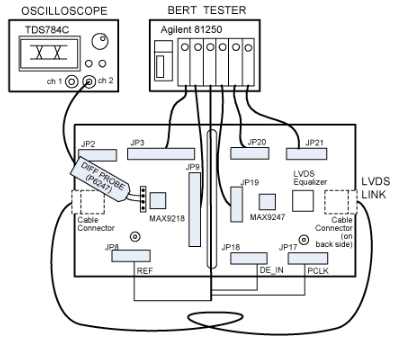

MAX9218接收到串行数据后,将其转换成与MAX9217输入格式相同的并行数据。同样,当MAX9218输出并行数据时,根据串行LVDS链路的时序重新生成总线时钟。图1所示为MAX9217和MAX9218之间视频、控制数据链路设置和连接的结构图。图2所示为视频数据和控制数据的时序。根据视频格式、显示器分辩率和链路速率,RGB数据的控制占空比在1%至5%之间。

图1. MAX9217/MAX9218的视频链路设置

图2. 串行链路的视频数据和控制数据格式

数字音频数据类型和传输格式

数字音频数据有多种不同格式。我们讨论3种最常用的格式:采样数字音频(PCM)、MPEG层3音频(MP3) 和ATSC数字音频压缩标准(AC3)。

PCM数字音频是CD ROM或DVD采用的数据格式。对左右声道的音频信号采样得到PCM数字信号,采样率为44.1kHz,精度为16位或32位。因此,精度为16位时,PCM音频数据速率为1.41Mbps;32位时为2.42Mbps。一张700MB CD可保存大约60分钟的16位PCM数据格式的音乐。

MP3是MP3播放器采用的音频格式,对PCM音频数据进行压缩编码。立体声MP3数据速率为112kbps至128kbps。对于这种数据速率,解码后的MP3声音效果与CD数字音频的质量相同。AC3是数字TV、HDTV和电影数字音频编码标准。立体声AC3编码后的数据速率为192kbps。

为了恢复音频信号,可将编码后的音频数据送入音频解码器芯片,该芯片生成PCM数字数据,传送至音频DAC,最终恢复成模拟音频信号。相反,没有编码的数字音频数据可以直接送入音频DAC。(下面详细说明这种类型的系统实现。)

编码或解码音频数据的常用串行音频数字接口是Inter-IC音频总线(I2S) 。图3所示为I2S接口配置和时序图。每个音频字的边界由信号WS标识。在我们的应用中采用配置模式1。在SCK信号的上升沿,数据被锁存至接收器,但是当SCK保持低电平时,不接收数据。

图3. I2S接口配置和时序

使用MAX9217和MAX9218之间的串行链路仿真I2S接口,可以将音频数据从图形控制器一端传送至远端。我们将控制位C3和C4分别分配给SD和WS信号。对于SCK时钟,如果要发送PCM数字音频,可以直接使用MAX9218恢复的像素时钟PCLK_OUT。对于传送MP3或AC3音频,可采用控制位C5为SCK时钟生成一半或较低速率的像素时钟。图4显示了这两种情况的时序波形。

为防止接收器溢出,大部分I2S接口需要进行节流控制,连续发送数据时,可以将SCK置低,直接实现节流控制。图4中Case 1,工作期间SCK信号无法置低,可以使用片选引脚/CS关闭接收器。在这种情况下,图4中的Case 1将C6分配给/CS信号。

图4. I2S接口的控制数据位波形

消隐比和音频数据吞吐率

由于音频数据是通过视频信号的消隐周期传输的,我们需要确定给定像素频率fP下行消隐比和场消隐比。图5所示为显示面板上的行消隐和场消隐周期。

图5. 行消隐和场消隐

以RL表示行消隐比,RF表示场消隐比,由图5所示,我们可以按以下各式计算这些比值:

RL = (I1 + I2) / L 和 RF = (f1 + f2) / F

由此得到音频数据吞吐率RA ,即:

RA = (RF

其中

注:MP3和AC3音频数据都含有头文件。考虑到这些信息后,实际的编码数据速率会稍高一些[2, 3]。

系统实现

要在面板端播放音频信号,我们需要将PCM数据送至音频DAC或解码MP3和AC3数据,然后将其送至音频DAC。由于没有反向通道将握手信号回送给控制器,解码器主机时钟必须与像素时钟同步,以防止数据上溢或下溢。图6所示为编码和未编码数据音频重放的系统结构图。

图6. 面板端音频重放实现

在上述结构图中,采用了3次I2S接口。从左边开始,第一和第二个I2S接口的数据速率相同,能够达到35MHz。第三个接口——MAX9850 DirectDrive耳机放大器[5]接口,速率固定为音频采样率的倍数。时钟SCK2送入MAX9491多路时钟发生器[6],它产生解码器、FIFO和MAX9850的同步时钟。MAX9491提供包含OTP的两个可编程PLL,是本应用的理想频率合成器。Case 1适用于提供解码PCM音频数据的图形控制器,Case 2用于面板端压缩数据的解码。Case 1的节流控制由/CS引脚实现,Case 2中通过空闲SCK时钟实现。对比这两种实现方式,我们看到PCM音频数据的Case 1不需要占用太多的消隐时间(表1),不需要使用音频解码器芯片,成本低于Case 2。因此,如果图形控制器能够从MP3或AC3等编码音频数据流中生成PCM数据,建议直接在链路上传送这些数据。

电子发烧友App

电子发烧友App

评论