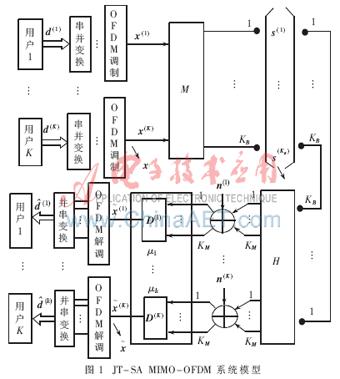

1. 引言

信道估计是OFDM 中的关键技术,其目的是给出接收端进行的信道均衡、信号检测、信道质量测量和软译码等处理时所需要的信道参数,其性能直接关系到整个OFDM 通信系统误码率性能[1] [2]。

基于参考信号(RS)的OFDM 的信道估计方法主要包括LS 算法和MMSE 算法:LS 算法简单,适用于一般无线环境;MMSE 算法可靠性较高,但过于复杂[3] [4]。结合MIMO 技术的OFDM 系统上的信道估计要考虑对每根接收天线接收到多根发射天线的导频进行分离,以及对多根接收天线接收数据进行协调处理[5]。目前在FPGA 上进行MIMO-OFDM 系统信道估计的设计方案还比较少,一些传统方案[5]-[7]中,每条信道都需要设置一个信道估计器来估计导频位置信道频率响应,插值估计通过复数乘法器实现,这样将会消耗大量的硬件资源。本文基于文献[8]中的MIMO-OFDM 系统,在ML605 开发板上进行信道估计的方案设计实现。根据系统应用环境,考虑资源消耗与复杂度,采用LS 估计算法以及线性插值算法进行模块化设计,具有良好的扩展性。基于传统信道估计方案对LS 估计模块进行精简,对插值模块内插系数计算进行优化,减少FPGA 运算单元及存储单元消耗。经测试,将该方案加入视频传输系统后,视频信号清晰稳定。

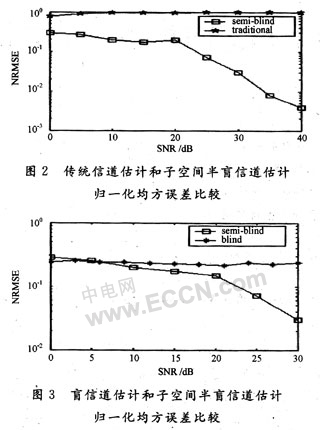

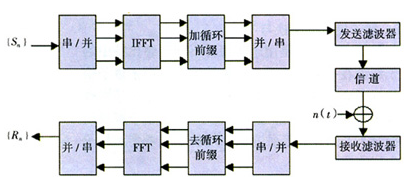

2. MIMO-OFDM接收端链路模型

图1显示的是用于进行视频实时传输的双层物理层接收链路模型。接收端信号经过OFDM解调后,分离出用户数据信号和参考信号。信道估计模块利用接收到的的参考信号与本地存储的参考信号共轭相乘得到信道参数[9] ,根据MIMO分集空频解码公式,将用户数据信号与信道参数整理后输出给MIMO解码模块进行处理,从而减少无线信道干扰。系统全局时钟频率为100 MHz,系统带宽10 MHz,子载波数量为600个,MIMO采用2T × 2R天线矩阵。

3. 信道估计模块总体设计

本文进行的信道估计模块设计,首先在Xlinx ISE上使用VHDL语言进行建模,并加入到接收端链

Figure 1. Architecture of receiver of video transmission system

图1. 视频传输系统接收链路模型

路中进行仿真测试;之后在Xlinx XPS上将物理链路作为硬件外设挂载到系统中,配置Microblaze IP核;最后将接收端和发送端程序分别下载到两块ML605开发板中,在发送端接上摄像机和视频服务器,接收端通过解码器解码,在显示器上可以看到摄像机捕获的视频图像。

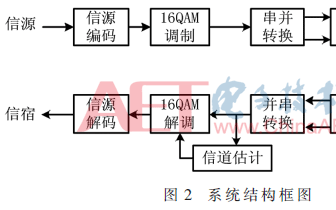

信道估计模块采用双层链路结构,分别对两根接收天线的接收数据进行处理。顶层模块由四种模块构成:LS估计模块、内插模块、数据处理模块和输出模块,如图2所示。

图2中RS00和RS10分别表示接收天线0所接收到的两根发送天线发送的参考信号,RS01和RS11分别表示接收天线1所接收到的两根发送天线发送的参考信号。LS估计模块接收到参考信号(Reference signal, RS)后估计出RS所在位置的信道参数hls,并输出给内插模块;内插模块根据导频图案,利用接收到的导频位置信道参数,通过频域和时域插值计算用户数据位置的信道参数h,并存储在RAM中;数据处理模块接收用户数据,并将数据整理成MIMO解码模块需要的格式后输出给输出模块;输出模块利用从OFDM解调模块接收到的用户数据地址,从RAM中提取相应用户数据位置的四条信道(两根发射天线分别到两根接收天线)的信道参数,将用户数据与信道参数一同输出。

为方便以后对物理链路进行优化升级,各项功能采用模块化设计,模块外部接口统一采用AXI-Stream接口,模块之间通过一个具有AXI-Stream格式接口的FIFO进行数据缓冲相连,如图3。

AXI-Stream协议下,时钟上升沿到来时,接收端或者发送端的READY和VALID两个握手信号同时为“1”时完成一次数据传输。FIFO输出的READY信号为“1”时,指示FIFO未满;FIFO输出VALID信号为“1”时,指示FIFO中存在有效数据。

视频传输系统采用LTE下行规定的帧结构与导频图案[10] ,如图4所示。导频图案中白格表示承载用户数据及控制信息的资源粒子(RE),黑格表示承载导频数据的RE,叉格表示不承载任何信息的空白RE。

3.1. LS估计模块

LS估计模块主要用LS算法估计出RS位置的信道参数![]() 。设接收到的RS为

。设接收到的RS为![]() ,本地存储的RS为

,本地存储的RS为![]() 。根据LS算法得到:

。根据LS算法得到:

![]() (1)

(1)

由于![]() 与

与![]() 均为复数,设

均为复数,设![]() ,

,![]() ,带入式(1)后得到:

,带入式(1)后得到:

![]() (2)

(2)

根据式(2),运用二叉树流水线技术对LS估计器进行设计。二叉树流水线结构能够充分发挥FPGA并行流水线的优势,提高系统计算效率,减少寄存器消耗。在流水线设计时,首先需要选择合适的流水线级数来减少处理延时。例如对于N个数据参与处理,并且需要经过七次相乘或者相加运算得到结果的算式,在实现时流水线级数应该设置为![]() 。其次,每一级流水线不能承担过多的计算,否则会降低整体流水线处理速度。本文中LS估计器的设计采用三级流水线,每一级流水线承担一次运算任务,延时一个时钟周期,如图5所示。

。其次,每一级流水线不能承担过多的计算,否则会降低整体流水线处理速度。本文中LS估计器的设计采用三级流水线,每一级流水线承担一次运算任务,延时一个时钟周期,如图5所示。

Figure 2. Architecture of channel estimation module

图2. 信道估计模块顶层结构

Figure 3. Architecture of AXI-Stream interface

图3. AXI-Stream协议接口结构

Figure 4. The frame structure and the double-antenna pilot pattern of the system

图4. 系统帧结构与双天线导频图案

本地RS由Matlab生成后,存入ROM当中,由状态机控制ROM地址,输出相应的RS。传统信道估计方案中,每根接收天线需要两个LS估计器进行RS位置信道参数估计[5] [6] 。以天线0接收到的RS为例,RS00以及RS01分别需要一个LS估计器以及一个存储本地RS的ROM进行参数估计。由于天线0和天线1发送的RS相同,本方案中将RS00和RS01合并后,利用状态机控制交替输入到一个LS估计器,减少一半运算单元以及ROM等资源的使用。

3.2. 内插模块

内插模块根据导频图案进行线性插值。首先进行频域插值,以天线0发送的导频图案为例。频域插值公式如式(3)所示。

其中![]() 表示频率方向RS间隔,

表示频率方向RS间隔,![]() 表示频率

表示频率![]() 、时间

、时间![]() 位置上的信道响应。通过从估计模块获得的hls估计出RS所在OFDM符号上(符号0和符号4,以符号0为例)RS位置之间的信道参数,存入相应的FIFO中。每个符号中有100个RS,所以循环99次。循环过后将边沿处子载波信道参数直接赋值为最近的RS位置的信道参数。流程如图6所示。

位置上的信道响应。通过从估计模块获得的hls估计出RS所在OFDM符号上(符号0和符号4,以符号0为例)RS位置之间的信道参数,存入相应的FIFO中。每个符号中有100个RS,所以循环99次。循环过后将边沿处子载波信道参数直接赋值为最近的RS位置的信道参数。流程如图6所示。

然后进行时域线性插值,时域插值公式如式(4)所示:

其中![]() 表示时间方向导频间隔,

表示时间方向导频间隔,![]() 表示频率

表示频率![]() 、时间

、时间![]() 位置上的信道响应。通过fifo中由频域插值得到的符号0和符号4的信道参数估计出其他符号上所有子载波的信道参数,将其映射到相应符号RAM中的对应地址当中,便于输出模块用接收到的数据地址读取相应位置的信道参数。由于系统配置子载波数为600个,所以设置循环600次。时域插值中符号0和符号4的每个符号的信道参数需要使用2次,因此在第一次接收并进行插值计算后,该符号信道参数将存入临时fifo (temp)中以备下一轮循环插值使用。流程如图7所示。

位置上的信道响应。通过fifo中由频域插值得到的符号0和符号4的信道参数估计出其他符号上所有子载波的信道参数,将其映射到相应符号RAM中的对应地址当中,便于输出模块用接收到的数据地址读取相应位置的信道参数。由于系统配置子载波数为600个,所以设置循环600次。时域插值中符号0和符号4的每个符号的信道参数需要使用2次,因此在第一次接收并进行插值计算后,该符号信道参数将存入临时fifo (temp)中以备下一轮循环插值使用。流程如图7所示。

为了减少FPGA中有限的乘法器资源消耗,计算内插系数时通过输入数据移位计算来实现。传统插值估计在内插系数分母不为![]() 时,需要使用乘法器将输入数据和预先存储在ROM中的插值系数相乘[7] 。本设计中,当内插系数分母不为

时,需要使用乘法器将输入数据和预先存储在ROM中的插值系数相乘[7] 。本设计中,当内插系数分母不为![]() 时,选择在数据低位增加8位数据小数位长度,移位计算出原始数据的多个

时,选择在数据低位增加8位数据小数位长度,移位计算出原始数据的多个![]() 分之1,通过二叉树流水线相加后再截取高16位数据得到,如公式(5) (6) (7) (8)所示,系数误差控制在213分之1左右。

分之1,通过二叉树流水线相加后再截取高16位数据得到,如公式(5) (6) (7) (8)所示,系数误差控制在213分之1左右。

3.3. 数据处理模块和输出模块

MIMO发射分集方案选择LTE标准的空频编码。在MIMO解码模块进行极大似然译码时,需要接收对应的用户数据和信道参数来构造判决矢量。根据判决矢量构造公式可以知道,在每次构造判决矢量时需要两条接受链路上连续两个RE上的用户数据和四条信道的信道参数[11] 参与计算。数据处理模块分别将接收到的两层链路中连续两个RE上用户数据进行串行合并,然后输出到输出模块。输出模块根据接收到的用户数据地址,计算两个RE地址的信道参数的均值,和用户数据一同输出给MIMO解码模块。

3.4. 综合测试与仿真

建模完成后,需要在ISE上进行综合。综合后可以在ISE中查看信道估计模块的资源消耗,如表1所示。

Figure 5. Architecture of LS estimation module

图5. LS估计模块内部结构

Figure 6. The flow chart of frequency domain interpolation

图6. 频域插值流程图

综合成功后将信道估计模块加入到整个MIMO-OFDM物理收发链路中,在发送端输入数据源,利用Modelsim进行仿真。为了在FPGA上进行计算,所有数据都已经量化为16位定点小数,其中最高位为符号位,次高位为整数位,其余14位为小数位,因此,数据范围在−2~+2之间。信道参数输出如图8所示。

尽管数据处理过程中引入了定点误差和截位误差,信道00和信道11的信道参数实部的定点16位数据(CH00_OUT_RE和CH01_OUT_RE)依然接近16,384 (即表示1)。在有线的环境下,由于信道01和信道10没有接收数据,信道参数的实部和虚部定点16位数据接近0 (0)。MIMO-OFDM基带传输链路输入输出如图9所示,其中valid信号表示数据有效性。数据输入链路的发送端(tx)后,接收端(rx)输出数据准确,且没有丢失。因此信道估计模块在有线环境下能够使系统正确恢复发射端数据。

4. 视频传输测试

将设计完成的物理层链路的发送端和接收端分别作为外设挂载到XPS工程中。配置ML605开发板中Microblaze IP核,用于在发送端接接收并封装视频服务器发送的视频信息,通过逻辑信道发送给物理层链路;在接收端接收并解析物理层的数据信息,发送给视频解码器解码。Microblaze IP核与物理层链路通过PLB (Processor Local Bus)总线进行数据传输。配置完成后,将生成的比特流文件下载到ML605

Table 1. Hardware resource consumption

表1. 硬件资源消耗

Figure 7. The flow chart of time domain interpolation

图7. 时域插值流程图

Figure 8. Simulation of channel parameters output

图8. 信道估计模块信道参数输出仿真

Figure 9. Simulation of input and output of MIMO-OFDM link图9. MIMO-OFDM链路收发仿真

开发板中,设置摄像机与视频服务器,在接收端视频流通过解码器解码后,显示器上可以看到摄像机拍摄到的视频,如图10所示。两套设备置于相邻的两个实验室中,可以看到本地摄像头拍摄图像与接收到的

Figure 10. Video transmission test

图10. 视频传输测试

图像清晰稳定,验证了在实验室简单环境下信道估计模块可以有效抵抗信道衰落,提高系统传输可靠性。

5. 结论

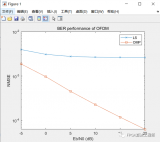

本文针对MIMO-OFDM视频传输系统,利用LS算法和线性插值算法,设计了一种结构优化,消耗FPGA逻辑资源少的信道估计方案,使得FPGA芯片上有足够的空间对物理层链路进行进一步的设计。最大支持282.509 MHz时钟频率,经测试:加入信道估计后,视频传输系统能够在实验室简单固定的环境下进行无线视频传输,图像清晰稳定。

电子发烧友App

电子发烧友App

评论