CS5343 - 98 dB, 96 kHz, Multi-Bit Audio A/D Converter - Cirrus Logic

2022-11-04 17:22:44

CS1237无法正常读配置和写配置问题。图1读配置时序图,如附件所示。图2单片机管脚未连接AD芯片,时序图。通过对比两个时序,发现数据总线被AD芯片强制拉低了。这种芯片使用时,需要主控芯片有推挽输出模式强制拉高总线,弱上拉类型芯片该如何使用这个芯片??

2020-11-27 10:18:20

的数字音频程序兼容。 集成电平转换器允许CS42406和其他在各种逻辑电平上运行的设备之间进行简单的接口。 高通滤波器可用于A/D的左右通道。这允许A/D消除不需要的直流偏移。 CS42406动态范围

2020-07-02 09:48:02

CS4923 CS4924 CS4925 CS4926 音频译码器系列用户指南II

2009-05-13 10:14:47

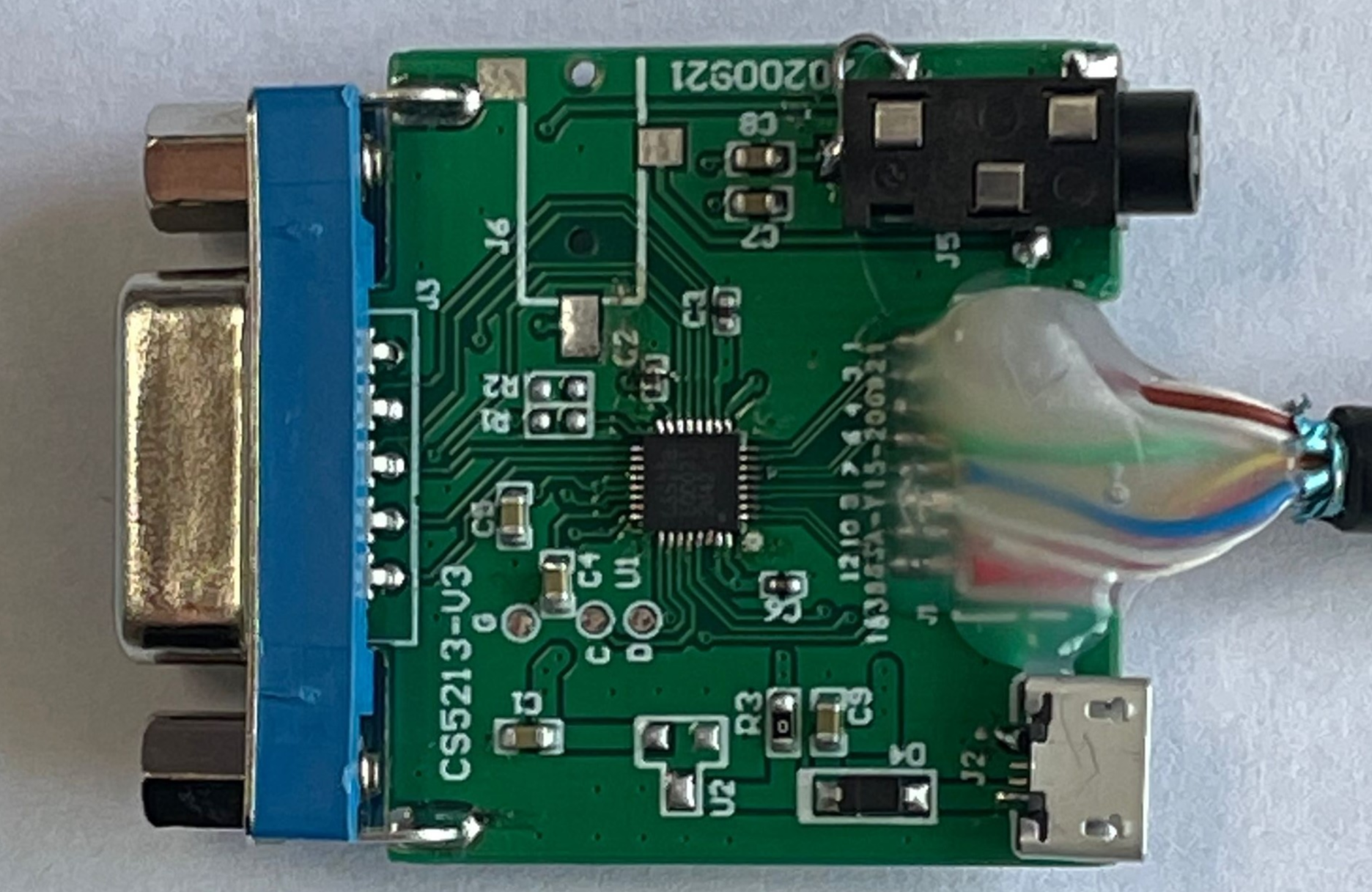

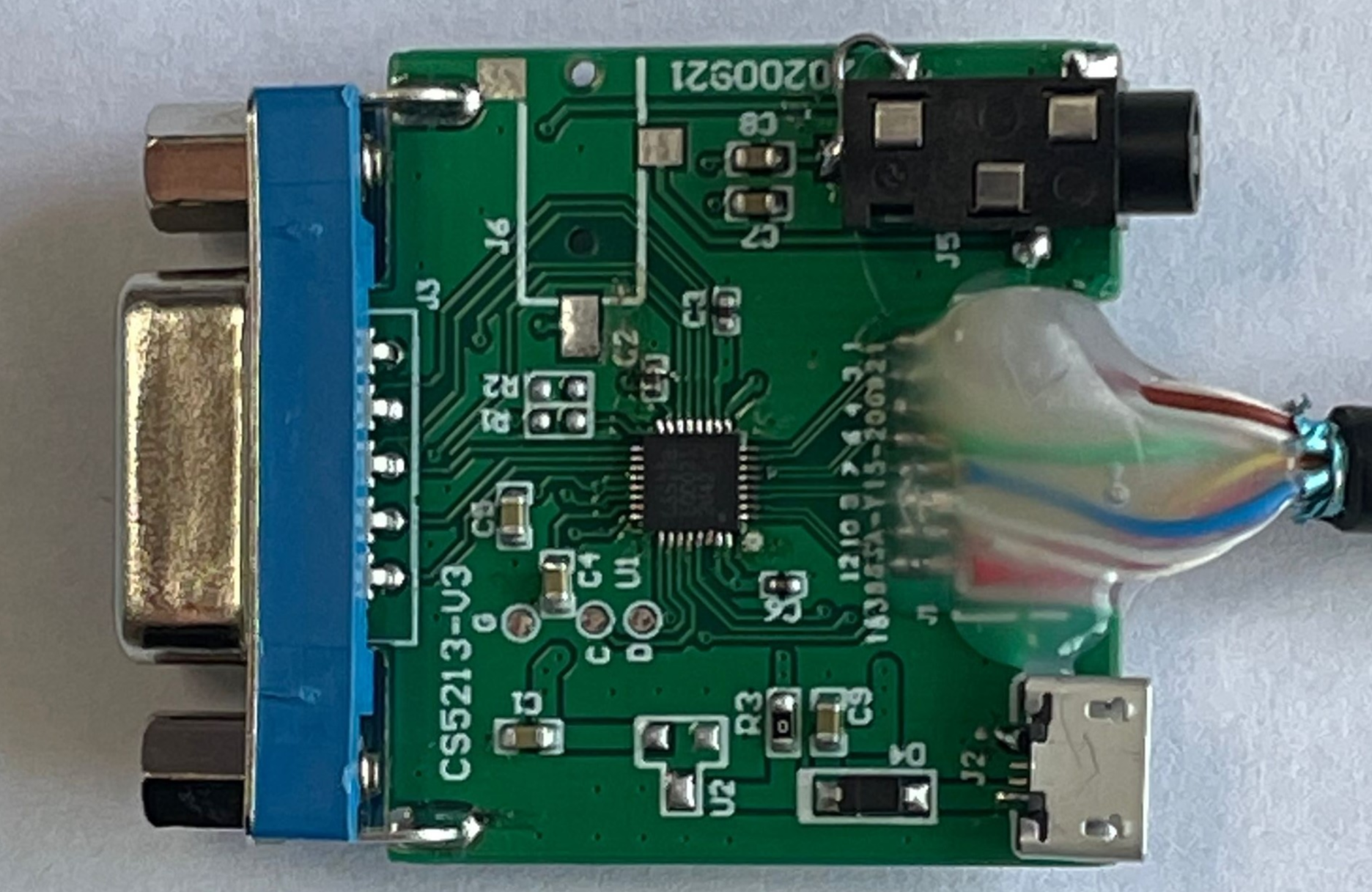

Capstone CS5213 HDMI-VGA转换器结合了HDMI输入接口和模拟RGB DAC输出。

通过支持和片上音频DAC,它节省了成本并优化了板空间。嵌入式MCU基于工业标准8051核心。

CS5213适用于多个细分市场和显示器应用,桌面、加密狗和对接系统。

2023-09-19 07:34:49

Capstone CS5213 HDMI到VGA转换器结合了HDMI输入接口和模拟RGB DAC输出。带支持片上音频数模转换器,节省成本,优化电路板空间。嵌入式单片机基于工业标准8051内核

2022-04-05 23:38:29

瑞奇达CS5213是一款HDMI到VGA转换器结合了HDMI输入接口和模拟RGB DAC输出单颗集成芯片。CS5213主要用于HDMI转VGA带DAC模拟音频输出转换器或者HDMI转VGA带

2022-03-02 07:50:33

终端设备没有,CS5213将响应EDID)使用内部预装ROM支持EEPROM自由模式支持自动节电模式支持VGA连接检测内部上电复位(POR)双通道16位分辨率sigma-delta DAC支持音频采样频率

2021-01-13 15:41:17

稳压器核心电压1.2V符合HDCP 1.4规范的片上HDCP引擎集成片上HDCP密钥CS5213支持2通道IIS音频接口CS5213支持1080i分辨率CS5213封装方式:CS5213封装尺寸

2022-05-18 10:12:45

DA-E23音频DAC解码器基于CS8416+ES9023架构,真正支持192kHz/24bit解码。设置有光纤、同轴各2个数字输入接口;模拟输出2个,其中一个带有音量调节。板载全密闭式电源变压器

2012-12-01 18:09:16

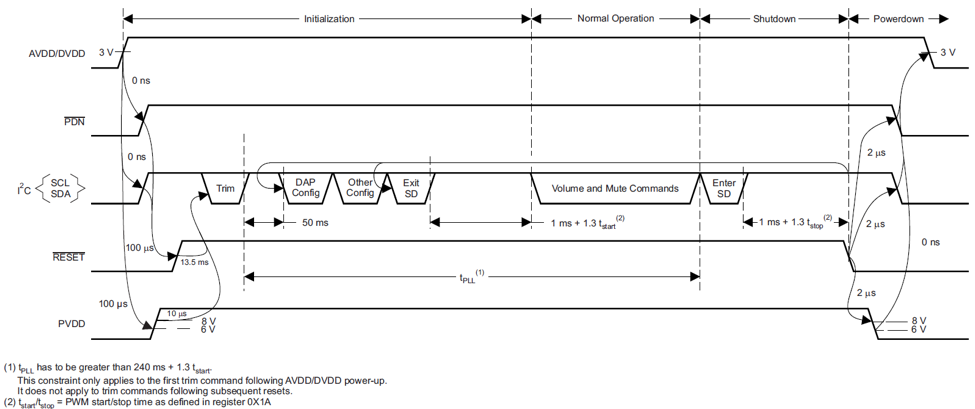

DAC时序分析

2021-07-29 09:14:26

想用dac7742y做一个高精度的锯齿波,可发现无波形输出。 按技术文档中的常规电路连接Vss:-15v,Vcc:+15v,Vdd:5v . 时序 按 技术文档来操作:比如说写时序:RW = 0

2019-02-25 08:37:50

的信噪比(DNR)和-120dB的THD N。ES9018S常被运用于旗舰级或高端的HiFi产品上,如WEISS、APOGEE等国外音响品牌,目前其他品牌的旗舰级音频播放器也大多数是选择该DAC芯片

2018-07-31 10:07:51

一,CS83711 两节锂电池7.4V供电内置升压2x16.5W双声道D类音频功放IC二,CS83785 单节锂电池3.7V供电内置升压2x10W双声道D类音频功放IC三,CS86189无滤波

2021-08-18 11:15:32

本人完全未接触过音频编解码,最近因为需要了解了一下音频编解码的芯片,其中均集成了ADC和DAC,想请教一下,音频编解码与ADC和DAC是什么关系?(我理解是:ADC是编码的基础,DAC是解码的基础,解码其实就是将数字量经DAC后生成了模拟量在经运放等恢复音频,不知对否?)

2014-08-07 15:22:30

请问能提供C6678上电芯片时序控制,以及配置端口电平和时序的Verilog代码吗?

2018-06-21 04:32:03

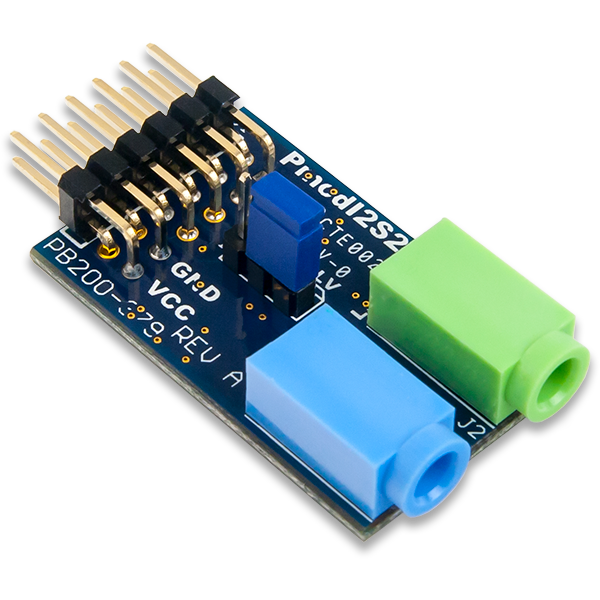

CS5343, CS5344 - 24 Bit 108k Samples per Second Analog to Digital Converter (ADC) Evaluation Board

2022-11-04 17:22:44

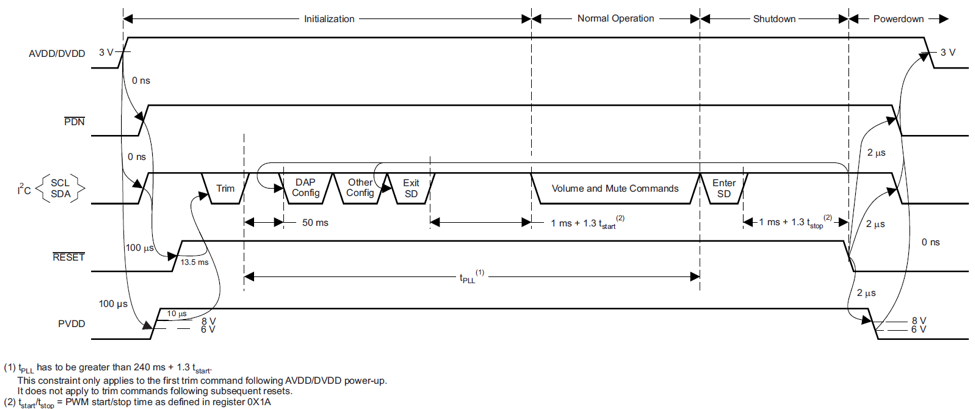

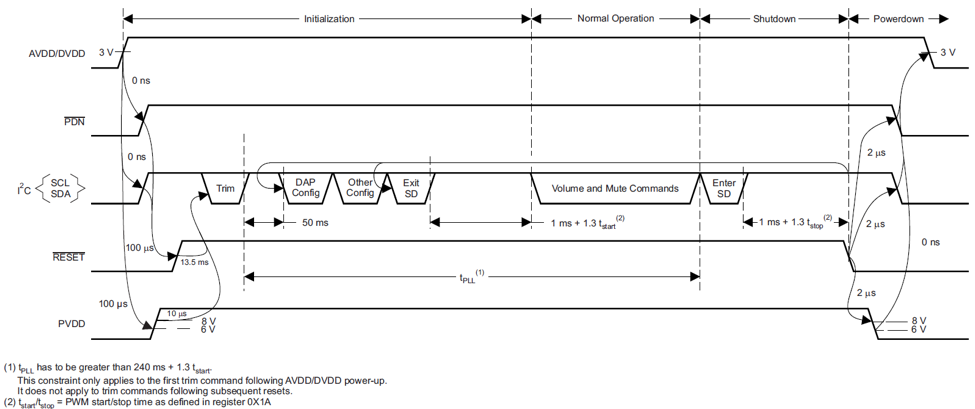

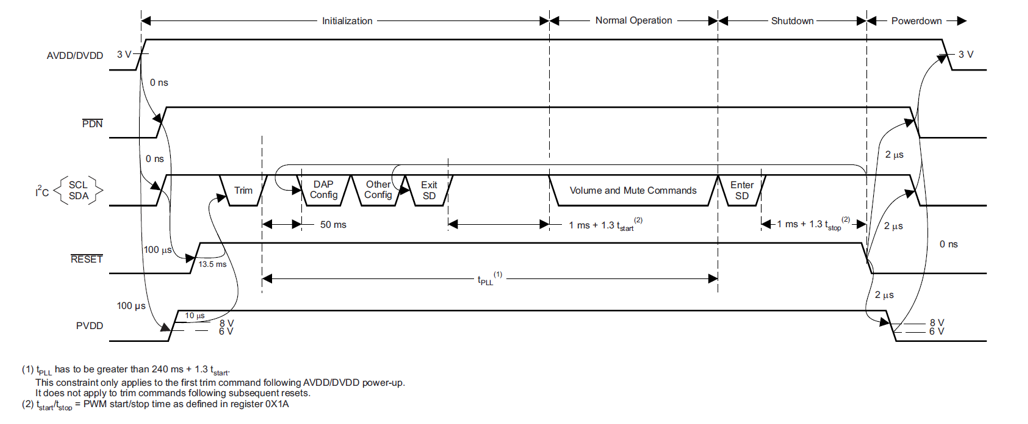

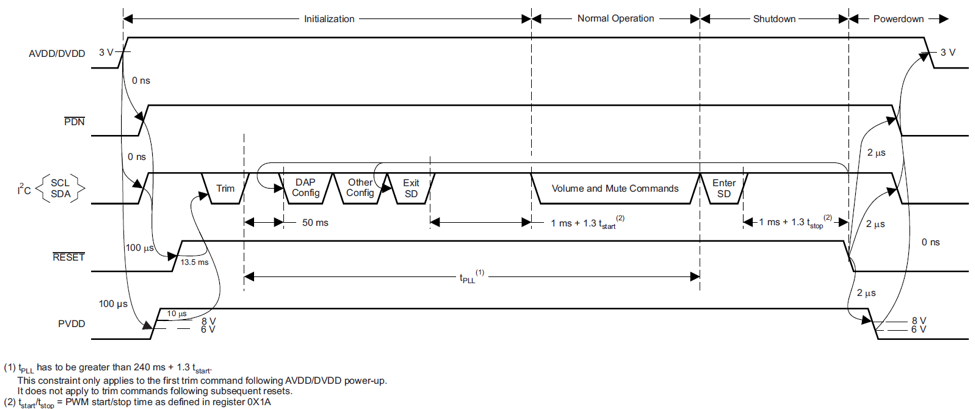

master 的I2S数据。CS5343是一款音频DAC,其通过I2S信号中的SDOUT的电平状态来确定主从模式。在CS5343和TAS5731M结合使用时,两颗芯片精确的上电时序控制是至关重要的,否则

2022-11-09 07:48:07

为什么有不同的上电时序

2023-11-02 08:13:09

1.目的HDMI RX接收到音频数据包(Audio packet),FPGA将得到的音频数据包解析并通过I2S协议发送给DAC芯片(CS4344),DAC芯片驱动后端功放以带动喇叭发出正确声音。2.

2022-01-20 07:27:09

如果要求输出是vdd=3.3v,我是不是可以这样设计上电顺序:首先设置Vgg=-2V,再VCtrl=1V,再Vdd=3.3V,然后调节Vgg,使Igg=140mA,那么它们之间的上电时序是如何控制的。

2023-11-22 07:14:57

上运载一个时钟频率 fPP 时,这个插入的卡必须要正确地复位(重置)。如果这个热插入特性是在主机内实现的,则该主机要经得起 VDD 和 VSS 之间短路而不损坏。上电时序如图:(SPI模式不支持CMD15,详见SD/MMC card 命令)

2012-01-12 11:06:39

I2S和AC97音频格式数据。 1.3 SSI的初始化 初始化SSI模块的正确顺序: ①上电或重启SSI(SSI_CR[SSI_EN]=0),即关闭SSI模块功能。 ②配置SSI模块。涉及的寄存器包括

2019-05-22 05:01:11

DAC是什么?STM32 DAC功能是如何实现输出音频波形的?

2021-11-15 07:18:19

电压信号,而 ADC把电压模拟信号转换成易于计算机存储、处理的数字编码,由计 算机处理完成后,再由 DAC输出电压模拟信号,该电压模拟信号常常用来驱动某些执行器 件,使人类易于感知。如音频信号的采集及还原就是这样一个过程。STM32具有片上 DAC外设,它的分辨率可配置为 8位或 12位的数字输入信

2022-01-06 08:16:08

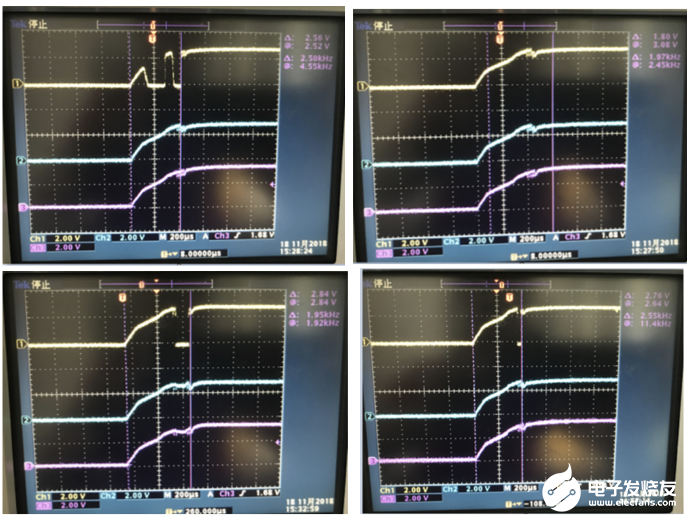

0-50ms,我特意测试了一下DEMO板上的5个电压上电时序,根据截图可见实际并非如手册上讲的那么严格,截图是两两比较的,前级为黄色,后级为红色。截图在附件似乎只要前面4个满足要求,0.9V都不是很重要,看

2018-05-25 04:36:15

的数字音频程序兼容。 集成电平转换器允许CS42406和其他在各种逻辑电平上运行的设备之间进行简单的接口。 高通滤波器可用于A/D的左右通道。这允许A/D消除不需要的直流偏移。 CS42406动态范围

2020-07-03 14:35:24

情况下的行为表现(参见表2),分析可能的问题及原因,并提出一些建议。上电时序问题多种多样上电时序问题可能出现于多种不同情况。例如,在一个客户应用中,AD8616配置为缓冲器,在电源建立之前输入为0 V(图

2018-05-09 16:32:40

有人用过cs4334音频dac吗?i2s都接上了,插耳机没声。。

2019-07-22 04:35:59

使用 DMA/PWM, DAC or I2S的Kinetis MCU上的音频输出

2022-12-08 07:18:30

目录程序目的展开设计SPI初始化DAC8563数据手册分析设定DAC值存在问题软件IO模拟正常硬件SPI向软件模拟IO靠拢尝试解决调整硬件SPI速率CS引脚不得常低调整CS引脚与MOSI引脚的时序

2021-08-11 07:44:38

本帖最后由 buhuile 于 2017-6-12 23:17 编辑

用安捷伦示波器测量上电时序或者掉电时序时,触发电平和时间怎么设置?时间设得不对,抓到的波形是不对的

2017-06-12 23:16:14

用安捷伦示波器测量上电时序或者掉电时序时,触发电平和时间怎么设置?时间设得不对,抓到的波形是不对的.

2017-06-17 14:41:18

单片机进行音频ADC DAC调试的方法是什么?单片机进行音频ADC DAC调试的工具是什么?

2021-11-15 06:08:46

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现以下情况,第一,上电

2019-10-18 07:53:02

音频二进制文件是怎样生成的?音频功率放大器TDA2030的原理是什么?如何去实现基于STM32的DAC音频输出呢?

2021-10-27 06:44:21

怎么实现基于STM32的DAC实现音频波形的输出?

2021-11-19 07:02:25

模拟时序控制器IC。它能控制和监视四个电压域。电压的上电和关断是通过控制相应电压转换器上的使能(开/关)引脚进行的。电压转换器的开启时间可以利用小电容产生的时间延迟来调整。各输出电压通过相应的监控引脚

2021-04-12 07:00:00

前段时间我发布了基于 ATmega 微控制器、RFM70 无线电模块和 CS5343 ADC 的电吉他无线系统:

在我看来,ESP8266可以用来代替发射器中的 ATmega88 和 RFM70

2023-05-24 08:51:58

现在的FPGA还严格要求上电时序吗?想请教一下大家

2017-09-26 15:39:07

上电过程 上电过程电源不是线性增加,而会出现电压降低的现象,如图所示,称为上电回沟。 这个问题觉得应该分两种情况分析: 1. 高速电路上信号线的回钩:反射,串扰,负载瞬变... 2. 电源电路上的回

2021-12-31 06:59:38

音频解码dac用多少位的?

2023-10-24 06:23:54

你好,AD7982的VREF与VDD/VIO之间是否有时序要求?手册里没查到。在目前我们的设计中,VREF(5V)先于VDD(2.5V)和VIO(2.5V)上电,不知是否会有问题。谢谢。

2019-01-08 13:56:41

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?为什么分析调制信号时波形对比度这么差呢?事实上,用户的每一次体验感,都是产品隐形的提升空间。以上这三个麻烦,现在也许有了

2018-12-03 11:17:59

的行为表现(参见表2),分析可能的问题及原因,并提出一些建议。上电时序问题多种多样上电时序问题可能出现于多种不同情况。例如,在一个客户应用中,AD8616配置为缓冲器,在电源建立之前输入为0 V(图1

2019-06-18 08:30:00

dac33音频芯片

2008-12-28 11:25:54 81

81 CS4923 CS4924 CS4925 CS4926 音频译码器系列用户指II

2009-05-13 10:09:51 24

24 CS4923 CS4924 CS4925 CS4926 音频译码器系列用户指南

2009-05-13 10:13:36 42

42 CS4926 CS4928音频译码器用户指南

2009-05-13 10:22:20 46

46 CS4923 CS4924 CS4925 CS4926 音频译码器系列用户指南

2009-05-15 15:19:07 8

8 CS4923 CS4924 CS4925 CS4926音频译码器系列用户指南II

2009-05-15 15:21:39 29

29 CS4926 CS4928音频译码器用户指南

2009-05-15 15:28:12 17

17 CS4923 CS49300 多通道数字音频译码器系列评估板

2009-05-15 15:54:16 40

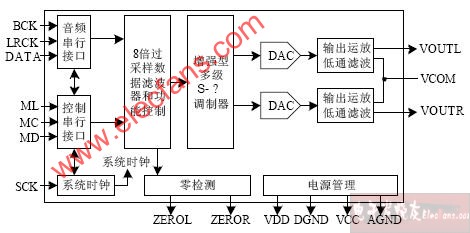

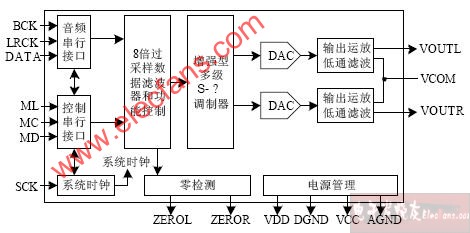

40 CS5343/4是用于数字音频系统的完整数模转换器。它执行采样、模数转换和抗混叠滤波,以串行形式为左输入和右输入生成24位值,每个通道的采样率高达108 kHz。CS5343/4使用三阶多位

2022-12-06 10:44:07

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 CS4334和CS8414是Crystal推出的DAC晶片和接收晶片.

2010-06-12 18:31:44 39

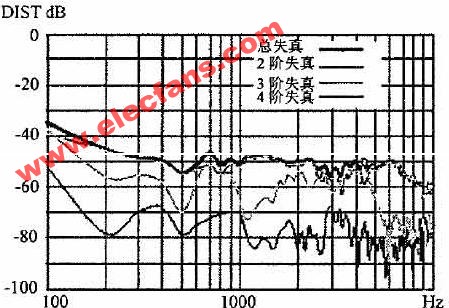

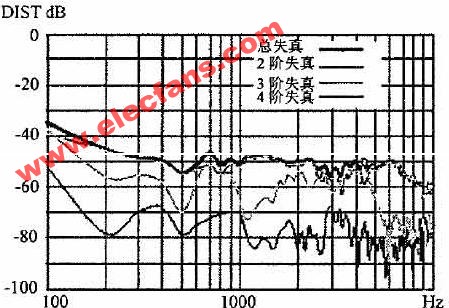

39 音频分析及音频分析仪简介

摘要:本文主要介绍了音频分析和音频分析仪的基础知识,从基本概念、音频分析方法、音频分析原理、音频

2008-11-27 09:32:59 5803

5803

音频DAC的工作原理

高分辨率音频DAC 大都采用多级幅度量化高阶Σ - Δ调制器结构。这样,在实际应用中可以提高音频动态范围,减小

2009-03-06 11:33:56 9249

9249

摘要:MAX9850音频DAC可以工作在较宽的主时钟频率范围,而具有不同的性能表现。通过选择不同的主时钟频率,设计人员可以在性能和简化设计之间做出平衡。本应用笔记分析不同主

2009-05-05 10:15:37 1865

1865

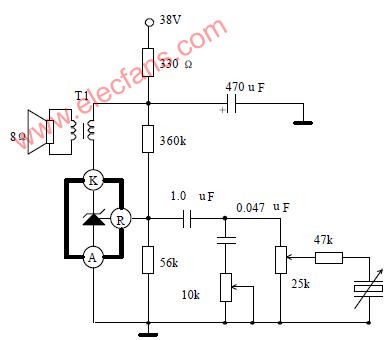

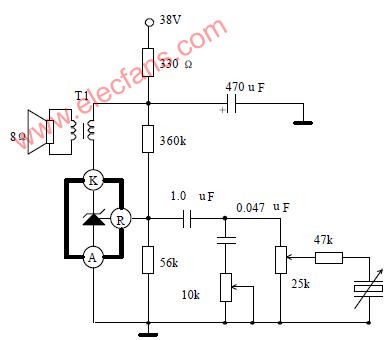

CW431CS音频放大应用线路

图6.6为用CW431CS 组成的400mW 唱机

2010-01-07 11:27:09 965

965

跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 CS7123芯片是深圳市芯海科技有限公司自主设计的高速/高精度视频DAC芯片,其内部包括三路10位电流导引(Current Steering)结构的DAC

2012-01-06 16:19:11 2385

2385

本文介绍了欧胜微电子公司最新一代音频数字-模拟转换器(DAC)的架构,专注于设计用于消费电子应用中提供高电压线驱动器输出的新器件系列。 基本原理 增量累加调制器通常用复杂

2012-07-06 11:07:54 977

977 本文介绍了欧胜微电子公司最新一代音频数字-模拟转换器(DAC)的架构,专注于设计用于消费电子应用中提供高电压线驱动器输出的新器件系列。

2012-09-29 13:43:42 1262

1262 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 CS4398的DAC原理图

2022-07-07 16:16:14 75

75 本文档的主要内容详细介绍的是CS4398 DAC音频解码器实用设计线路的电路图免费下载。

2018-10-18 08:00:00 250

250 时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

Digilent Pmod I2S2具有Cirrus CS5343多位音频A / D转换器和Cirrus CS4344立体声D / A转换器,每个转换器都连接到3.5mm音频插孔。 这些电路允许系统

2019-11-27 11:52:26 1631

1631

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 AD5343 Evaluation Software

2021-02-20 12:09:19 4

4 AD5332/AD5333/AD5342/AD5343:2.5V至5.5V,230A,并行接口双电压-输出8/10/12位DAC数据表

2021-04-22 18:32:30 4

4 UG-984:评估AD5343 12位双通道电压输出数模转换器(DAC)

2021-05-13 13:09:27 1

1 AD5343评估软件

2021-05-28 19:47:35 12

12 电子发烧友网为你提供ADI(ti)EVAL-AD5343相关产品参数、数据手册,更有EVAL-AD5343的引脚图、接线图、封装手册、中文资料、英文资料,EVAL-AD5343真值表,EVAL-AD5343管脚等资料,希望可以帮助到广大的电子工程师们。

2021-08-16 18:00:03

CS4398的DAC原理图.(普德新星电源技术有限公司怎么样)-CS4398的DAC原理图

2021-09-17 13:40:52 96

96 18位高精度音频Σ-ΔDAC设计(深圳核达中远通电源技术)-18位高精度音频Σ-ΔDAC设计

2021-09-18 17:21:40 12

12 。CS5343是一款音频DAC,其通过I2S信号中的SDOUT的电平状态来确定主从模式。在CS5343和TAS5731M结合使用时,两颗芯片精确的上电时序控制是至关重要的,否则会出现偶尔没有声音

2022-01-19 16:38:45 4085

4085

带音频输出的方案芯片,CS5213是一款HDMI to VGA转换器且结合了HDMI输入接口和模拟RGB DAC输出。带支持片上音频数模转换器,节省成本,优化电路板空间。嵌入式单片机基于工业标准8051

2021-11-16 16:42:36 1251

1251 CS5213资料CS5213方案CS5213规格书HDMI to VGA方案HDMI to VGA(带音频)

2022-03-04 10:47:43 16

16 Capstone CS5203 HDMI到VGA转换器结合了HDMI输入接口和模拟RGB DAC输出。通过支持和片上音频DAC,它节省了成本并优化了板空间。嵌入式MCU基于工业标准8051内核。

CS5203适用于多种细分市场和显示应用,例如

主板、桌面、dongle市场和对接系统。

2022-10-18 10:19:23 0

0 CS201电路原理图,CS201电路设计资料,CS201专业Type-C音频转换芯片,TYPEC耳机,typeC麦克风 typec拓展坞音频芯片。

2022-11-07 14:26:23 11

11 高性能音频数模转换器(DAC)传统上需要一个非常干净的采样主时钟(MCLK),以避免音频质量下降。时钟源通常直接来自晶体振荡器,其产生的抖动通常小于100ps。在某些系统中,音频过采样频率(通常是3.072MHz或2.8224MHz的倍数)不是晶体振荡器参考频率的方便部分。

2023-02-28 13:43:07 832

832

master 的I2S数据。CS5343是一款音频DAC,其通过I2S信号中的SDOUT的电平状态来确定主从模式。在CS5343和TAS5731M结合使用时,两颗芯片精确的上电时序控制是至关重要的,否则会出现偶尔没有声音的问题。具体分析如下。

2023-03-29 09:41:26 1658

1658

Capstone CS5213 HDMI到VGA转换器结合了HDMI输入接口和模拟RGB DAC输出。带支持片上音频数模转换器,节省成本,优化电路板空间。嵌入式单片机基于工业标准8051内核。

CS5213适用于多种市场和显示应用,如笔记本电脑、主板、台式机、转换和对接系统

2022-02-16 18:30:49 503

503

98 dB 的动态范围以及 -92 db 的总谐波失真 (THD) + N。唯一差异在于串行音频接口格式支持,CS5343 支持 I²S 格式,CS5344 支

2024-01-03 15:37:43 0

0 CS43198 音频数模转换器HIFICS43198 是下一代低功耗音频数模转换器 (DAC),可提供卓越的系统级音频性能,而不会缩短电池寿命。该IC最大程度降低了电路板空间要求,同时支持推动

2024-01-03 15:45:10 1

1

电子发烧友App

电子发烧友App

评论